AMD在其Athlon 64 X2双核台式机处理器中首次采用了其65nm工艺技术。该处理器包含9层铜金属、1层凸点下锃金属、低k金属间介电质层和绝缘硅(SOI)衬底,以及其它新增的移动特性。有趣的是,其65nm技术首次应用的初衷并非是增强前一代90nm Athlon的性能,而是降低其功耗。AMD声称,该公司已将其90nm版本2.6GHz处理器的热功耗从89W降至65W。

与其前几代CPU技术一脉相承,AMD在65nm节点继续沿袭其SOI策略,AMD强调了SOI能比块状硅(bulk silicon)在更高密度和更低功耗方面带来更多的好处。它是AMD的第三个SOI技术节点,并将使对SOI是否适用于大批量制造的持续怀疑走向沉寂。

的确,SOI也许很快就将迎来艳阳天。一系列迹象表明,除了SOI的传统支持者IBM、AMD和飞思卡尔之外,SOI将会得到更广阔的应用。这些迹象包括:ARM最近收购了法国一家基于SOI的标准核库及其它知识产权块供应商Soisic,以及新加坡的特许半导体也从IBM获得了90nm SOI技术的授权。AMD去年对无晶圆厂图形芯片制造商ATI的收购也许同样昭示着SOI也将最终进入图形处理器。

AMD仍采用部分耗尽的SOI晶体管设计,其中,门下部的耗尽区并不完全夹断(pinch off)硅衬底。在发生彻底夹断的薄衬底上完全耗尽的晶体管具有接近理想的阈下行为,从而显著降低阈下漏电流。但是,控制完全耗尽器件的阀值电压依然是个问题,使得其应用目前仍受到阻碍。

AMD工艺的最大创新在于其增加晶体管驱动能力的移动增强技术。所有主要的微处理器制造商在90nm节点都通过增加沟道应力来强化移动性,以防止对门长度和门氧化物物理上的进一步微缩。持续的微缩将把增加的漏电流和待机功耗增加至破坏性水平。

所以制造商为晶体管沟道的晶格增加应力,从而稍微改变了硅原子的原子间距,并导致增强的载流子活动性--PMOS场合是空穴,NMOS情况是电子。与相同门长度但未经应力化处理的晶体管相比,增加的载流子活动性生成更大的驱动电流,并带来更快的开关速度。所以,对门长度和门氧化物适度的缩微是实现下一代技术节点所要求的。另一种替代方案是不进行任何缩微,在保持性能水平的情况下可降低功耗。

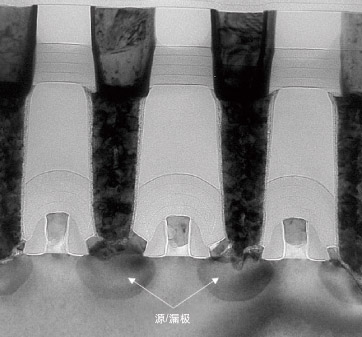

在90nm,有两种主要的增加应力的方法:源/漏区的硅锗外延层生长以及在完成的晶体管上带特定应力沉积的氮化物“应变层(stress liner)”。SiGe源/漏区用于PMOS晶体管,它从增加在沟道指向上的压缩应变中受益。硅锗(SiGe)具有比普通硅更大的晶格常数,从而SiGe层将压缩它们之间的沟道区。

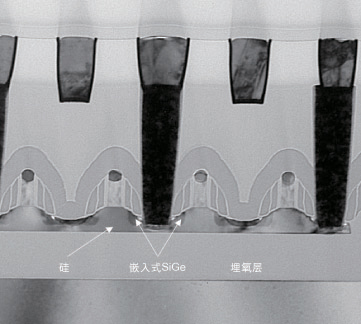

图1:AMD 65nm PMOS器件中的应变层和嵌入式SiGe层。

应变层与内置的应力一道沉积,该应力然后将被转移至沟道。可通过调制沉积参数来选择压力类型、应力或压缩力。可伸张的应变层改进了NMOS性能,该性能从沟道方向中的可伸张应力中获益,而应变层提升了PMOS性能。

双应变层技术

在90nm工艺,AMD仅利用了应变层技术。而在65nm,AMD采用了双应变层(DLC)技术。在PMOS器件上沉积一个压缩层,而在NMOS器件上沉积一个张力层。但在新的开发中,PMOS晶体管上的压力被SiGe层通过施以扭曲所增加。

因采用的是绝缘硅,AMD 65nm晶体管硅体的厚度仅为80nm。适用于块硅器件的传统SiGe源/漏技术与如此薄的硅层并不相容。SiGe层将有100nm伸展至块状硅。

AMD克服了这一限制,并用嵌入式SiGe增加PMOS沟道的压缩应力。嵌入式SiGe层有只约50nm厚,并充分扩展至镍硅化物接触层。AMD报告说,采用将应变层/嵌入式SiGe结合起来的方法,其在PMOS饱和电流方面有53%的改进,而NMOS性能则提升了32%。

图2:本TEM图像显示的是采用SiGe源/漏极的英特尔PMOS器件的横截面。

与90nm工艺一样,后期的收尾金属化工艺采用9层铜金属处理,它也许意味着更多金属层的效用业已饱和。的确如此,但尽管这样,它整合了显著改进的设计成用于缩短配线RC延迟的金属和电介质工艺。其最大的改进是将全部金属层从单蚀刻改为双蚀刻。此举消除了高k掺碳氧化物在沟道层的蚀刻阻留,降低了IMD的有效“k”值。其它的改变还有:用低k碳氮化硅取代了氮化物金属封顶层、更大范围内使用低k掺碳氧化物以及再次降低金属线的整体电容。

综上所述,这些改进一道创造了一个具竞争力、高性能的65nm工艺,并为AMD微处理器未来的业务前景做了很好铺垫。到2007年中期,AMD预期其位于德国德累斯顿的Fab 36将完全转向65nm。

作者:Edward Keyes

首席技术官

Semiconductor Insights公司