最近几年,用于高速数据互联的低电压差分信号(LVDS)[1]在消费电子、高速计算机外设和电信/网络以及无线基站中得到了广泛的应用。LVDS在性能、功耗、噪声、EMI消减以及成本方面具有明显的优势。通过恰当的设置,可以在10到15米长的双绞线上或者在超过1米的PCB印制线上,实现100Mbps到800Mbps的LVDS信号传输。负载为100欧姆的功耗仅仅为1.2mW,并且基本上与频率无关。

本应用说明将讨论LVDS故障防护功能,这对于正确的LVDS操作非常重要。我们将讨论三种故障防护电路,分析他们的特性,并对应用提出指导。

LVDS的基本参数和优点

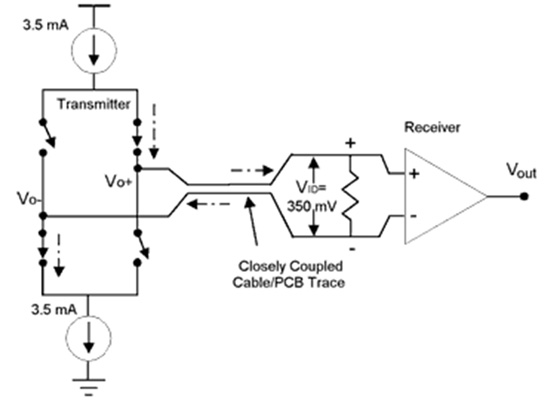

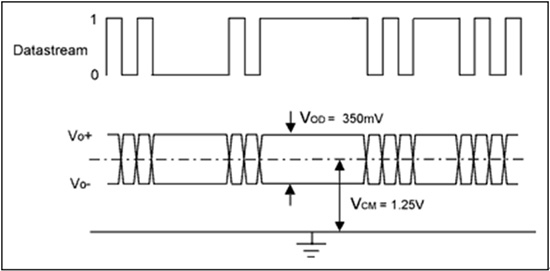

我们先简单地了解LVDS信号和电路配置的基本架构。图1显示了一个简单的、基本的LVDS传输与接收电路。接收器是一个比较器,其绝对转换门限电平为50mV。无论是电缆还是PCB印制线对,传输线都设计成100欧姆的差分阻抗。图2显示了在介质上的共模和差模信号电平。在图1和图2中,VID为LVDS接收器的输入差分电压,VOD为LVDS发送器的差分输出电压,VCM是共模电压。

用一个电流源连续驱动两个紧耦合的线缆或印制线,无论差分模式有怎样的变化,传输介质上的共模电流和电压都不会随时间而变化。一般来说,数字传送速度主要受限于负载上的寄生电容和电感。对于图1中显示的LVDS电路,大多数的负载电容对于驱动器(发送器)呈现为共模阻抗。另一方面,绝大部分电感来自芯片或负载管脚,而不是来自匹配的传输线。而且,寄生电感的值相对较小,对于信号完整性的影响可以忽略不计。由于负载上的共模电压没有变化,因此来自负载寄生电容的大部分影响被消除了。因此,LVDS可以比CMOS或TTL信号的数据速率高很多。

由于两根线缆或印制线相互非常近,因此只有共模影响EMI。在传输期间的共模变化可以忽略不计,意味着LVDS具有非常低的辐射电平,即使是很高的工作速率也是如此。而且,由于仅有350mV的低差分电压摆幅,100欧姆的终端电阻上只有1.2mW的恒定功耗,并与数据速率无关。与CMOS、TTL这样的单端信号所消耗的高功率相比,LVDS的低功耗是非常显著的。

图1:基本的LVDS Tx和Rx电路原理图。

图2:LVDS信号的共模和差模。

故障防护功能

大多数的LVDS接收器需要内部或外部的故障防护电路,这样当出现一个特殊的链路状况或发生故障时,接收器的输出将呈现一个已知的逻辑状态,通常为逻辑高电平。下面所列为需要启用故障防护功能的链路状况或故障。

• 输入开路:如果LVDS芯片具有多个接收器端口,未使用的接收器输入应该保持开路状态,输出应该是稳定的逻辑高电平。

• 输入悬浮:如果LVDS驱动器处于三态,驱动器处于断电状态,或者链路中断,LVDS必须具有一个稳定的逻辑高电平输出。

• 输入短路:如果两个并行的LVDS线或印制线被短接在一起,这将是一个错误的连接,需要保持逻辑高电平输出状态。

设计师还希望故障防护功能在噪声环境中能够性能稳定,并且对LVDS正常工作的影响可以忽略不计。

故障防护电路和性能分析

有三种基本的故障防护电路类型:外部偏置电路,路径中电路和并行电路。我们将介绍每种电路是如何工作的,然后分析它们各自的性能优势和劣势。

外部偏置故障防护电路

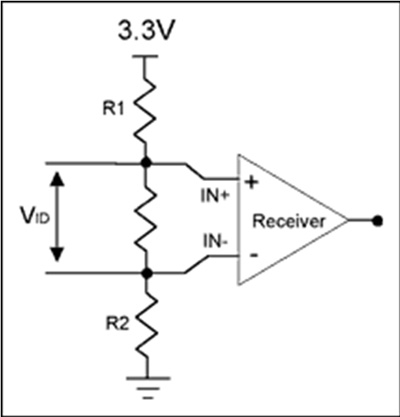

这种故障防护功能电路比较简单,由三个外部连接到接收器输入管脚的电阻组成(图3)。

图3:外部故障防护电路

在这种设计中,当线路未被驱动时,在两个输入管脚之间设置一个正的偏置电压,以便让接收器的输出处于逻辑高电平状态。根据下面的表述来设置VID偏置值。

电路的共模电压遵循下面的关系式:

例如,要在一根悬浮线的VID上获得50mV的偏置电压,我们可以选择R1 = 4170欧姆,R2 = 2450欧姆。如果我们假设噪声的幅度小于VID的偏置电压,那么接收器的输出将处于逻辑高电平。

这种故障防护电路广泛用于早期的LVDS接收器中。基于下面的原因这种电路曾经很受欢迎:

• 它提供了根据悬浮线上的噪声水平来外部设置偏置电压的灵活性。

• 它提供了一个共模返回路径以及一个ESD放电路径。

然而,这种设计的一些缺点限制了在当前LVDS应用中的使用。

• 对于单个LVDS链路来说,需要两个电阻或许不是什么负担,但是如果使用多个链路,特别是在多通道应用中,这个问题就值得考虑。

• 当前LVDS数据速率可以达到800Mbps,或者对于计算机外设和网络连接,甚至高达2Gbps。在这么高的数据传输速率下,因为VID偏置产生的非均衡的接收器门限电压可以导致相当大的占空比失真,并增加抖动。

• 对于差分噪声来说,它具有低的噪声余量,因为VID偏置不能被设置得过高。

• 这种电路对于输入短路故障来说是无效的。当被短路,VID偏置电压源也被短路,LVDS输出将呈不定状态。

路径中故障防护电路

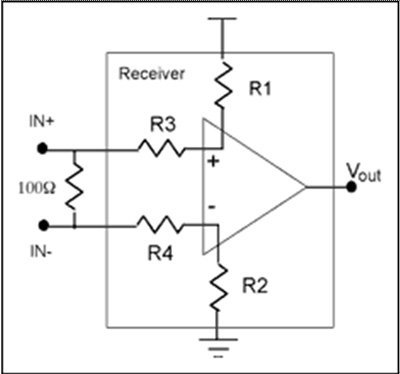

路径中故障防护设计类似于外部偏置故障防护方法,但是这里的R1和R2被集成到了LVDS接收器中,因此VID上的偏置现已是一个内置的电压源。该电路广泛应用在某些LVDS接收器中[2]。图4给出了一个等效电路。

图4:路径中故障防护电路框图。

采用路径中电路设计,选择R1和R2的电阻值使内部VID偏置电压值处于30mV到50mV之间。即使当输入短路也插入正的VID偏置,这使输出在上面三种需要故障防护保护的条件下都处于高电平。

这种路径中设计超越了外部偏置方法,因为它克服了后者的某些缺点。路径中故障防护电路:

• 取消了外部电阻

• 当输入短路时工作

尽管如此,对于某些应用来说,路径中故障防护方法依然具有较大的一些缺陷:

• 它不具有设置偏置电压的灵活性。

• 它导致不均衡的接收器门限,劣化占空比性能,并增加抖动。

• ‘路径中’噪声噪声余量的较低

并行故障防护电路

大多数美信(Maxim)的LVDS产品采用这种并行故障防护电路中[3],它克服了前面两种故障防护电路的主要缺点,如图5所示。

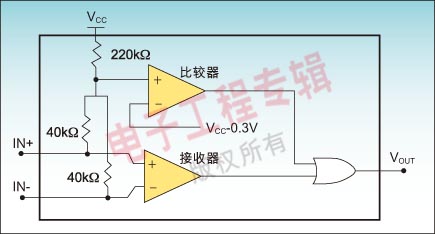

图5:并行故障防护电路的原理图。

在图5中,比较器监测电压轨的电压电平,并与VCC - 0.3V的参考电压比较。如果轨电压高于参考电压,其输出就处于逻辑高电平。然后,这种逻辑高电平阻止接收器的输出通过一个或门,故障防护功能被激活。这种配置可以在前面所列的这三种需要故障防护功能的情况下将LVDS输出拉到逻辑高电平:开路、浮置和短路。只要共模电压低于基准电压VCC - 0.3V,这种功能设计就能正确地实现。

这种并行故障防护方法相比于两种老的方法,提供了某些独特的优势:

• 对于共模和差模,它提供了非常高的噪声余量。

• 其配置是对称的,对占空比和输入差分信号的抖动没有影响。

尽管有这些独特的好处,但使用这种并行方法也存在顾虑。对于多点或长距离的点对点应用,共模负载电容可能会相对很大。当发生故障时,该电路需要一些时间来对共模电压电平进行充电,使其达到VCC - 0.3V。这个过程反过来又会对故障防护功能增加激活延时。

结论

本应用说明讨论了三种不同的故障防护电路的设计、操作、优势劣势,它们分别是外部偏置、路径中和并行电路。我们看到对于LVDS故障防护功能来说,还没有一个完美的解决方案。分析显示,并行方法比其它两种方法可以在更多的条件下获得更好的性能。

美信集成产品公司高级工程师