尽管半导体工艺多年以来一直在发展,制造对设计的影响还是可以通过采用简单的设计规则和基本的电子模型得到解决。制造与设计之间的沟通也比较容易。只要简单地遵循设计规则并用模型仿真,芯片良品率就能得到保证。

然而从90纳米节点开始,这种观念开始接受挑战。虽然传统设计规则对于45纳米设计的成功仍然很关键,但是它们被统计良品率模型所扩充,该模型远远超出了简单的通过/失败检验范畴。该方法包括以下技术:临界特性分析、临界区域分析、LFD(光刻工艺友好的设计)和高级仿真,所有这些技术都在一个基础架构中使用,该架构能处理不同技术间的交互,全面提高设计质量。通过结合所有这些技术,设计人员能够得到对于设计质量的全面描述,并且这种描述建立在目前最先进的基于规则和基于模型分析的基础之上。

在更先进的工艺条件下,经验证为“无设计规则检查错误”的设计仍会导致良品率低下甚至芯片功能失效的情况出现。为什么呢?即使芯片内部或芯片本身的某个特殊设计组件或结构能实际制造出来,但在特定的全芯片版图中,同样的可制造组件会显著增加失败的概率。例如,目前许多设计都是自动生成的,并且要满足最小的宽度和间距等最小设计约束。这样做被认为有助于保持整个设计尺寸尽可能小。虽然一个最小规格的特殊布局也许能被制造出来,但是如果这种情况过多的话也会显著地增加这种芯片失败的概率。

下面的一项技术可以从宽度、间距和密度的角度分析布局,预测哪里最容易出现问题,并确定与每个因素相关的风险大小。正确的分析需要综合报告和可视化结果,以帮助设计人员查出最重要的问题,或驱动增强工具做出正确的改动。

制造水平决定了设计和硅片之间的交互所需的良品率模型和信息。设计人员如何使用这些模型直接影响良品率。困难在于制造过程的每一步对于良品率的影响都不同,因此需要一个系统来应对临界区域和光刻等已知的挑战以及所知甚少的阻抗和蚀刻因素。

同时支持规则和模型的通用几何处理引擎对于鉴别限制良品率的结构来说是很重要的。这可能包括了描述被推荐规则的缺陷率变化或粒子短路和开路的缺陷密度分布数学模型。这些信息被发布在支持被推荐规则和临界区域分析的工艺文件中。

被推荐规则分析可确定临界特征,其决定了所有良品率下降的根源:随机、系统以及参数因素带来的影响。除随机粒子以外,这些因素都可以解决阻抗和蚀刻对良品率的影响。

更先进的临界区域分析可以确定版图中某一类型和尺寸的粒子将造成短路和开路的设计区域。由于数据超过负荷是DFM的障碍之一,因此对临界特性分析技术的基本要求是使筛选数据的过程自动化。基于这种分析,设计师可以确定最坏影响检查的最坏区域,并在该区域内运用drill-down方法统计性加权个别出现的问题,以进一步区分临界特性的优先次序。通过各种报告和可视化结果,设计小组可以确定最影响其产品良品率的设计原则或自动设计工具行为,帮助他们针对良品率、面积和性能等各方面因素做出明智的折衷。

光刻友好的设计(LFD)

采用LFD技术,版图设计人员能预测工艺变化对某特定芯片的可印性的影响,并使提高鲁棒性的设计成为可能,从而大大降低芯片对工艺窗口变化的敏感程度。

搜集在可能的dose/focus条件下,而不仅仅是在最佳设置范围下关于设计如何印制的数据,

一个LFD的设计检查要完成三项重要任务:

1.在可能的dose/focus条件下、而不仅仅是在最佳设置范围内搜集设计如何印刷的数据;

2.特殊的缺陷或潜在的良品率抑制因素;

3.为设计的每一部分分配一个“可制造性记号”以反映在特定的工艺窗口下该部分可制造性的良好程度。

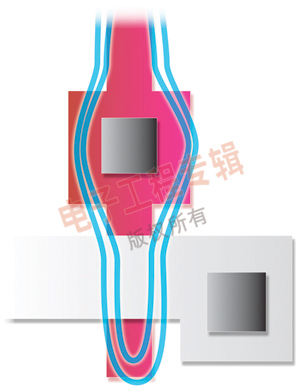

图2:多晶栅上的PV band特写:灰色表示有源层,红色表示多晶层,蓝色表示多晶层的PV band。

版图数据及其对制造变化的可能响应通过整合工艺变化段(PV band)的先进工艺汇聚在一起。PV band是显示印制如何响应工艺变化的几何区域。在这一区域中随工艺条件发生变化时就会印刷一个特征。创建PV band所用的方法是通过在不同工艺条件下计算硅片印制图形并将结果图形进行组合。PV band以不同方式预测了良品率故障,包括4种最常见的故障结构:挤压、桥接、重叠和临界尺寸可变性。这种结构的预测结果再被汇集到LFD规则中。在设计过程中设计人员正是使用这些LFD规则来分析标记的区域。

从制造、时序和电源角度看,LFD故障规则识别工艺变化时印制电路变化的区域,其可能会引起临界误差。典型的设计规则违反可通过边界移动或形态改变(切割拐角)得到修复。

高级仿真

现在已经知道一些DFM工具能够直接影响45纳米工艺节点的时序分析。其中有的在工艺窗口内仿真光刻和蚀刻效果,添加通孔以减少随机缺陷,改变线路路径以平衡金属密度以及使用CMP模型以便更好地预测阻抗和电容值。

光刻和蚀刻仿真器目前能基于制造参数提取晶体管参量。它们也能用于高亮显示印刷图像与绘制图像相差过大的设计区域。

这样就赋予了设计人员调整设计的能力,因此在可预测性工艺窗口范围内的设计具有鲁棒性。它也允许高级设计人员有机会创建独立的设计。这对于设计团队理解设计来说至关重要,特别是在小型模块级别。它遵循与130纳米工艺中密度学习相同的方法:设计流程中的问题越早得到平抑,设计的最终阶段就能越快完成。

DFM的晶体管和通孔版图应该遵循时序收敛中使用的层次方法。这样,在全芯片级重新验证时只需要做很少的工作。试验与库设计表明在65纳米版图中,这种情况是可能的。更多的想法仍不断涌现出来。为了满足130纳米设计过程中出现的密度需求,新的DFM工具会找到创新的实现方式以做出更好的、更具鲁棒性的设计,并且不会破坏选路和时序收敛流程。

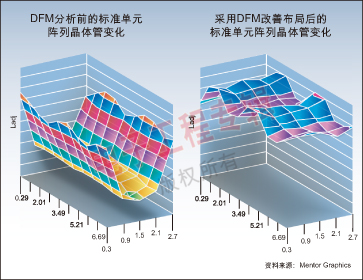

图3:DFM工具能改善交叉模块栅变化

在对于不同DFM技术的讨论中尚不明确的可能是这样一个事实:在期望最终产生最高良品率的硅片的情况下,这些技术不能彼此独立完成。

例如,临界区域分析可能认为通过增加某些金属线的宽度,对某一尺寸的粒子设计会变得更有弹性,并且“开放型”缺陷会显著减少。同样加宽金属线的方法在设计运行高级仿真分析时可能导致较大的性能损失。进行“修复”可能改进临界特性,但从光刻的角度看也许不利于可印性,反之亦然。实际上,一个用来评估良品率影响的最优化解决方案应该是基于所有DFM技术的折衷。

基础架构需要在不同技术之间权衡后决定一个最佳方法,并且这种方法中的实际软件应考虑到其它DFM问题带来的影响。这种想法可以为设计和分析流程创建全面的DFM分析方法。

随着DFM所面临挑战的增加,该行业发现自身需要额外的技术支持。这种情况与验证系统级芯片设计的时序相似:在不同的提取级别存在数字部分和模拟部分。然而,要验证它们能否在一起工作需要一个模式混合的多级仿真环境。这就需要设计师识别所需的分析类型并提供一个允许其一起工作的系统。在良品率方面,基于规则和基于模型的方法同时存在,针对每种具体情况可以由分析软件来决定哪种方法工作得最好。

作者:

Jeff Wilson

产品行销工程师

Mentor Graphics

jeff_wilson@mentor.com