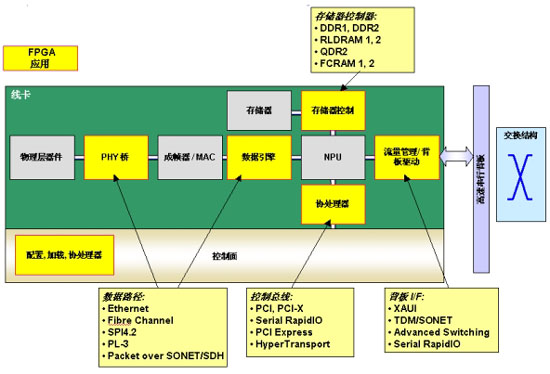

如今的FPGA不再是只用I/O实现简单的桥接,支持信号的完整性和满足时钟要求,而是要求FPGA能支持一些用于链路层的协议,用于简化实现不同的高速并行和串行标准。把这些标准化的特性集成到FPGA之中,可以大大缩短设计时间。90纳米的FPGA代表了第8或者第9代FPGA,这些器件从过去大量的查找表形式转变成复杂的SoC。高性能的FPGA能够满足通信网络系统的需要。图1展示了FPGA在线卡上的应用。这也是FPGA用于主要工业中的基本功能,包括通信、数据通信和存储技术。从图1中可以看到需要FPGA支持的各种接口和标准。

LatticeSC FPGA采用富士通的90纳米CMOS工艺技术,并用300毫米晶圆制造,能够加速芯片至芯片、芯片至存储器、高速串行、背板及网络数据通道的连通性。本文主要介绍LatticeSC FPGA的特性、结构和应用。LatticeSC器件被设计成针对高性能基于协议的连通性的结构,器件支持多协议,以及所有的高性能存储器标准。

器件的结构

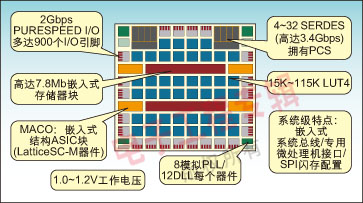

器件中集成了支持3.4Gbps数据率的高信道数的SERDES模块、提供业界领先的2Gbps速度的PURESPEED并行I/O、创新的时钟管理结构、以500MHz频率工作的FPGA逻辑、密集的RAM块,以及莱迪思特有的针对成本优化(MACO)的嵌入式结构化ASIC模块的掩膜式阵列。图2为器件的结构。

虽然结构化ASIC缺乏FPGA的灵活性,但由于其密度和性能,它们变得越来越流行。与全定制或者标准单元的ASIC不同,结构化ASIC设计成本要低得多,因为它们只将一小部分掩膜用作定制。莱迪思在每一片LatticeSC FPGA中嵌入了多达12个结构化ASIC模块,称为MACO模块。每个MACO模块大约有5万个ASIC门可用来实现需要最高性能、最小硅片面积和最低功耗的IP核。MACO模块还提供充足的至I/O引脚的布线连接、RAM块及可编程逻辑块。

LatticeSC器件提供1~7.8兆位、能够以500MHz频率工作的嵌入式RAM块(EBR)。每个18Kb的sysMEM EBR块可以实现单口、双口、伪双口或者FIFO存储器。专用的FIFO支持逻辑使得LatticeSC器件能够有效地实现FIFO而无需耗费LUT或布线资源来产生标志位。器件还集成了具有层次结构的时钟资源。与其它器件不同,LatticeSC FPGA既有PLL又有DLL资源,为时钟管理问题提供了“无折衷”的解决方案。

除了SERDES,LatticeSC PURESPEED I/O支持许多差分和单端I/O标准,包括LVTTL、LVCMOS、SSTL、HSTL、GTL+、LVDS、LVPECL和HyperTransport。但这还不够,如今的高速接口要求基于位的补偿,这是由于要保持适当的建立和保持时间裕度,以便缩短时钟周期时间。对于高速并行协议SPI4.2,这个问题尤为突出,动态位对齐和字对齐是系统解决方案的关键因素。通过提供完整的、灵活的和验证的I/O系统,PURESPEED技术提供专用的I/O逻辑块来简化这个过程。作为一个系统,PURESPEED块解决了嵌入式电路实现系统级连通性的挑战,而无需使用任何定制的逻辑资源。

提供完整的物理层解决方案

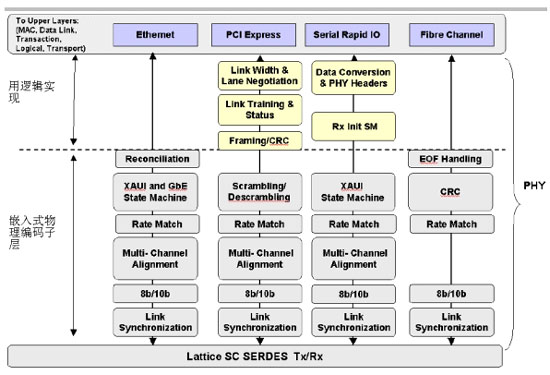

LatticeSC内含嵌入式物理编码子层(PCS)模块。这些预制的模块使用了ASIC技术,大大缩短了设计时间,提高了FPGA门的使用率,降低了成本和功耗。器件的SERDES/PCS逻辑可以配置成支持许多工业标准的高速数据传送协议。每个通道的SERDES/PCS逻辑拥有专门的发送和接收SERDES,用于传送高速全双工串行数据,速率可达3.4Gbps。物理编码子层支持如下的数据协议:

1. SONET/SDH

2. Gigabit Ethernet

3. 10 Gigabit Ethernet XAUI

4. 1.02或2.04Gbps Fibre Channel

5. Serial RapidIO

此外基于协议的逻辑可以在一些配置中全部或部分旁路,使用户能灵活地设计高速数据接口。图3为物理编码子层支持的Ethernet、Fibre Channel、PCI Express和RapidIO。几年前,SONET/SDH被认为是成熟的技术,会让位给全光或以太网传输技术。事实上,由于其过去的记录、稳健的可靠性和普及性,SONET/SDH仍然是可靠的传输技术。GFP、VCAT和LCAS增强了SONET/SDH的性能,使其能够支持多种协议,减少了推广应用成本。

存储器

为了支持高达10Gbps或者更高的速度,LatticeSC含有较大的存储器块,另外还有专门的电路用来支持标准的片外存储器。器件有3个层次的存储器可供使用:

1. 片内存储器:所有可编程功能单元可以配置成RAM或者ROM。用户可以使用基本功能块来构成小的FIFO,用于本地时钟域的传送。

2. 嵌入式RAM块:器件内有专用的RAM块阵列。用来支持包缓冲、大的灵活的缓冲器以及构建前后相关的查找表存储器。嵌入式RAM块总的容量为7.8Mb。

3. 外部存储器接口:有些应用需要较大的存储器,例如支持大量的包传送、用于流量管理的缓冲,以及远距离传送,sysIO块对已有的和新兴的存储器预制了专门的接口。用户可以选择各种各样的标准接口,诸如DDR1/2、RLDRAM1/2或QDR1/2。在I/O逻辑块中有DDR电路,并伴有输入延时和专用DQS检测电路以支持存储器接口,每个引脚的的带宽可超过800Mbps。

应用实例

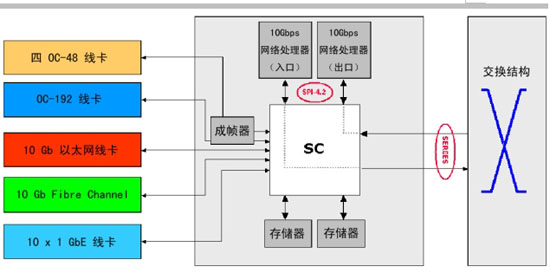

图4为FPGA在当今多种服务环境中所扮演的连通性角色。

从图中可以看到单片LatticeSC器件能够支持多个数据流。LatticeSC器件利用嵌入在结构化ASIC模块中的多个SPI4.2核,无缝地实现与10Gbps网络处理器的接口。要缓冲这些更快的线速,需要高速存储器接口。LatticeSC支持所有最新的存储器标准。具有32个SERDES通道的器件支持许多串行背板标准,诸如SRIO、PCI Express、Ethernet、Fibre Channel和SONET/SDH。

由上可知LatticeSC是如何来应对连通性的挑战。在电气方面,器件具有广泛的接口标准,能够支持最新的存储器、网络处理器、DSP和交换结构。为了满足高速串行设计,器件在发送端有预加重,而在接收端具有均衡性以改善信号完整性。高性能专用PLL能够迅速地从串行流中提取时钟。器件的物理编码子层支持多种主要协议。

作者:陈恒

上海莱迪思半导体公司