OPTION_5:HP

如果你是少数仍认为指令集架构(instruction set architectures,ISA)是精简(RISC) 或复杂(CISC),会对应用处理器之设计的功耗或性能有显著影响的软件或硬件工程师,放弃这种想法吧!它是不正确的,因为更重要的是处理器的微架构 (microarchitecture),也就是指令被硬布线(hardwired)到处理器中的方法,以及有什么被添加入以协助它们达成特定目标。

以上结论来自于学术期刊《ACM计算器系统学报(ACM Transactions on Computer Systems)》的一篇论文“指令集架构之战:了解ISA是CISC或RISC的关联性(ISA Wars: Understanding the Relevance of ISA being CISC or RISC)”(参考连结), 作者为Emily Blem、Jakrishnan Menon、Thiruvengadam Vijayaraghavan以及 Karthhikeyan Sankaralingam;该论文报告了过去四年美国威斯康辛大学(University of Wisconsin)垂直研究小组(Vertical Research Group,VRG)所做的一项研究结果。

报告作者之一Vijayaraghavan 表示,该研究是到目前为止针对三大处理器架构──英特尔(Intel) x86架构、ARM处理器以及现属于Imagination 的MIPS处理器──的设计、实作等所有角度的最完整分析。“虽然在过去,RISC与CISC指令集架构也许有一些差异,但我们锁定的参数──性能 (performance)、功耗(power)与能源效益(energy)现在肯定没有。”另一位报告作者Sankaralingam 表示:“ISA缺乏的地方,微架构就会补强它,反之亦然。”

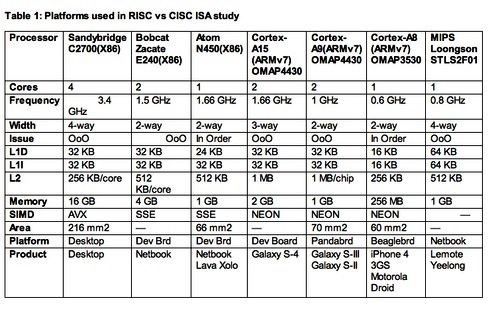

RISC、CISC指令集架构研究所采用的处理器平台

Sankaralingam 指出,现在只有一种处理器是真正的RISC架构──MIPS,是以美国斯坦福大学开发的RISC架构为基础;至于x86处理器架构一开始是纯CISC设 计,但过去几年来越来越朝类RISC结构发展。ARM处理器架构近似RISC,但采用更多CISC功能,包括增加的Thumb 1与Thumb 2指令集架构。

他表示:“所以我们的研究基本上是在目前的市场环境,比较今日的Intel、ARM与MIPS处理器;几乎每 一个我们的量测结果,都与指令集架构无关。”以往的比较研究会因为处理器系统的软件与硬件资源不同而有缺陷,但VRG团队尽力确保其量测是在条件几乎相同的平台与同等的环境中完成,为了区分出实作与ISA效果,他们尽可能让所使用的各种ISA芯片,都具备类似的微架构。

此研究将比较样本局限在ARM Cortex-A8或更高等级的处理器,较不注重Cortex-M系列组件;Sankaralingam解释:“原因很简单,我们的目标之一是要有能比较与量化的平台,因此我们没必要去看A9以下的处理器,以及相对应的竞争架构。”在Cortex-M0的环境下,ARM是与1~20MHz与 2~50mWatt的8位MCU竞争,其运作是架高在x86指令集之上,不适用其研究。

本文下一页:以龙芯(MIPS)、三个ARM平台和三个x86平台来评估

{pagination}

该研究小组的评估,是以一颗MIPS 处理器(中国开发的龙芯- Loongson处理器)、三个ARM平台(Cortex- A8、Cortex-A9与Cortex-A15),以及三个x86架构设计(Atom、Bobcat与Sandybridge i7)来进行;他们也使用了相同的操作系统──Linux 2.6 LTS,还有以gss 4.4为基础的交叉编译程序前端(cross compiler front end)。

在移动设备客户端的工作负载方面,他们使用CoreMark与Webkit性能基准;在桌面应用方面,则是采用SPECCPU2006基准。至于服务器工作负载的性能基准,则是使用包括lightpd与CLucerne等性能基准。

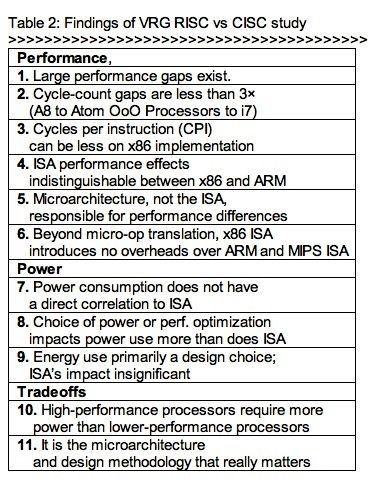

RISC、CISC指令集架构研究的发现

研究所采用的实作样本,包括不同ISA以及相同ISA、不同微架构;Sankaralingam表示:“整体看来,我们选择的平台条件具备合理的平等,而且我们执行了详细的分析,分别得出各微架构与技术的效果。”

VRG 团队确实进行了处理器在运行时间(execution time)、工作周期(cycle count)、指令数目(instruction count)、指令格式与结构(instruction format and mix)、微架构以及ISA对微架构影响的比较;功耗与能源效益的分析量测也很全面,包括平均功耗、平均技术独立功耗(technology independent power),以及平均能源效益等等。

Sankaralingam表示,他们的报告结论是,虽然 ISA与支持不同特殊应用(例如虚拟化、加速器、浮点运算..)的功耗与性能有关,但无论ISA是RISC或CISC,其实大都与今日成熟的微处理器设计领域没有什么关系。“根据这项研究,研发工程师能简单根据工程设计观点,放心考虑针对不同性能等级优化的ARM、MIPS或x86处理器;” Sankaralingam指出:“不同ISA的能源效益基本上并没有差别。”

如该报告最后一段所写:“显然数十年来的硬件与编译程序研发,已经能有效掌握RISC与CISC架构,而且两者在未来要求节能的创新应用中拥有平等地位。”

编译:Judith Cheng

本文授权编译自EE Times,版权所有,谢绝转载