近几年来,由于电子产品设计的Core电压越来越低,而电流却变得越来越大,从30A到100A不等,使得电源完整性(Power Integrity, 即PI)越来越受到大家的关注。4月19日,由《电子工程专辑》精心打造的电子设计群体的高端交流聚会—技术分享沙龙在深圳国际商会中心33楼成功举办。在此次聚会中,工程师吴均(Bruce Wu)和周红伟带来了“从同步开关噪声来优化电源设计”的技术分享。(从同步开关噪声来优化电源设计(视频))

在分享会上吴均表示,PI这个话题其实很早就在业界讨论了,只是当时很多大公司都普遍认为PI最多只是帮助节省几个不怎么值钱的电容而已,所以一直没怎么受到重视。而现在由于Core电压降到了1V以下,电源的波动对系统的影响就会变得越来越大;加上电流的增大,像33A、50A、或者80A这样的大的电流在PCB板上跑的时候,载流通道是否足够,电源的波动能不能满足系统需求等问题就变得越来越严重了。因此,PDN(电源供电网络),PI设计这几年越来越受到大家的关注和重视。(相关博客:当电源和DDR成为硬件设计最头痛的问题)

图1:吴均在技术分享沙龙上分享心得。

【分页导航】

| • 第1页:PI重视不够 Core电压降到1V发生改变 | • 第2页:电源设计和DDR设计 让人头痛的问题 |

| • 第3页:四个方面去考虑 SSN方面降低电源噪声 | • 第4页:退耦电容仿真图形结果引发的猜想 |

| • 第5页:退耦电容双方面作用 为什么 | • 第6页:案例分析退耦电容是如何影响SSN的 |

| • 第7页:目标阻抗的角度 选择退耦电容方法 | • 第8页: SSN与平面耦合 要尽量避免什么 |

| •第9页: 吴均谈噪声和纹波的区别 | |

{pagination}

在吴均看来,目前做硬件设计中遇到的两个比较让人头痛的问题是电源设计和DDR设计。因为不管是从仿真角度,还是从测试角度来看,电源设计都不好做。他首先抛出了几个问题,在电子产品设计的电流越来越大时,应该怎么设计PDN,怎么合理配置和摆放电容。PDN阻抗分析与优化电容的时候,怎么设定目标阻抗?分析到多高的频率?怎么确保优化方案是正确的?SSN的仿真怎么才能够做到准确?电源纹波和噪声该怎么测量?两者之间有什么区别和联系?

针对这些问题,跟吴均一起来到沙龙现场的周红伟分享了主题为《从同步开关噪声来优化电源设计》的技术分享。在分享中,他首先从电源噪声的原理说起,再到退耦电容与SSN(同步开关噪声)关系,最后总结出该如何做好电源设计的优化工作。

图2:周红伟在分享《从同步开关噪声来优化电源设计》。

【分页导航】

| • 第1页:PI重视不够 Core电压降到1V发生改变 | • 第2页:电源设计和DDR设计 让人头痛的问题 |

| • 第3页:四个方面去考虑 SSN方面降低电源噪声 | • 第4页:退耦电容仿真图形结果引发的猜想 |

| • 第5页:退耦电容双方面作用 为什么 | • 第6页:案例分析退耦电容是如何影响SSN的 |

| • 第7页:目标阻抗的角度 选择退耦电容方法 | • 第8页: SSN与平面耦合 要尽量避免什么 |

| •第9页: 吴均谈噪声和纹波的区别 | |

{pagination}

在我们设计好一个电源,打板、制作好之后,需要将整板拿去测量。而在用示波器测量的时候,我们通常都会发现我们设计的电源存在很大的噪声。这个时候,我们就需要考虑,到底是什么原因造成了电源噪声过大,该怎么办?周红伟觉得,这时我们应该从四个方面去考虑,比如我加的电容数量足够吗?电容种类够不够?电容放置的位置是否正确?电源地耦合吗?

他解释说,电源系统的噪声来源是多方面的。首先,稳压电源芯片本身的输出并不是恒定的,会有一定的纹波。这个是由稳压芯片自身决定的,一旦选好了稳压电源芯片,这个噪声我们就无法控制,只能接受。其次,稳压电源无法实时响应负载对于电流需求的快速变化,这就会造成SSN(Simultaneous Switch Noise,同步开关噪声)。这时因为当器件处于开关状态,产生瞬间变化的电流,在经过回流途径存在电感时,形成交流压降,从而引起噪声,所以也称为Δi噪声。SSN是电源噪声的一个重要组成部分。另外,负载瞬态电流在电源路径阻抗和地路阻抗上产生的压降。PCB板上任何电气路径都不可避免的会存在阻抗,不论是完整的电源平面还是电源引线。当然还有诸如边缘效应,平面谐振等方面的原因。这里主要从SSN方面看,来怎么降低电源噪声。

这样的话,就需要考虑影响SSN的因素有哪些?周红伟指出,影响SSN的因素有开关速度(信号的速率)、驱动的多少(信号数量N)和回路电感Loop,因此SSN量化计算的公式可表示为:

Vssn=N ×Lloop×Δi

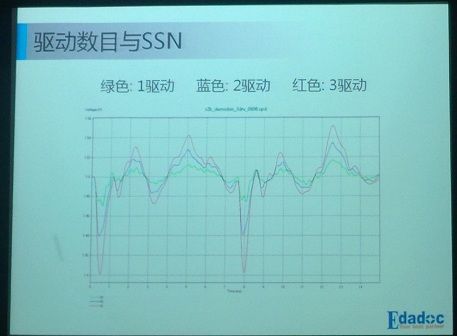

图3:驱动数目与SSN。

从图3的仿真波形可以看出,驱动的数目越多,Vssn就越大,这也验证了上面公式的正确性。

因此,SSN抑制方法有:1,从源头上减少SSN的产生(驱动能力的选择);2,添加退耦电容组合(退耦电容);3,采用嵌入式退耦电容(埋容);4,电源地平面分割(平面耦合)。

【分页导航】

| • 第1页:PI重视不够 Core电压降到1V发生改变 | • 第2页:电源设计和DDR设计 让人头痛的问题 |

| • 第3页:四个方面去考虑 SSN方面降低电源噪声 | • 第4页:退耦电容仿真图形结果引发的猜想 |

| • 第5页:退耦电容双方面作用 为什么 | • 第6页:案例分析退耦电容是如何影响SSN的 |

| • 第7页:目标阻抗的角度 选择退耦电容方法 | • 第8页: SSN与平面耦合 要尽量避免什么 |

| •第9页: 吴均谈噪声和纹波的区别 | |

{pagination}

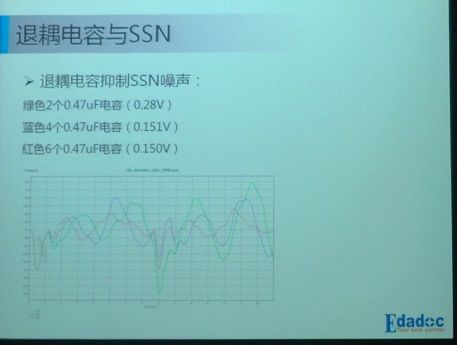

采用退耦电容是解决电源噪声问题的主要方法。这种方法对提高瞬态电流的响应速度,降低电源分配系统的阻抗都非常有效。

从图4的仿真图形可以看出,分别采用2个、4个和6个电容的三种方案中,噪声的幅值是依次降低的,但也可以看到,从4个到6个,噪声幅值的降低很不明显。这就说明同一种电容2个和加4个有区别,而加6个时效果不明显,可以说后面多加的这2个是多余的,可以不需要。为什么会出现这种情况呢?

图4:退耦电容与SSN。

【分页导航】

| • 第1页:PI重视不够 Core电压降到1V发生改变 | • 第2页:电源设计和DDR设计 让人头痛的问题 |

| • 第3页:四个方面去考虑 SSN方面降低电源噪声 | • 第4页:退耦电容仿真图形结果引发的猜想 |

| • 第5页:退耦电容双方面作用 为什么 | • 第6页:案例分析退耦电容是如何影响SSN的 |

| • 第7页:目标阻抗的角度 选择退耦电容方法 | • 第8页: SSN与平面耦合 要尽量避免什么 |

| •第9页: 吴均谈噪声和纹波的区别 | |

{pagination}

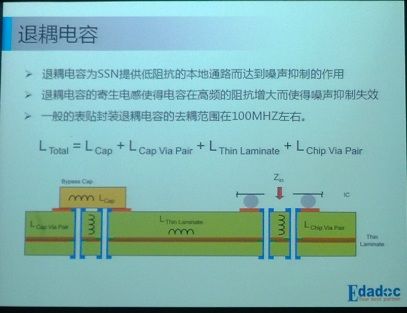

退耦电容一方面的确可以为SSN提供低阻抗的本地通路而达到噪声抑制的作用,但是另一方面,退耦电容的寄生电感使得电容在高频的阻抗增大而使得噪声抑制失效。这是由于实际的电容器总会存在一些寄生参数,当电容安装到PCB板上时,就会有安装电感存在。总的安装电感Ltotal见图5中的公式。一般来说,电容的寄生参数在低频时表现并不明显,但是在高频情况下,其重要性可能会超过容值本身。业界普遍的观点是,一般的表贴封装退耦电容的去耦范围在100MHz以下。

图5:退耦电容。

【分页导航】

| • 第1页:PI重视不够 Core电压降到1V发生改变 | • 第2页:电源设计和DDR设计 让人头痛的问题 |

| • 第3页:四个方面去考虑 SSN方面降低电源噪声 | • 第4页:退耦电容仿真图形结果引发的猜想 |

| • 第5页:退耦电容双方面作用 为什么 | • 第6页:案例分析退耦电容是如何影响SSN的 |

| • 第7页:目标阻抗的角度 选择退耦电容方法 | • 第8页: SSN与平面耦合 要尽量避免什么 |

| •第9页: 吴均谈噪声和纹波的区别 | |

{pagination}

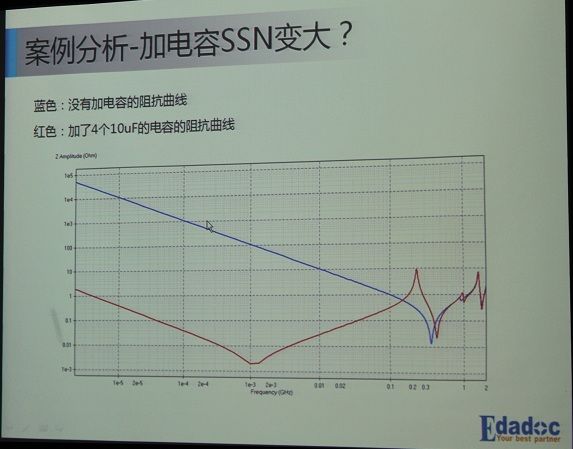

周红伟从一个具体的案例入手分析了退耦电容是如何影响SSN的。图6案例中的仿真图就可以看出,退耦电容在低频时对电源噪声的抑制是非常明显的,但在高频情况下却出现了SSN变大的情况,这是为什么呢?这对我们选择退耦电容有何指导意义呢?周红伟认为,出现SSN变大的原因跟电流的频谱有关。随后他进一步解释了退耦电容的选择方法。

图6:案例分析—加电容SSN变大。

其实我们很多工程师在电源设计时都是凭经验来选择退耦电容的,这具有一定的盲目性。而根据电源噪声的频谱来选择相应的电容,虽然可以很好地优化电源,也比较有针对性,但却有一定的滞后性。那么到底有没有什么更好的方法来选择退耦电容呢?

【分页导航】

| • 第1页:PI重视不够 Core电压降到1V发生改变 | • 第2页:电源设计和DDR设计 让人头痛的问题 |

| • 第3页:四个方面去考虑 SSN方面降低电源噪声 | • 第4页:退耦电容仿真图形结果引发的猜想 |

| • 第5页:退耦电容双方面作用 为什么 | • 第6页:案例分析退耦电容是如何影响SSN的 |

| • 第7页:目标阻抗的角度 选择退耦电容方法 | • 第8页: SSN与平面耦合 要尽量避免什么 |

| •第9页: 吴均谈噪声和纹波的区别 | |

{pagination}

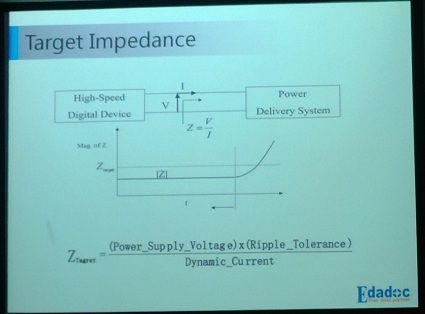

周红伟从目标阻抗(Target Impedance)的角度提出了一个选择退耦电容的方法。目标阻抗的计算方法见图7。公式中的Dynamic_Current一般取最大电流的50%,当然这只是一个经验值。不得不承认,这样取值的话是可能会存在一些过设计在里面的。

图7:目标阻抗的计算方法。

由于电源噪声V(f)=I(f) ×Z(f),在目标阻抗确定时,选择退耦电容的关键在于电流频谱。对于电容组合的选择,需要考虑的问题很多,比如,选什么封装、什么材质、多大的容值、容值的间隔多大、主要时钟频率及其各次谐波频率是多少和信号上升时间等等,这需要根据具体的设计来专门设计。通常,用钽电容或电解电容来进行板级低频段去耦。高频小电容的选择需要分频段计算。可以把需要去耦的频率范围分成几段,每一段单独计算,用多个相同容值的电容并联以达到阻抗要求,不同频段选择不同的容值。还有一点需要注意的是,容值的等级不要超过10倍。

板级上能做到100MHz,可100MHz以上的频段呢?对这个问题,吴均表示这个一般都是交给芯片厂商,在芯片级去解决,我们只需要关注100MHz以下频段的就足够了。

【分页导航】

| • 第1页:PI重视不够 Core电压降到1V发生改变 | • 第2页:电源设计和DDR设计 让人头痛的问题 |

| • 第3页:四个方面去考虑 SSN方面降低电源噪声 | • 第4页:退耦电容仿真图形结果引发的猜想 |

| • 第5页:退耦电容双方面作用 为什么 | • 第6页:案例分析退耦电容是如何影响SSN的 |

| • 第7页:目标阻抗的角度 选择退耦电容方法 | • 第8页: SSN与平面耦合 要尽量避免什么 |

| •第9页: 吴均谈噪声和纹波的区别 | |

{pagination}

对SSN与平面耦合的问题,周红伟说,“一般来说,电源地之间的距离越近高频阻抗越小,电源地间距越小噪声也会越小。如果你的芯片工作频率刚好在谐振点附近,我们怎么样来解决这个问题,如果芯片不能动的话,我们可以采用相应的方法来改变谐振频点。可以通过加小电容和地孔的方法来使谐振点偏移,从而尽量避免芯片的工作频率与谐振点重合。”

他进一步指出,平面谐振的影响因素有平面的形状,叠层结构,退耦电容可以提高系统的谐振频率,地孔也可以提高系统的谐振频率。

另外埋容可以有效地降低高频阻抗。这是因为埋容可以让电源地离得更近,回路电感会更小。

最后,周红伟总结说,电源设计需要注意电源地耦合、电容组合要多样化、电容放置合理、电源平面加电容和适当多加一些地孔。对于电容的放置,应该尽量靠近芯片放置,当然很多时候不可能所有的电容都放置在芯片周围,这时就需要选择将小电容靠近芯片,并且均匀地放置在芯片周围。另外,一般情况下,小电容选择小封装,大电容选择大封装。而谐振问题可以加电容和加地孔来解决。

本次技术分享沙龙总共得到了8位资深工程师的支持,大家对技术问题的探讨不仅在会上,就连茶歇期间都不放过。《电子工程专辑》对本次沙龙的全过程都进行了录像(图集)

图8:与会工程师在茶歇期间也不忘记技术交流。

【分页导航】

| • 第1页:PI重视不够 Core电压降到1V发生改变 | • 第2页:电源设计和DDR设计 让人头痛的问题 |

| • 第3页:四个方面去考虑 SSN方面降低电源噪声 | • 第4页:退耦电容仿真图形结果引发的猜想 |

| • 第5页:退耦电容双方面作用 为什么 | • 第6页:案例分析退耦电容是如何影响SSN的 |

| • 第7页:目标阻抗的角度 选择退耦电容方法 | • 第8页: SSN与平面耦合 要尽量避免什么 |

| •第9页: 吴均谈噪声和纹波的区别 | |

{pagination}

除此之外,吴均对噪声和纹波的区别给出了自己的解释,他表示,目前为止并没有协会定义什么是电源纹波,什么是电源噪声。我们将电源纹波理解为电源模块包括前面提到的VRM的输出电压的波动和复杂的供电网络无关,或者说是电源输出的源端的电压波动,电源噪声则是指由源模块工作在实际产品系统中,经过供电分布网络讲电源能量输送到芯片管脚处,在芯片管脚处的电压的波动,或者简单说是电源输出的末端的电压的波动。因此,一般都认为电压的波动在源端叫纹波,在末端叫噪声。

而对于纹波测试,业内普遍的说法是用20M的带宽来进行,负载端电源噪声测试用的是500M的带宽,当然这也存在一个争议,比如说DDR3工作在800Mbps,和1600Mbps,那么我时钟可能在800MHz,这个时候按照3倍频率或者5倍频率的概念,那你就需要到6GHz的示波器,才能测准DDR3这样一个噪声,是不是需要500MHz的带宽来测试就够了,还是你需要用全带宽呢?吴均认为这个各有各的说法,业界并无定论。

图9:本次技术分享沙龙的参会工程师与工作人员合影。

《电子工程专辑》网站版权所有,谢绝转载

【分页导航】

| • 第1页:PI重视不够 Core电压降到1V发生改变 | • 第2页:电源设计和DDR设计 让人头痛的问题 |

| • 第3页:四个方面去考虑 SSN方面降低电源噪声 | • 第4页:退耦电容仿真图形结果引发的猜想 |

| • 第5页:退耦电容双方面作用 为什么 | • 第6页:案例分析退耦电容是如何影响SSN的 |

| • 第7页:目标阻抗的角度 选择退耦电容方法 | • 第8页: SSN与平面耦合 要尽量避免什么 |

| •第9页: 吴均谈噪声和纹波的区别 | |