KinanaHussain

产品行销经理

Vitesse半导体公司

10Gbps(10G)以太网、SONET/OTN、InfiniBand(QDR/FDR)和光纤通道产品的资深设计师都很清楚,维持10Gbps速率信号的质量远比在1至3Gbps速率范围时更困难。随着背板和网络接口速率进入10Gbps时代,那些正在开始设计其首款10Gbps产品的工程师将不得不面对信号质量的新现实。

10Gbps速率会遇到不连续性问题,它不仅存在于单个设备,还存在于电路板的电气连线,因而会对PCB布局和基板材料的选择(如FR4)同时产生影响。看起来工整、“干净”的发射信号在接收器端会变得面目全非,如图1的眼图所示。

图1:眼图清楚显示了发射信号波形和接收信号波形之间的信号衰减。

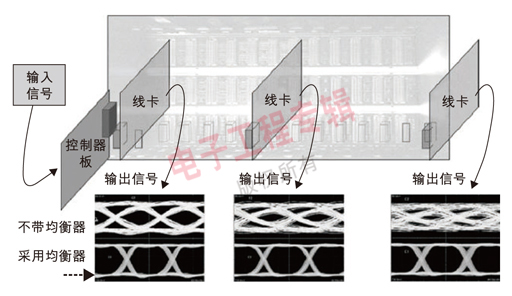

对于工作在10Gbps及以上速率的线卡和背板,表征其信号完整性问题需要同时可视化板级和器件级设计,如图2所示。

图2:适当的均衡能够成功恢复信号路径上产生的衰减叠加。

事实上,尽管系统开发人员必须了解高速设计中使用的每个器件的均衡化和纠错能力,但PCB设计师一直被称为10G设计方法学的“守门人”。当一项任务需要在板级和器件级同时考虑时,一些导致信号完整性问题的常见因素就浮现出来:

PCB布局:一些物理设计特点(例如使用过孔根(via stub))会对工作在数十Gbps数据信道上的信号完整性产生严重影响。高级设计中采用的加扰技术会使AC耦合问题加剧。随着标准8B/10B编码升级至66B/64B,这种加扰技术的难度也提升了一个数量级。

不好的过孔布局加上AC耦合会导致信号发生显著的基线漂移,并且无法通过输入均衡化来缓解。所以,必须在器件级和电路板级都遵守设计规则,并辅以实时眼图监测。这并非是惧怕高速设计的原因。对行为的实时监控是确定性的,而且借助成本合理的测试设备,信号也是可以被监控的。不过,必须从高速设计的早期阶段,就考虑信号质量的约束条件。例如,采用Back-drilling技术处理过孔根;使导线间隔至少三个介电层厚度以实现隔离;最后,使用一个大的AC耦合电容以滤过低频分量。

平面不连续性:通过适当的信号终止并采用简单、直接的PCB布局可以解决不连续问题。当不连续性贯穿整个设计,通过使用带许多过孔根的多层电路板、带多个过孔的表贴元件以及具有快速传输边沿速率的所有类型器件(尤其是表贴元件)时,问题就出现了。信号迹线上的大量过孔会导致波导模式。因此要恰当安排接地过孔的间距,以防止产生波导模式;尽量将接地过孔安排在没有信号走线的开放区域。

边沿速率设计技巧:这是一个与设计所使用的特定器件有关的问题,并对板级布局有影响。快速输出边沿和上升时间可以消除或减少对预加重或去加重的需要;不带预加重或去加重的设计,能够提供更小的串扰和更低的功耗。考虑边沿速率使我们能够在器件级,更恰当地思考信号完整性问题。

发射均衡:通过使用时钟驱动器,可在数字域进行预加重、去加重和预补偿;或者以模拟方式,采用基于时域的多衰减滤波器进行上述处理。

接收均衡:多级模拟输入信号的均衡处理比简单的单级设计更加复杂,但高频设计需要非线性输入均衡。仔细规划此类设计,可采用诸如FR这样的低成本PCB材料。

{pagination}

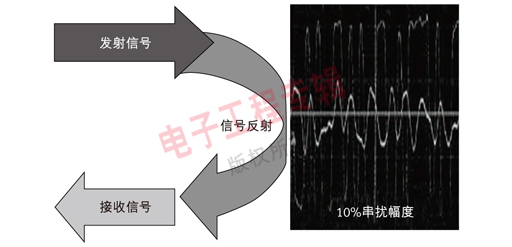

在发射链路和接收链路中,高级均衡能够充分利用重定时器信号的优势--模拟均衡来补偿线性高频损耗;重定时电路中的数字均衡器或判决反馈均衡器(DFE)和IC器件有助于应对串扰和反射问题,如图3所示。

图3:即便是中等程度的串扰,也会因反射而影响信号完整性。

随着背板设计者为遵从10GBASE-KR标准,从单一信道转向多条10Gb串行信道;线卡接口开发人员转用新出现的QSFP+、CFP、CXP等收发器模块,在许多情况下,几乎都需要使用重定时器芯片。

器件级和板级波形分析:随着高速设计中的许多器件都采用均衡处理,一个常被忽视的问题是--波形分析变得愈加困难。100Mbps和1Gbps设计中干净且“张开”的眼图,在10Gbps以上速率设计中几乎无法与噪音区别开来。许多半导体供应商转而在高速线卡设计中采用嵌入式探针和测试点技术,其中最先进的设计可提供来自芯片级的完整的嵌入式波形分析。

更广泛地使用嵌入式分析功能,不仅可在基准测试中对眼图进行实时监测,还带来其它好处。带嵌入式测试功能的重定时器器件,可以远程并连续监测网络节点,以实现诸如自动保护开关等功能,本质上等同于在系统各处都放置了一台示波器。这就允许针对子信道相位调制、信号验证和假锁检测等属性,有针对性、间接地使用监视器。

随着非线性均衡方法和带有DFE的重定时器的使用越来越普遍,并且,嵌入式波形分析功能也不再仅是测试平台独有,设计人员可能会发现,10Gb时代的信号完整性问题变得相对易于解决。10Gbps信道带宽正在成为未来40Gb和100Gb系统最基本的标准设计,今天10Gbps系统所采用的设计方法将会被以后数代设计沿用。

不过,需要注意的是:在信道速率超过3Gbps,并向10Gbps及更高速率迈进时,旧式的电路板走线设计方法(诸如采用单级线性均衡,并企图在没有嵌入式探针的情况下观察波形等)将很难满足要求。总之,10Gbps速率的信号完整性问题是个大挑战,但并非无法克服。

本文来自《电子工程专辑》2012年2月刊,版权所有,谢绝转载。