作者:邵乐峰

为加快上市时间并同时实现产品差异化,使用业界标准内核来开发SoC不失为一种明智的选择。但随着消费电子、人机界面、数字多媒体等新兴应用的涌现,业界对多核技术的期望值也在节节攀升。而在嵌入式领域,不断提高处理器主频的做法已经不能满足不断增加的性能要求,而且势必造成功耗的增加。由于嵌入式系统的成本/功耗限制比PC更为严格,这就使得多核在嵌入式SoC领域有了充分的用武之地。

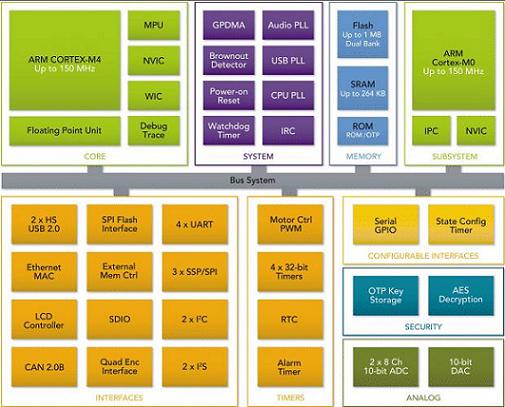

NXP Cortex-M4/M0双核微控制器

多核方案一般包括对称多处理(Symmetrical Multi-Processing)、非对称多处理(Asymmetric Multi-Processing)和混合多处理(Bound Multi-Processing)三种。日前,恩智浦半导体(NXP)就宣布推出全球首款采用ARM Cortex-M4和Cortex-M0双核架构的非对称数字信号控制器LPC4000系列。“这种组合方式开创了业界ARM Cortex构架处理器研发的先河。”该公司副总裁暨全球微控制器产品线总经理Geoff Lees表示,“我们将工程师最需要的处理器单元进行了整合,而且不需要他们编写额外的算法来分配核与核之间的运算关系。这对于那些纠结于到底是采用一个还是两个Cortex-M4进行设计的工程师来说,非对称构架是最好的选择。”

作为提供全系列ARM内核微控制器产品厂商,32位ARM MCU毫无疑问将承担更多为NXP攻城拔寨的重任。来自NXP方面的消息称,在LPC4000系列中,M4作为主处理器融合了微控制器基本功能,如集成的中断控制器、低功耗模式、低成本调试和易用性,以及高性能数字信号处理功能,包括单周期MAC、单指令多数据(SIMD)技术、饱和算法、浮点运算单元。而M0则作为协处理器,用来分担Cortex-M4处理器大量数据移动和I/O处理任务,减小Cortex-M4带宽占用,使得后者可以全力处理数字信号控制应用中的数字计算。

“非对称双核架构降低了功耗、成本和系统复杂性,为开发人员提供了单一芯片解决方案,让软件分配变得更简单。”Geoff进一步解释说,“目前我们推出的产品只是M4+一个M0构架,未来随着用户需求的逐步增加,我们还有可能继续增加作为协处理器的M0数量,变成一个M4 + N个M0的结构。”

Geoff还特别强调了LPC4000系列独有的可配置外设功能,包括可配置状态机定时器、SPI闪存接口和串行GPIO接口。其中可配置状态机定时器由状态机和定时器阵列构成,可实现多种复杂功能,包括事件控制的PWM波形生成、ADC同步和死区控制;SPI闪存接口能够为绝大部分SPI和quad-SPI闪存制造商提供无缝高速的存储器映射连接方法;而首次采用的串行GPIO接口则允许开发人员连接任何非标准串行接口以及多种标准仿真串行接口,比如:I2S、TDM多通道音频、I2C等接口。该系列部分产品的其他外设包括2个HS USB控制器、片内HS PHY、支持硬件TCP/IP校验的10/100T以太网控制器和高分辨率彩色LCD控制器。

此外,LPC4000系列还采用了优化的256位宽度闪存架构,具备264 KB SRAM以及双块存储器架构,可支持1MB闪存安全编程和存储器分区。同时,LPC4000系列的标准特性还包括含有启动代码和片内软件驱动的32 KB ROM、AES-128解密、8通道通用DMA控制器,2个具有最高采样率为400k/s的10位ADC/DAC、马达控制PWM和正交编码器接口、4个UART、2个Fast-mode Plus I2C、I2S、2个SSP/SPI、智能卡接口、4个定时器、窗口看门狗定时器、报警定时器、具有256字节电池供电备份寄存器的超低功耗RTC以及最多146个通用I/O引脚。

至于为何选择推出双ARM内核构架,Geoff认为,DSP+ARM构架的产品主要面向中高端应用,而NXP则希望通过Cortex-M4 + Cortex-M0的双核架构打开马达控制,工业自动化,汽车配件以及嵌入式音频等领域。

LPC4000系列结构框图

{pagination}

TI DSP/ARM Integra处理器

与NXP LPC4000系列的市场诉求不同,TI日前针对工业控制、航空电子、视觉应用和高端测量测试等需要较强运算和信号处理能力的领域,推出了集成DSP+ARM架构的Integra系列处理器C6A816x。

“有很多算法在DSP平台可以实现,在ARM上也可以;但有些特定的算法,如数据滤波、图像处理等放在DSP上运行的效率会高很多,可能达到60%以上”,TI数字信号处理系统业务拓展经理程自清表示,“在某些高端的应用场合,ARM+DSP会起到事半功倍的效果。”究其原因,因为DSP可专门用于处理密集型信号处理需求、复杂的数学函数以及影像处理算法,而 ARM 则可用于实现图形用户界面(GUI)、网络连接、系统控制以及多种操作系统下的应用处理。另外,ARM资源可以空出来做更多的应用,总体性能会大大提高。

C6A816x处理器在同一芯片上集成了1.5GHz TMS320C674x 浮点与定点DSP和ARM Cortex-A8处理器,此外还集成了针对各种应用而优化的数种高带宽外设,包括 PCIExpress Gen2、SATA 2.0、双千兆位以太网和双DDR2/DDR3 接口。另一方面,该系列处理器还配备了片上显示引擎,能够为2个同时工作的高清显示屏输出两组不同的内容流。“这对于高端机器视觉系统等应用而言非常重要,其中一个显示屏可提供触摸屏键盘功能,而另一个显示屏则能显示机器性能及视觉分析结果。”程自清补充说。同时,C6A8168处理器还专门集成了3D图形加速器,可实现更高级、更丰富的精彩GUI体验。

在接受媒体采访时,程自清以机器视觉产品为例,详细介绍了基于C6A8167的方案是如何帮助客户简化设计,并提高可靠性的。在以往此类产品的系统设计中,工程师往往需要FPGA进行算法和数据整理,同时利用DDR做影像视觉处理和特征提取的算法,另外还需要uProcessor做系统管理和通讯等,特别是在一些高端的显示中,总体成本非常高。而采用C6A816x产品,首先接口可以全部集成在其中,同时又集成了定点、浮点DSP和高性能ARM,据称此举可节约超过50%的成本。

C6A816x产品图

本文属于《电子工程专辑》网站作者原创,谢绝转载。