在前不久于美国加州举行的ARM开发者大会上,ARM公司发布了Cortex系列多内核处理器Cortex-A9。这是ARM继7月份发布ARMv7架构的多处理扩展版本以来的又一次重要产品发表。早在2006年初,该公司CEO Warren East就曾暗示Cortex系列将推出多处理器内核。

单核的Cortex-A9在性能上大抵相当于已推出的Cortex-A8处理器。但A9系列还有两个、三个乃至四个内核集群的产品,能提供超过8,000Dhrystone Mips(DMIPS)的对称多处理(SMP)性能。这种内核是可综合的,采用先进工艺时的时钟频率有望超过1GHz,不过当时钟减慢或内核被关断时才可达到最大功率效率。

此外,这种架构可以扩展到四个以上的内核。“被授权者可以根据需要在芯片上配置一个以上的集群。”ARM多处理项目经理John Goodacre表示。这家IP供应商把这种架构瞄准了HDTV机顶盒、家庭服务器引擎和移动互联网手机等应用。

目前,好几家公司都已获得Cortex-A9授权,其中包括NEC电子、Nvidia、三星、ST和TI。但是据Goodacre透露,目前相关芯片还未上市,对ARM合作伙伴而言,可能要到明年第一季度才能够确定具体的交付日期。

A9内核是Cortex-A8的改进版。“它增加了几条支持多处理的额外指令,并后向兼容。”Goodacre提到。像A8一样,A9也是超标量体系结构,带有一个多事件8级流水线。程序对前面的分支解算进行异步评估,目的在于取指,每时钟周期允许连续获取和解码两条指令。

不过A9流水线更进一步,还支持乱序指令分发及完成。

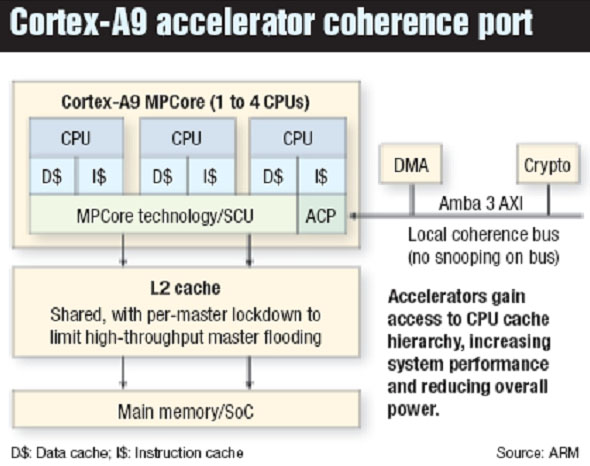

这种新的架构带有一个支持硬件加速器和DMA单元的加速器一致性端口(ACP),增强了ARM目前的多处理器能力;带有中断虚拟化功能,支持TrustZone技术;还带有一个通用中断控制器(GIC)。

作为一个完全成熟的ARMv7器件,A9 MPcore支持Thumb2 指令、TrustZone、浮点运算单元(FPU)与Neon——用于流媒体处理的ARM单指令多数据扩展。与每个内核相关的指令和一级数据缓存都整合了缓存一致性支持,通过一个Snoop控制单元(SCU)进行同步。有一条本地一致总线与SCU相链接。

与传统相悖,A9一开始是作为一个可综合内核被提供的。“考虑到对处理而言附加的FPU或Neon、缓存容量、中断方案以及接口等方面,它还是可配置。”Goodacre表示。

尽管ARM的这一设计还没有完全定案,但该公司已开始授权。“我们向获授权者提供beta版的设计文件。预计明年第一季可以推出正式版本。”Goodacre称。

这表明获授权者可能还需要再等12到18个月的时间才能实现芯片的制造。“我预计2009年底第一款使用Cortex-A9的器件将上架销售,2010年开始量产。”Goodacre提到。

此外,预计这一目前以65纳米为基准的设计文件将在45纳米芯片中亮相。

在OS支持方面,Goodacre例举了一些运行在ARM11 MPcore上的成功方案,包括Mentor Graphics公司的Nucleus;通用Linux内核;QNX实时操作系统;MontaVista软件公司的Mobilinux,以及日本eSol有限公司的一种不对称和对称多处理混合的实现方案。“Symbian尚未正式支持ARM11上的多处理,但它们已在实验室实现运行。”Goodacre表示。

图8:Cortex-A9加速器一致性端口(ACP)