在不远的将来,现代家庭的客厅都将配备具有IPTV功能的数字电视、高清电视(HDTV)机顶盒和高清视频光盘播放机。移动设备中也将越来越多地增加娱乐媒体回放功能。很快,所有设备都将能播放专业制作的娱乐内容。

支持视频播放的下一代家庭与便携设备的设计者在考虑他们以后的SOC设计架构时必须清楚什么对此类设备消费者来说才是最重要的。现在有很多IP供应商提供可集成进SOC的视频处理器内核或硬件模块。在评估这些内核和模块时,设计师必须清楚市场在支持各种视频标准方面的发展动向。

多种不同的视频标准

尽管H.264已成为未来系统与设备的全球性优秀视频编码标准,但仍有越来越多的标准在被人们采用。例如,下一代视频光盘和DTV标准要求采用Windows Media Video 9或SMPTE VC-1编码;有些IPTV系统采用MPEG-4及类似编码;很多系统出于兼容目的仍要求采用MPEG-2编解码;实时双向视频会议系统仍广泛采用H.263标准;中国的国家广播则主要采用AVS编码标准。

不同类型的设备对编解码性能的要求也不尽相同。例如,机顶盒只需解码高质量的视频信号,而视频会议设备则必须同时进行实时的视频编解码。电池供电的设备要求低功耗,而装备有移动天线的设备则需要特别强的比特流纠错能力。

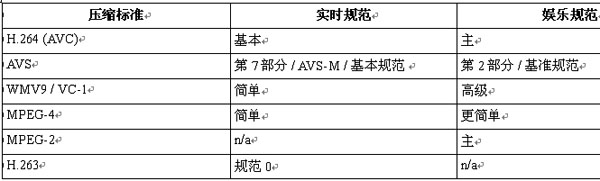

由于许多编码标准又根据采用的编码技术对哪些应用和设备有益而细分为不同的规范,这就让视频处理世界变得更加复杂。通常,适用于双向通信类的规范要求具备实时编码能力但只需进行低复杂度的纠错,而用于专业娱乐视频编码的规范则要求更高压缩率和更低解码成本。表1所示为主要压缩标准的实时应用类规范和娱乐应用类规范。

对于将来的视频设备甚至移动设备,能解码H.264主规范(Main Profile)之类的娱乐视频规范是很重要的。例如,手持式设备中的全功能DVB-H解码器必须同时支持H.264基本规范(Baseline)和主规范(Main Profile)。终端用户产品要在市场中取得成功,必须支持恰当的解码规范。

早期RCA Lyra便携式媒体播放机的购买者就曾因为发现它无法播放任何带B帧编码的视频而大感失望。B帧虽然提高了压缩率,但要实现实时编码则很困难,因此只有部分娱乐类规范使用它。Lyra播放机的这一缺点导致用户从因特网上下载的大部分视频都无法观看。这种功能上的不足在竞争日益激烈的消费品市场迅速导致了一个视频播放机产品线的消亡。Lyra的失败为Archos公司的产品 stellar的成功让出了道路。

要处理多样化的编码标准和规范,需要多格式的可编程视频处理器。消费者对娱乐和通信的要求刺激了芯片制造商采用既能处理娱乐类规范也能处理实时类规范的可编程视频处理器。一般认为硬连线的视频模块面积更小,但当同时需要多种模块以满足多种标准时,整个视频功能模块的面积就可能比采用处理器实现时占用的面积大得多。而且硬连线的视频模块在应付这些不断发展的视频标准中的各种变化时也不够灵活。因此,现在绝大部分芯片设计师都只会考虑采用可编程视频处理器。

表1:实现压缩标准中不同部分的各个规范。

关键是能高效地处理各种标准

然而,仅仅因为一个处理器能够编程并不意味它就能高效地处理每一种标准。通用嵌入式CPU若用于处理视频流则显得配置不足,仅解码一段低质量的视频就不得不以极高的主频运行。因此,这种方案对便携式设备而言能效比太低。相反,专用视频处理器中集成有专用指令集,可以利用SIMD(单指令多数据)技术进行像素数据的并行处理或利用特殊指令进行视频数据的串行处理(例如熵解码、运动向量预测等)。在设计Diamond 388VDO标准视频引擎时,Tensilica公司在标准32-bit RISC指令集之外还增加了很多视频专用的指令集以优化引擎的视频处理能力。

要实现用于H.264 主规范的处理器尤其困难。H.264主规范采用了比特流无损熵编码中基于上下文的自适应二进制算术编码(CABAC)方法。要从CABAC比特流中解码每个二进制元素(称为bin)需要依赖于前一bin的完全解码结果,每个bin都对解码器的状态有很大影响。有两种嵌入式处理器能严格用软件实现实时CABAC解码:菲利普半导体(NXP)的Trimedia和Tensilic Diamond 388VDO。全软件CABAC解码这种方法经证实有一大优点,那就是在高比特率工作情况下能够达到最高效的性能。

Tensilica能够使用指令集扩展实现全软件的熵解码,因而能创建出可处理复杂比特流的低时钟速率、高能效视频处理器。例如,Tensilica能以仅162 MHz的时钟速率实现对一个5 Mbps比特流的所有D1 Main profile解码。

与此类似,H.264 Main profile支持B帧和交织式视频内容,而这两项功能会给经验不足的视频处理器和编解码器开发人员带来很大困难。解决视频编解码器难题最简单的方法就是增大DRAM存储器带宽。这种方法在高端PC机上没有问题,但用在嵌入式系统中就不现实了。由于受功耗和成本限制,嵌入式系统无法承受这样的DRAM带宽浪费。

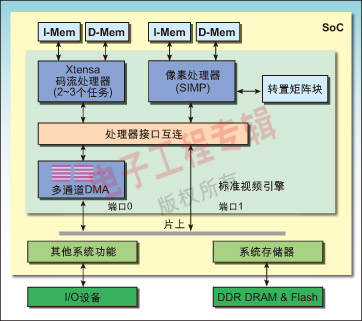

图1所示为Tensilica Diamond388VDO标准视频引擎的框图。其中包含两个Tensilica Xtensa可配置处理器和一个DMA控制器,可最大限度发挥视频压缩解压算法固有的并行性。Diamond 388VDO内核中的流处理器和像素处理器共同分担视频压缩任务,DMA控制器则负责在处理器内核内外和两个处理器之间传送压缩前后的图象。Diamond 388VDO视频引擎中的每个处理器都有自己的指令集和数据RAM。

图1:Tensilica的 Diamond388VDO视频引擎框图。

Diamond视频引擎内核中的这两个处理器都采用了Tensilica的可配置Xtensa处理器架构。流处理器通过增加额外指令集来完成比特流解析和熵编码。这些新指令中一部分基于Tensilica的FLIX(可变长度指令扩展),并采用每条指令执行两次独立操作的VLIW指令格式。像素处理器中也增加了可同时操作多个像素的SIMD(单指令多数据)指令。

流处理器和像素处理器中添加的指令使Diamond视频引擎能够在时钟速率低于200MHz时以标准显示分辨率(SD或D1)和30帧/秒的速度编码MPEG-4 ASP(Advanced Simple Profile)比特流或解码H.264/AVC MP(Main Profile)、MPEG-4 ASP、MPEG-2 MP、和VC-1/WMV 9 MP视频比特流。低时钟速率通常意味着低功耗,该引擎之所以选择200-MHz的时钟速率是因为该引擎可以采用普通的低成本130nm IC加工工艺制造。

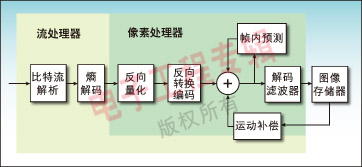

图2所示为Diamond视频引擎在解码H.264/AVC视频数据流时内部的任务分配情况。流处理器用于完成比特流解析(包括分离网络抽象层、图象层和片层)和熵解码。像素处理器则用于完成反向量化、反向变换编码、帧内预测、运动补偿和图像解块处理。流处理器也可辅助像素处理器进行运动补偿。

图2:Diamond 388VDO视频引擎在进行H.264/AVC解码时的内部任务分配情况。

需要注意的是,在一块处理器上运行所有这些解码任务其实是可能的,但这需要高得多的时钟速率,而时钟速率高意味着需要采用更加昂贵的工艺技术。为了尽可能减小电池供电的便携式视频产品的功耗,Diamond 388VDO视频引擎即使在解码标准分辨率的视频时都保持很低的时钟速率,从而最大限度减小了功耗。

所有视频解码任务都应在处理器外完成

在评估不同的视频处理器性能时,很重要的一点就是检查并确保系统主CPU的处理器内核无需承担任何视频解码任务,包括所有比特流解析任务。传统视频处理器,例如Hantro出产的处理器,只将运动估计之类的像素处理功能挪至主CPU外完成,而给系统控制器留下了运算量很大的一部分任务。这些开销可能要求SOC设计师采用更加庞大也更耗电的系统控制器,这在便携式设备的设计中是需要付出昂贵代价的。

研究一下业界领先的家用和手持嵌入式视频设备,我们会发现最好的视频处理器是那些以高比特率和低内存带宽处理娱乐类数据的处理器。只有深刻理解各种视频规范,并清楚哪些规范需要利用下一代设备来实现,SOC架构师们才能正确评估不同IP厂商提供的产品。

移动多媒体产品部技术行销经理

Tensilica 公司