近年来,随着ESG意识抬头,企业为求永续经营,无不使出浑身解数规划自身的ESG步骤与时程。在半导体业,降低芯片内晶体管的漏电,减少耗能,就是一种实践环境永续性的具体作法,而降低漏电也成了多年来电晶体架构革命性演进的主要驱动力。

在平面式晶体管架构中,通道长度(Channel length)因工艺技术随着摩尔定律越缩越短,当低于数十纳米时,短通道效应(Short-channel effects)所导致的漏电就越来越严重,因此在2000年有了3D鳍式晶体管(FinFET)原型架构的诞生[1],并于2011-2012年开始实现商业化的量产。

鳍式晶体管架构是将原本平面的源极(Source)和漏极(Drain)转变成立体结构,让栅极(Gate)三面包覆通道,使得栅极与通道之间的接触面积变大,提升栅极控制电子的能力,因而可以降低漏电。但随着工艺技术不断的推进,通道长度持续缩减,研发工程师很快地理解到,当栅极与通道之间的接触面积缩小到某一程度后,漏电将再度成为一个必须面对的课题。

因此,在鳍式晶体管商业化生产几年后,各研究单位与重要的电机电子工程师学会会议就开始酝酿与讨论新一代晶体管架构的研发技术蓝图,虽然最终各家对于新一代晶体管架构的名称莫衷一是,但其核心的概念都是要增加栅极与通道之间的接触面积以进一步提升栅极控制电子的能力。

之前鳍式架构的栅极是三面包覆通道,为求在缩减通道长度的状况下,增加栅极控制电子的能力,新一代的架构是让栅极四面整个包覆通道,称为环绕式栅极晶体管(GAAFET)架构。全球主要先进工艺的晶圆代工厂都已经揭示采用环绕式栅极架构的时程[2],这当中又以韩国三星(Samsung)最为积极,率先在3纳米工艺节点采用环绕式栅极架构,并于2022年正式发布投产[3]。

第一个采用Samsung环绕式栅极架构工艺的不是一般消费性产品,而是用于挖矿专用的ASIC芯片Whatsminer M565++(MicroBT),与消费性产品最大的不同是Whatsminer M565++芯片仅有逻辑单元,并没有内存单元,虽然赢得了全球第一个量产环绕式栅极晶体管的瞩目眼光,但显然在工艺良率上的挑战仍大。

经过一年多的技术提升与优化,Samsung第一个一般消费性产品采用环绕式栅极架构工艺终于在2024年发布,产品是用于Samsung Galaxy Watch 7的处理器-Exynos W1000,采用的工艺技术为Samsung在2023年推出的第二代环绕式栅极架构3纳米工艺节点。

虽然环绕式栅极晶体管有较佳的效能,但相较于发展已相当多年,工艺相对成熟的鳍式晶体管工艺,环绕式栅极晶体管的工艺更为复杂且遭遇的技术挑战困难许多,为了达到工艺与晶体管效能的优化,工艺研发上势必导入不少技术创新,本次泛铨科技利用高空间解析的穿透式电子显微镜(Transmission electron microscope, TEM)搭配能量色散X-射线光谱(Energy dispersive X-ray spectroscopy, EDS)带你一窥Samsung环绕式栅极晶体管的工艺细节。

我们这次所研究的产品是用于Samsung Galaxy Watch 7的处理器-Exynos W1000,其采用的工艺技术为Samsung第二代环绕式栅极架构3纳米工艺节点[4],由Samsung官网所公开的信息,新的3纳米工艺环绕式栅极架构在单核与多核的效能上比前一代(仍是鳍式晶体管架构)分别提升了3.4与3.7倍[5]。

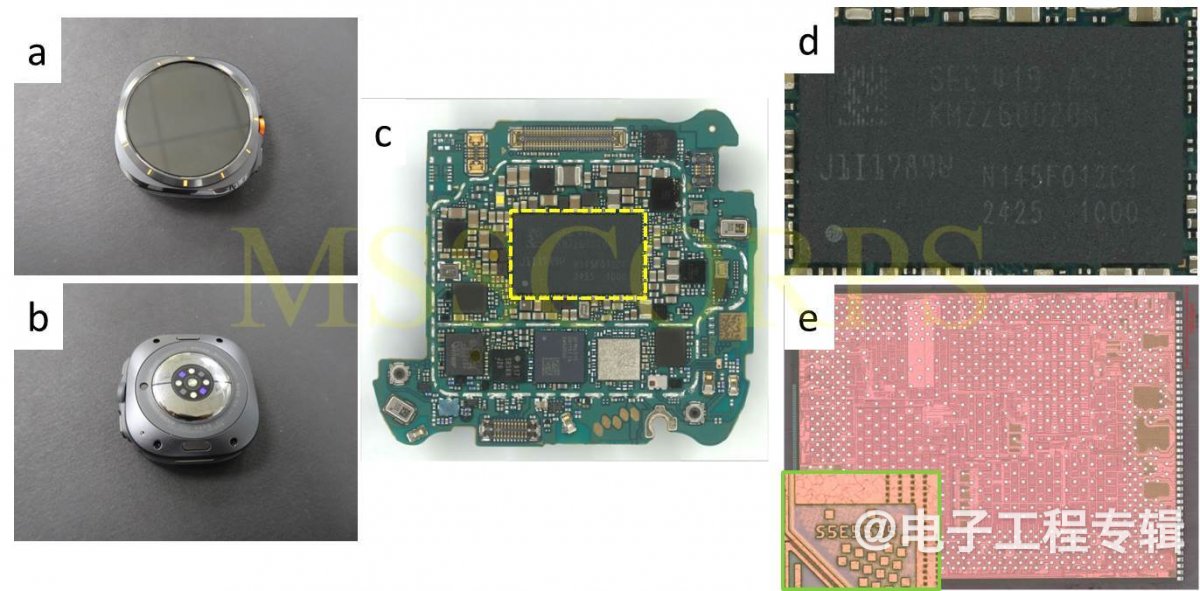

图1a与b为我们这次购买Samsung Galaxy Watch 7的正面与背面照,拆开手表后可以看到主要的PCB版(图1c),板子上由黄色虚线方框标示的就是本次分析的主角Exynos W1000,其表面雷射刻号可以由图1d清楚看到,在去除封装体后,我们可以看到整个芯片的样貌与标志编号。

图1, a & b Samsung Galaxy Watch 7的正面与背面照,c 主PCB版光学显微镜图,Exynos W1000由黄色虚线方框标示,d Exynos W1000特写光学显微镜图,e Exynos W1000去除封装体后光学显微镜图,芯片标志编号为S5E5535。

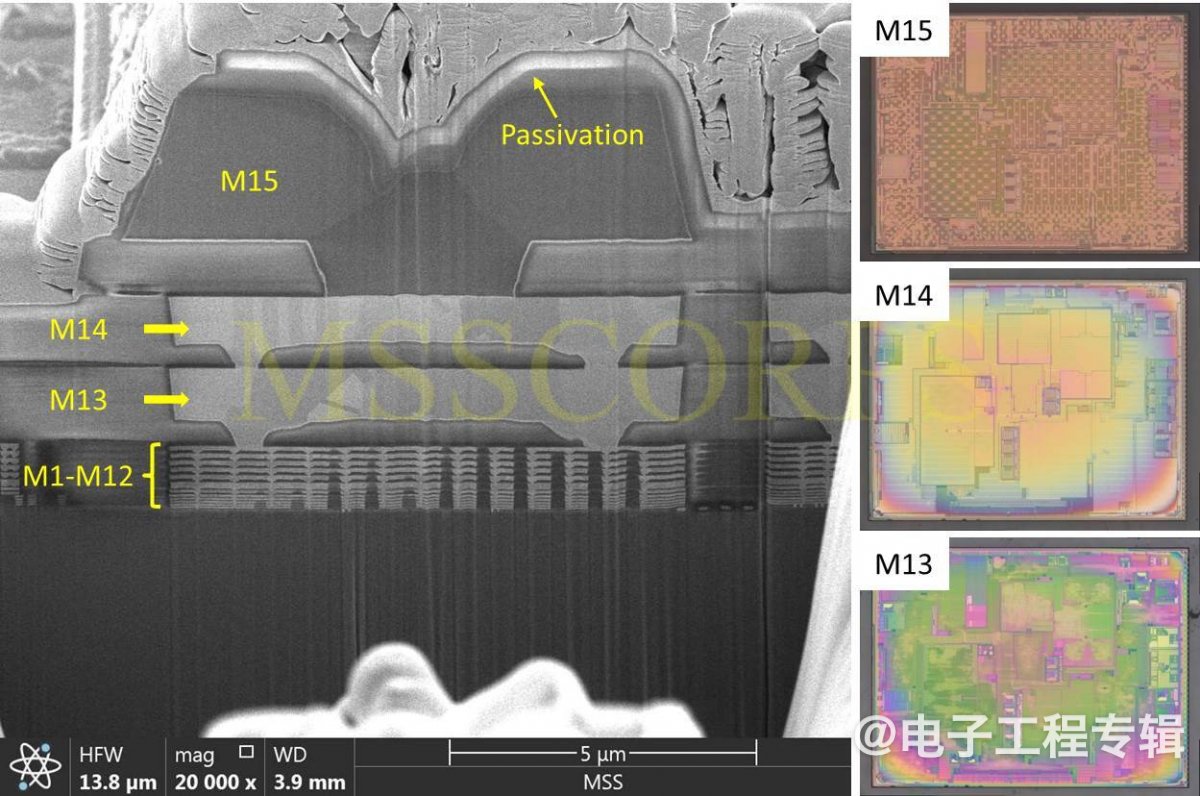

欲了解Exynos W1000工艺的第一步,我们可以由聚焦离子束截面(Focused ion beam cross-section, FIB CS)分析开始,图2左侧大图为芯片的截面图,由图中我们可以清楚看到Exynos W1000的工艺为一层保护层(Passivation layer)加上15层的金属层(Metal layer),其中最上层的金属层(M15)也就是重布线层(Redistribution layer, RDL),除了由截面分析获得Exynos W1000的初步工艺信息,透过逐层的平面去层(Parallel mapping)我们可以了解各金属层的布局(Layout)。

图2,左侧大图为Exynos W1000截面聚焦离子束分析截面图,右侧分别为M15、M14、M13的光学显微镜图。

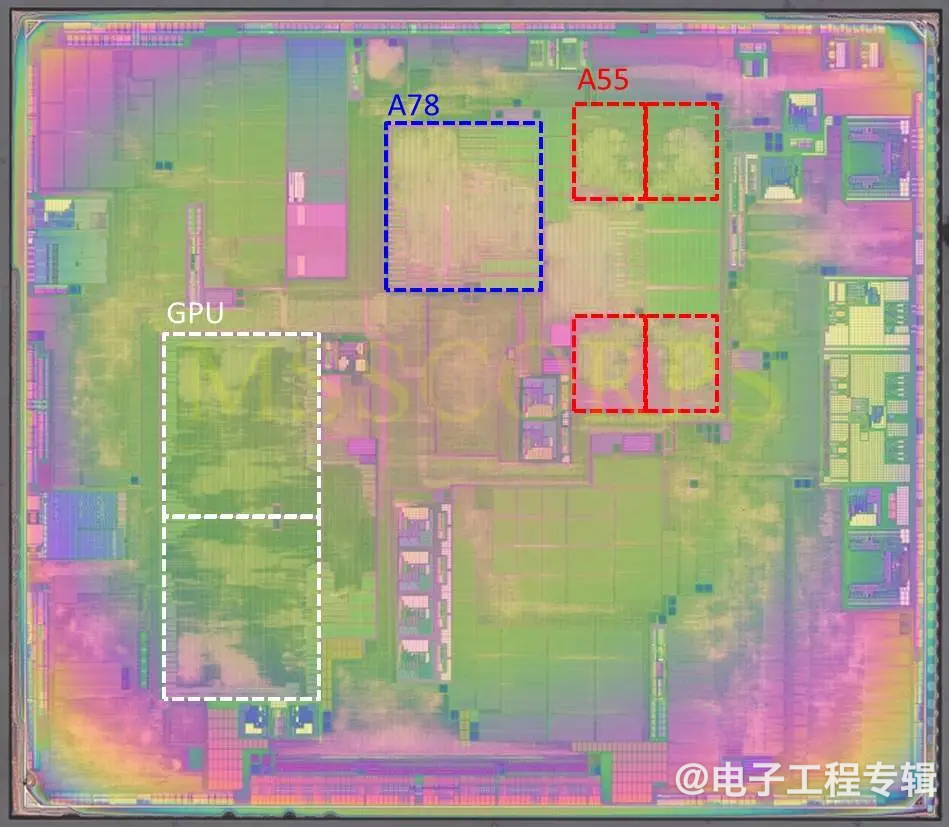

图2右侧是我们利用全平面去层技术,将Exynos W1000由M15处理到M13的光学显微镜图。根据Samsung官网的信息[5],Exynos W1000有一个高效能的大核心CPU,Arm Cortex-A78与4个小核心CPU,Arm Cortex-A55,GPU部分则是2核心的Arm Mali-G68 GPU,这些主要的CPU与GPU核心位置分别以不同颜色的虚线方框标示于图3中。

图3, M13光学显微镜图,CPU与GPU分别以不同颜色虚线方框表示,A78为Cortex-A78,A55为Arm Cortex-A55,GPU为Arm Mali-G68 GPU。

Exynos W1000是全球第一个用于一般消费性产品采用环绕式栅极架构的微处理器,到底这新的架构与目前主流的鳍式架构有甚么差异,就让我们利用最先进的穿透式电子显微镜与绝伦的分析技术,一一为你解开它的神秘面纱。

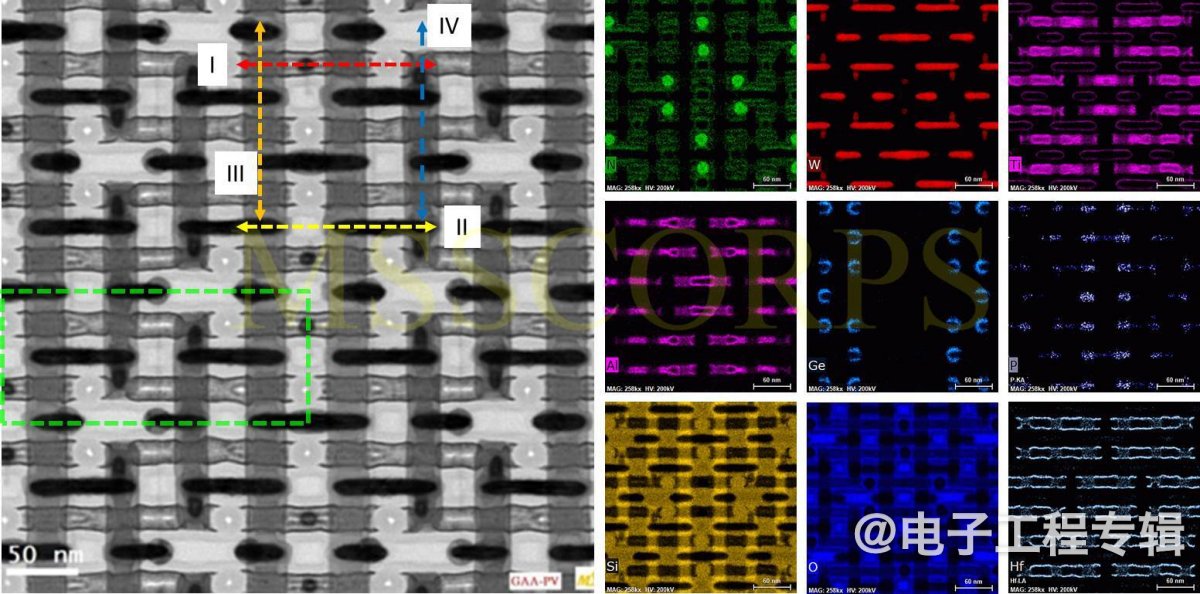

我们分析的位置是每个微处理器都会有的6T-SRAM(Static random-access memory)区域,图4左侧大图是6T-SRAM的平面穿透式电子显微镜(PVTEM)照片,6T-SRAM是由六个晶体管所构成,包含两个PMOS与四个NMOS,其单位胞(Unit cell)由绿色虚线方框标示,藉由EDS mapping分析(图4右侧小图),我们可以获得组成元素的分布图,由分析的结果显示,Samsung新一代的环绕式栅极架构并没有出现有别于先前Samsung FinFET 4nm鳍式架构的新元素。

图4,左侧大图为6T-SRAM平面STEM图,单位胞由绿色虚线方框标示,I, II, III, IV分别为XTEM的分析方向,I方向为Along Gate,II方向为Along S/D,III方向为Along N-GAA,IV方向为Along P-GAA,右侧小图为左侧大图各个元素的EDS Mapping分析结果。

由于环绕式栅极架构较为复杂,平面加上截面观察才能完全显现其3D结构,因此我们分别在四个方向(图4左侧大图内以I, II, III, IV标示)以截面穿透式电子显微镜(XTEM)分析,来清楚解析环绕式栅极架构的细节。

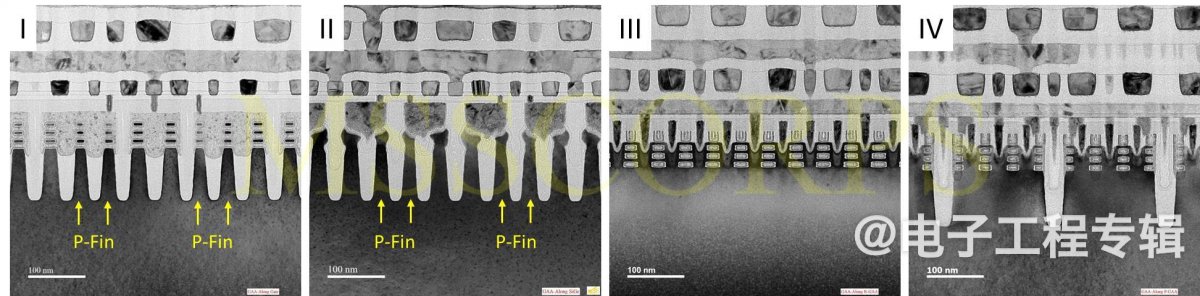

图5为这四个方向的XTEM照片,由图5I可以清楚的看到无论是P-Fin或是N-Fin上方都有三个信道,信道侧边可以由图5III & IV观察到,因此通道四方都完全被栅极所环绕,这与我们先前发布的Samsung鳍式架构TEM照片有很大的差异。

图5, XTEM图,分析方向为沿着图4左侧大图所标示的四个方向,黄色剑号标示为P-Fin位置。

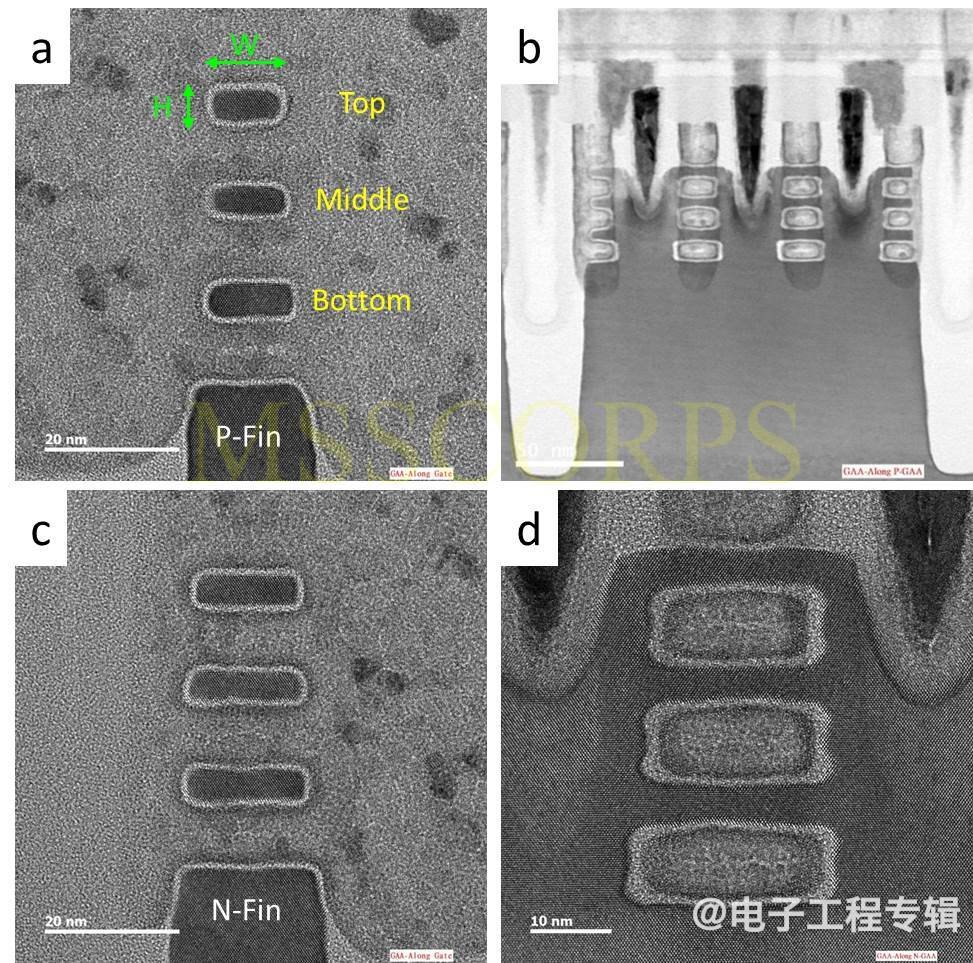

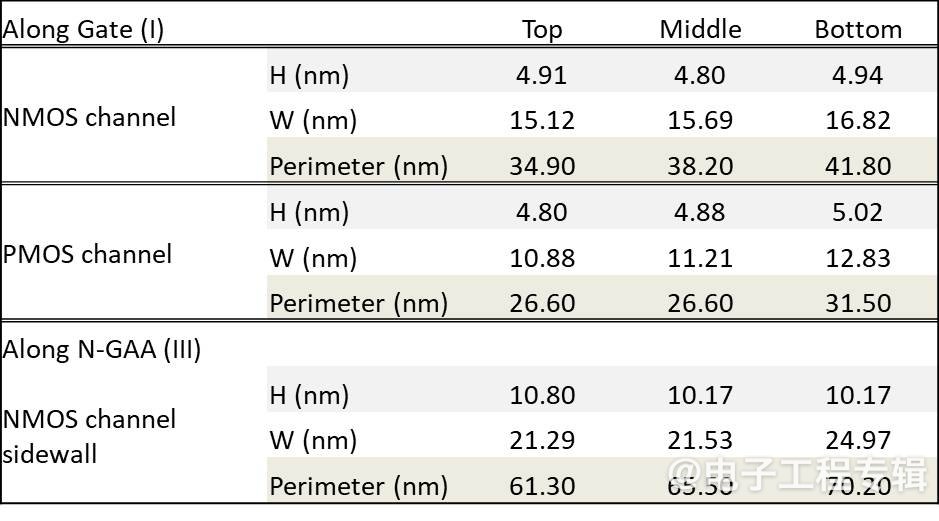

通道的数量与截面积都是决定晶体管在作动时能够乘载多大电流的关键参数,由高解析的TEM照片(图6),我们可以获得更多环绕式栅极架构的细节,图6a与c清楚地显示出P-Fin与N-Fin在I方向(Along gate)上的通道截面积有明显的差异,N-Fin上的通道截面积明显比P-Fin上的通道截面积大,而由III (Along N-GAA,图6b)与IV(Along P-GAA,图6 d)方向的TEM照片结果显示,P-Fin与N-Fin上的通道侧边面积大小并没有明显差异,我们将通道相关的关键尺寸(Critical dimension, CD)整理在表1中。

图6, a & c分别是PMOS与NMOS沿着I方向(Along Gate)在信道位置的TEM放大图,W & H定义为通道宽度与高度的关键尺寸,b PMOS沿着IV方向(Along P-GAA)在信道侧壁位置的TEM放大图,d NMOS沿着III方向(Along N-GAA)在信道侧壁位置的TEM放大图。

表1, 通道关键尺寸量测表,量测位置标示于图6a。

由PVTEM与XTEM照片,我们可以清楚知道比起鳍式架构,环绕式栅极架构在工艺上的复杂度与困难度都高出许多,导入多项新的工艺,包含磊晶成长(SiGe/Si epitaxy, S/D epitaxy)、蚀刻(Fin reveal, cavity etch, NW release)、…等等[6],由于工艺节点已来到只有数纳米尺度,为让晶体管能够发挥最佳效能,工艺要求的规格已经到了原子级的严谨程度,多一排或少一排原子最后都会造成晶体管在效能上的差异或甚至失效。

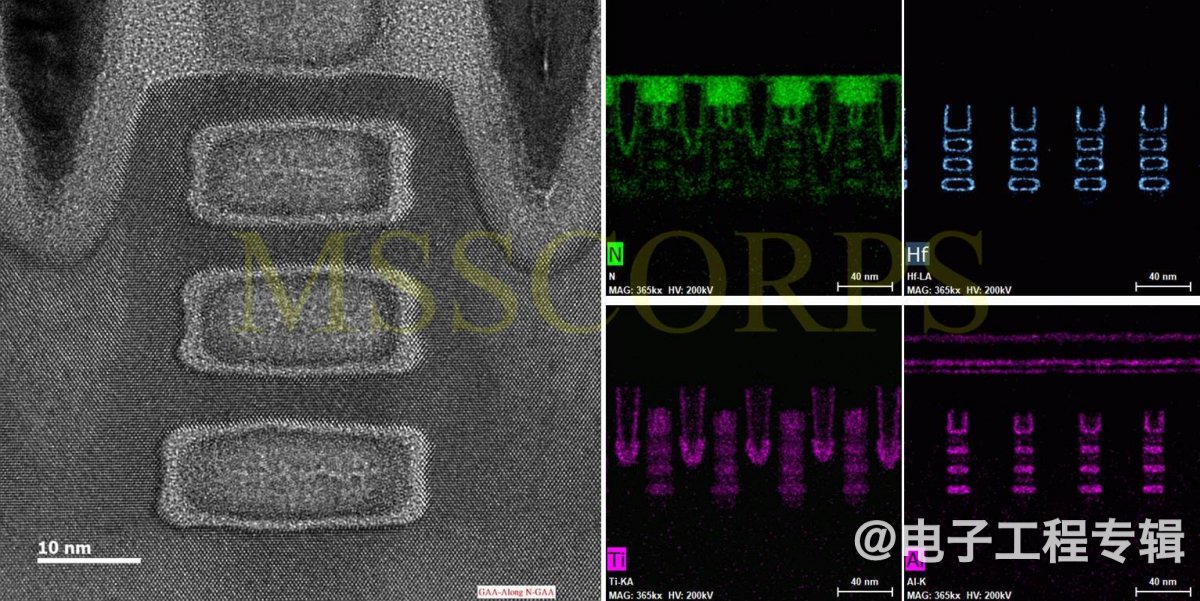

举晶体管最重要的电性参数之一临界电压(Threshold voltage, Vth)为例,临界电压是栅极控制信道电流开(”1”)与关(”0”)的关键,实务上,临界电压越小越好,临界电压的大小与栅极/信道之间功函数(Work function)的差异有正相关,而功函数的差异与材料的特性与堆栈(Stacking)质量有关[7],为求精准地控制功函数的差异,栅极/介电层/信道堆栈结构的接口平整度就扮演了相当重要的角色,由图7左侧大图我们可以清楚看到环绕式栅极堆栈与接口平整度的状况,右侧小图为部分元素的EDS Mapping,可以了解高介电材料与栅极的组成元素的分布状况。

图7,左侧大图为NMOS沿着III方向(Along N-GAA)在信道侧壁位置的高解析TEM图,右侧较小倍率的小图为其中四个元素(N, Hf, Ti, Al)的EDS Mapping分析结果。

由图4到图7,我们也清楚的认知到,要分析先进晶体管架构的工艺细节,具有高空间分辨率的穿透式电子显微镜将是一个唯一且不可或缺的工具[8]。

综合上述的结果与说明,我们可以清楚的了解到工艺技术的创新是推进晶体管架构不断演进的底气,也是芯片整体效能能够持续提升重要的驱动力,环绕式栅极将不会是晶体管架构的终点;因应越趋复杂的工艺架构、多样的材料、以及原子等级的结构尺寸,材料分析也必须与时俱进,以获得精准的实验结果。

[1] D. Hisamoto, W.-C. Lee, J. Kedzierski, H. Takeuchi, K. Asano, C. Kuo, E. Anderson, T.-J. King, J. Bokor, and C. Hu, IEEE Transactions on Electron Devices, 2320-2325, 2000.

[2] Intel预计在Intel 18A导入RibbonFET架构 (https://www.intel.com.tw/content/www/tw/zh/foundry/process.html),tsmc预计在N2导入Nanosheet FET架构 (https://www.anandtech.com/show/18832/tsmc-outlines-2nm-plans-n2p-brings-backside-power-delivery-in-2026-n2x-added-to-roadmap),Samsung则是预计在3nm导入多桥通道场效晶体管FET(MBCFET)架构 (https://news.samsung.com/tw/三星投产gaa架构3纳米工艺芯片)。

[3] https://news.samsung.com/tw/三星投产gaa架构3纳米工艺芯片

[4] https://www.techinsights.com/zh-tw/node/58215

[5] https://semiconductor.samsung.com/processor/wearable-processor/exynos-w1000/

[6] P. Eyben et al., “3D-carrier Profiling and Parasitic Resistance Analysis in Vertically Stacked Gate-All-Around Si Nanowire CMOS Transistors”, DOI: 10.1109/IEDM19573.2019.8993636; N. Loubet et al., “A Novel Dry Selective Etch of SiGe for the Enablement of High Performance Logic Stacked Gate-All-Around NanoSheet Devices”, DOI: 10.1109/IEDM19573.2019.8993615.