近日,2024 IEEE Symposium on VLSI Technology & Circuits在美国召开,中科院微电子所抗辐照器件技术重点实验室李博研究员、杨尊松研究员团队在会上展示了高性能锁相环芯片的最新研究进展。

网路数据交互量爆炸式增长,促使通信技术的不断进步,5.5G、6G、224Gb/s高速接口电路等新一代通信系统要求锁相环频率综合器的RMS抖动小于50fs,这在硅基CMOS集成电路设计中极具挑战。

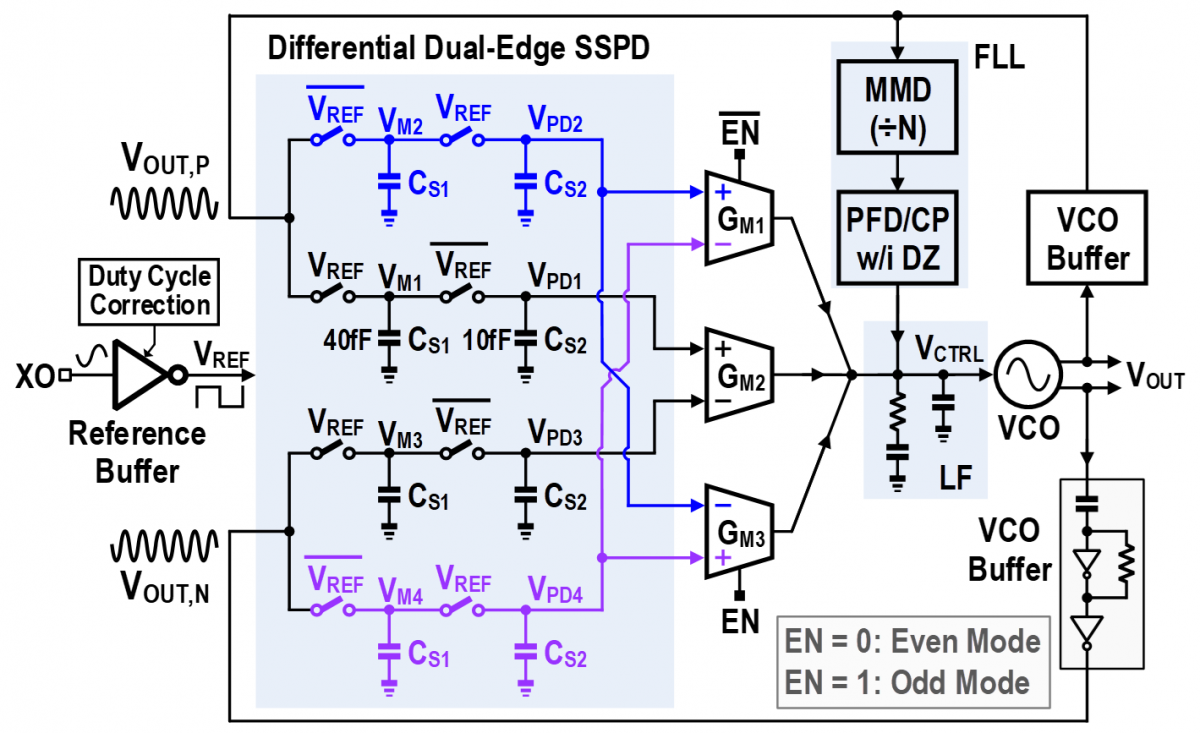

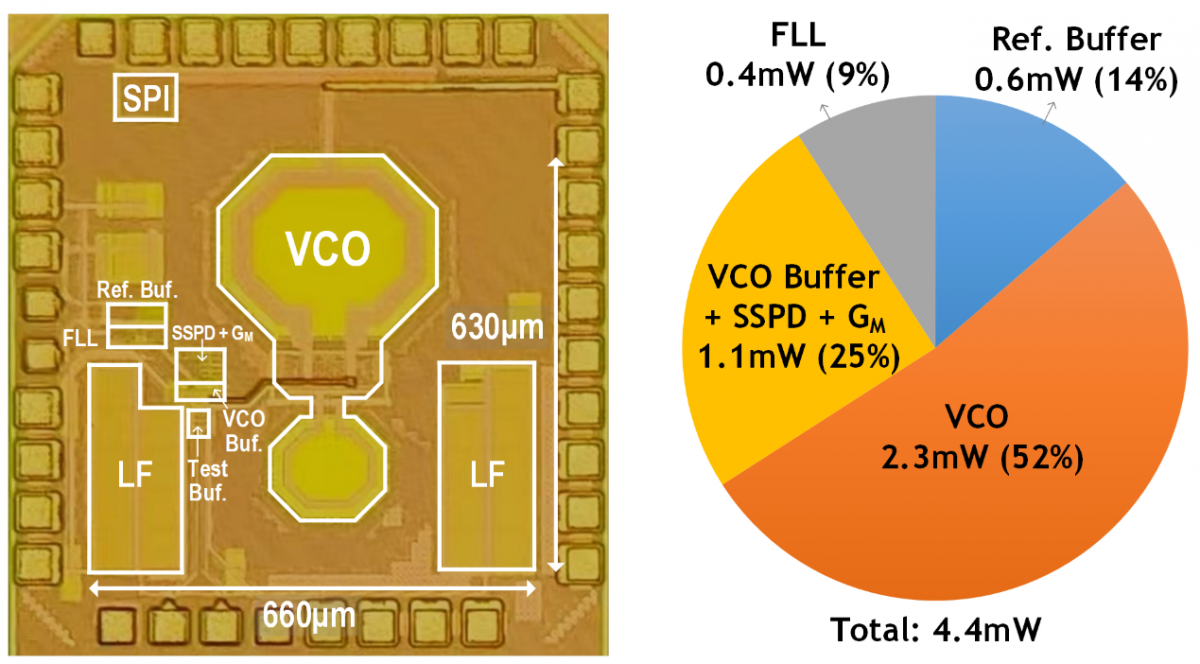

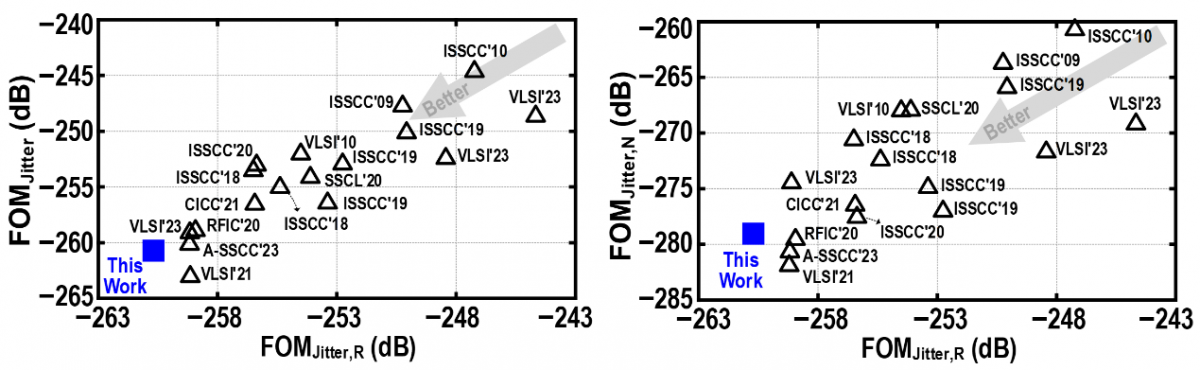

亚采样锁相环的相位锁定环路无需使用多模分频器和重定时器,有潜力在低功耗下进一步提升抖动性能。对于50fs以下极低RMS抖动,参考路径中的缓冲器通常会极大限制亚采样锁相环的带内相位噪声,需要消耗较大功耗和面积将其降低至较低水平。双边沿采样鉴相技术能够将参考缓冲器引入的相位噪声降低3dB,但会恶化频率分辨率。针对上述问题,抗辐照器件技术重点实验室研究团队提出了可配置双边沿亚采样锁相环结构,通过奇偶采样模式切换,能够在同步实现低功耗和低抖动的前提下保持频率分辨率不变,所提出的锁相环结构在硅基65nm CMOS工艺上进行了流片验证,实现了目前国际上最佳的抖动-功耗的参考频率归一化优值。

上述研究成果以“A 6.5-to-6.9-GHz SSPLL with Configurable Differential Dual-Edge SSPD Achieving 44-fs RMS Jitter, −260.7-dB FOMJitter, and −76.5-dBc Reference Spur”为题发表在集成电路设计领域国际顶级会议2024 VLSI Technology and Circuits,微电子所博士研究生陈天乐和任洪宇为该文章的共同第一作者,微电子所杨尊松研究员、李博研究员为该文章的通讯作者。

图1. 提出的双边沿亚采样锁相环电路结构

图2 芯片照片及各个模块的功耗占比

图3 国内外锁相环性能对比