IGZO薄膜晶体管(TFT)由于其极低的关态电流、较高的迁移率和低温工艺,在新型DRAM的应用中备受关注。与传统的硅基1T1C DRAM相比,IGZO 2T0C DRAM具有能够实现多值存储的优势,该优势可提高各个单元的有效存储密度。但目前基于该方面的研究仅实现了单个存储单元的多值存储功能验证,以及多个单元间SN电压的均一性,仍需要较为复杂的外围电路来解决读取晶体管之间阈值电压变化的问题。

针对上述挑战,中科院微电子所刘明院士团队与北京超弦存储研究院赵超研究员团队联合在2023年国际电子器件大会(IEDM)上首次报道了具有单元内阈值电压补偿技术的双栅IGZO 2T0C DRAM。器件层面上,研究通过控制半导体厚度以及优化金属半导体接触,实现了具有正阈值以及高开态电流的双栅a-IGZO晶体管。电路层面上,提出了一种新型的双栅2T0C DRAM结构,通过全新的写入方式,实现了无需外围电路的存储单元内阈值电压补偿技术,并且突破了存储窗口的极限。实验制备的双栅2T0C DRAM首次实现了在25个单元间的3-bit存储功能、目前报道中最大的ΔVSN/ΔVDATA比值(1.46)以及大于1500秒的数据保持时间。

基于该成果的文章“Improved Multi-bit Statistics of Novel Dual-gate IGZO 2T0C DRAM with In-cell VTH Compensation and ΔVSN/ΔVDATA Boosting Technique”入选2023 IEDM。中科院微电子所博士生陈楷飞、超弦存储研究院朱正勇研究员和微电子所博士生卢文栋为第一作者,中科院微电子所李泠研究员、杨冠华副研究员以及超弦存储研究院赵超研究员为通讯作者。

图1:传统单栅2T0C DRAM在多值存储中面临的挑战以及双栅2T0C DRAM在实现多值存储中的优势

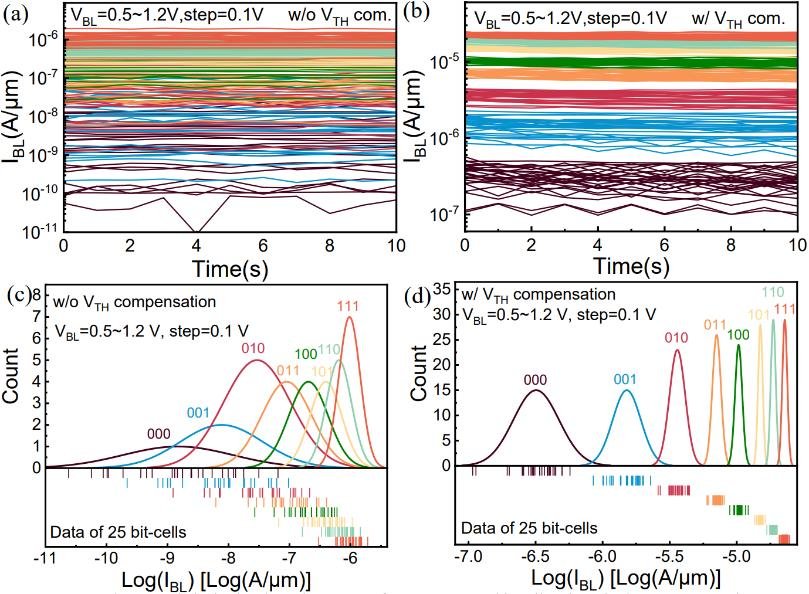

图2:不具有和具有阈值电压补偿功能的25个双栅IGZO 2T0C DRAM的读取电流分布对比