许多IC设计的共同目标都是实现功率、性能和面积(PPA)的最佳组合。通过对RISC-V ISA(指令集架构)扩展的研究,发现有助于大幅降低功耗,同时在不增加额外成本的情况下能实现所需性能。

TWS(真无线立体声)芯片主要包含一个蓝牙射频收发器。它包括128抽头有限冲激响应(FIR)滤波器、128抽头最小均方(LMS)自适应滤波器、有源噪声控制(ANC)混合函数以及计算这些函数所需的计算单元和总线。在这种设计中,四个单元中的前三个需要最多的计算资源:FIR滤波器需要1693个指令周期,LMS滤波器需要1820个周期,而ANC功能所需的周期则高达10404个。系统框图显示了TWS设计的主要构件,左边为模拟功能,右边为数字功能。蓝牙收发器(左上)由一个RF基带控制器和64kb交换存储器组成。位于下面的收发器和音频子系统很复杂,因为TWS的设计有两个独立工作的扬声器和麦克风。两者的锁相环(PLL)必须同步,以确保它们都能以相同的频率工作。

图1:TWS设计的关键构件,左边是模拟功能,右边是数字功能。(本文资料来源:安第斯科技)

更复杂的是,蓝牙系统处理的是小端格式的16位数据,而音频系统用的则是大端格式的24位数据,因此需要计算密集型格式转换。ANC功能对计算资源的需求最大。它需要大量的计算,如乘法和加法。ANC与高精度DAC和低延迟ADC还需要交互。实时模拟采样要求每输出一个样本就有一个样本输入。

右侧的数字部分是一个带有P(DSP/SIMD)扩展的RISC-V CPU和用于处理噪声控制和音频编解码器计算的独立DSP。此外,该设计包含少量的SRAM硬件DMA和AXI/AHB总线矩阵。该设计具有消费设备所需的通用I/O功能,包括GPIO、I2C、实时时钟、UART等。

为了执行最复杂的TWS函数,混合ANC电路需要高抽头数滤波器,在本例中,需要128抽头FIR滤波器和128抽头的最小均方滤波器。为了处理这些函数,每个样本总共需要896次加法和896次乘法。在本例中,ADC和DAC主频为192kHz,大约每5.2微秒进行一次采样。

在所示框图中,处理ADC和DAC操作时,计算资源必须执行以下功能:加载样本的DMA,然后是音频编解码器计算、蓝牙和内务操作。接下来是FIR和LMS滤波器所需的繁重处理任务。除了这些操作之外,ANC也增加了相当多的计算需求,主要是大量的乘法和加法。

定制RISC-V扩展减少指令周期数

认识到对更多计算资源的需求,设计团队决定为RISC-V处理器创建专用于处理FIR和LMS滤波器的定制扩展,每个处理器增加一条指令。另外开发了乘法器、加法器和存储器来处理ANC运算。这些扩展使用Andes自定义扩展(ACE)和CoPilot工具来创建。这些工具省掉了将定制指令集成到设计和验证流程中的耗时任务,从而最大限度地减少了设计团队实施修改所需的时间。

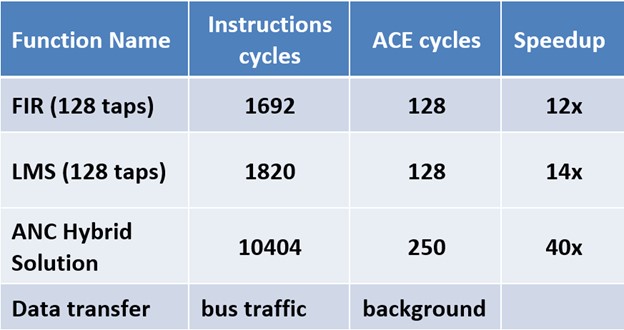

结果如表1所示。纯C代码的128抽头FIR滤波器原来需要大约1600个指令周期,添加定制指令后,周期数减少到128个,速度提高了12倍。同样,计算128抽头LMS滤波器所需的周期也从1820个周期减少到128个,速度提高了14倍。而最显著的加速发生在ANC功能上,所需周期从10404个下降到250个,减少了40倍。应用于TWS平台直接存储器访问功能的CPU周期计数还取决于SoC架构。通常情况下,业务流越大,需要的周期就越多。ACE和CoPilot工具分配了附加的指令背景属性。因此,为了确保最佳功能的实现,定制指令并行运行。因此,CPU可以采用较慢的80MHz时钟频率,从而降低了功耗,并延长了电池寿命。

表1:通过自定义扩展实现的加速(在ACE周期列下)效果。最显著的加速发生在ANC功能上,降低了40倍。

虽然我们暂且还不能对这种专有设计的实际结果发表正式评论,但表中所示数据结果已清楚表明所得到的明显改进,这正是向设计添加定制扩展所产生的结果。除了性能提升之外,使用定制扩展的设计还受益于一种电路,该电路以较低的时钟速率运行,可以节省功耗,并且使用更少的逻辑门,从而所用的芯片尺寸更小。

使用定制扩展的另一个重要好处是,竞争对手不能轻易地对设计进行反向工程。最后,对于那些担心定制会增加设计验证时间的设计师来说,60%成功使用ACE工具的客户经验已证明这不是问题。凭借这种特殊的设计,最终实现了芯片的成功流片,没有任何设计自旋(design spin),目前已用于Razer的True Wireless Pro耳机中。

(参考原文:optimizing PPA with RISC-V custom extensions in TWS earbuds)

本文为《电子工程专辑》2022年11月刊杂志文章,版权所有,禁止转载。点击申请免费杂志订阅