为了满足快速发展的汽车和人工智能(AI)以及机器学习(ML)工作负荷的带宽需求,Rambus等公司开始改变习惯使用外围组件实现高速(PCIe)互连的设计,将PCIe和CXL数据平面有效地结合在一起来优化互连性能。

由于许多行业参与者都为PCIe的发展做出了贡献,因此最新的PCIe迭代几乎没有给业界什么特别惊喜——据说该兴趣小组的成员目前已拥有900多名。在过去的二十年里,PCIe在计算领域中变得无处不在,并且派生了其他许多成熟和新兴的标准,例如高速非易失性内存(NVMe)和计算高速链路(CXL)。

与其前身类似,PCIe6.0针对的是数据密集型环境,例如数据中心、高性能计算(HPC)、人工智能和机器学习。但是,随着现代汽车继续演变为车轮上的服务器——不,是车轮上的数据中心——许多存储技术正在进入汽车应用领域,包括同时使用NVMe和PCIe的固态驱动器(SSD)。

PCIe SIG总裁兼董事会主席Al Yanes表示,PCIe已经成为存储空间和NVMe的代名词,从战略角度来看,汽车已成为大家关注的下一个焦点,汽车正朝着更高的带宽需求发展,就像智能手机自问世以来一样。

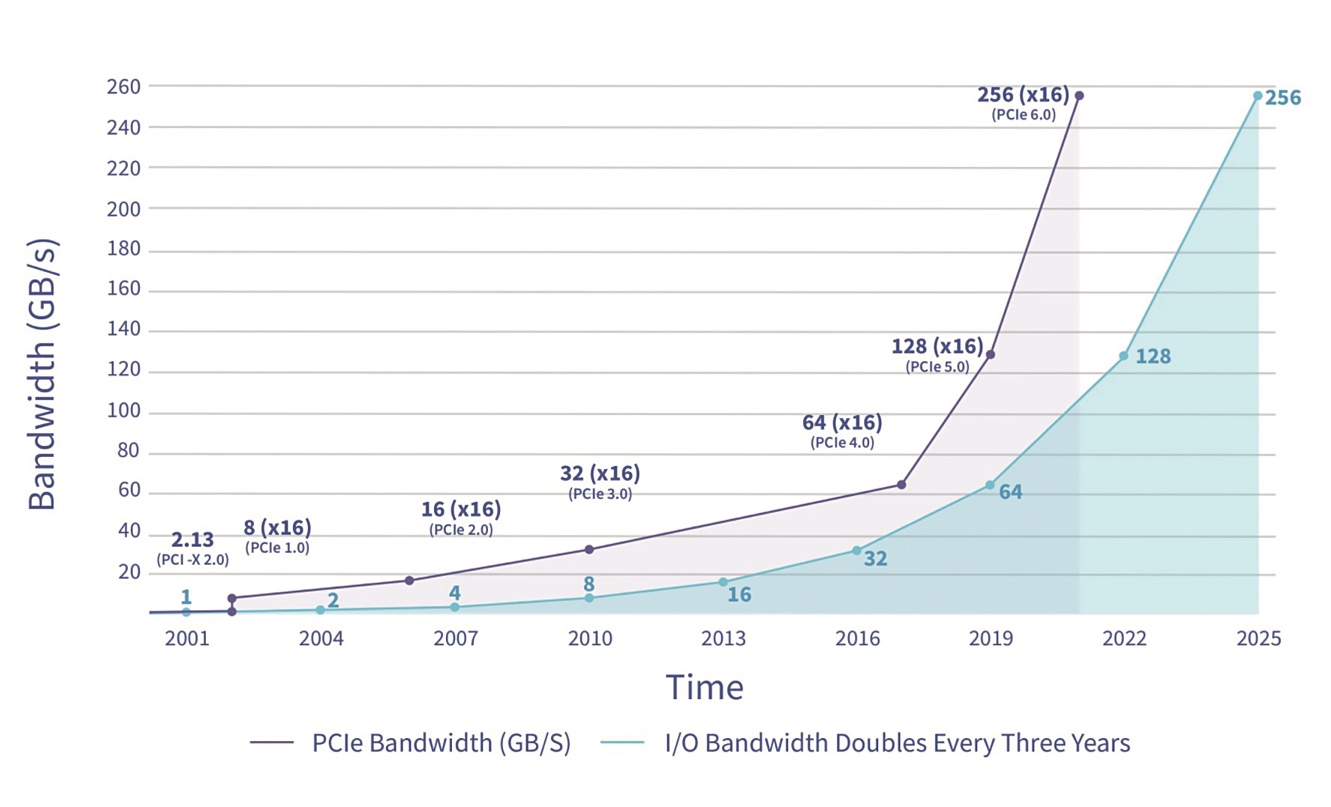

然而,加速器以及人工智能和机器学习应用最需要PCIe 6.0提供的带宽,Yanes在接受电子工程专辑采访时称这是“革命性的飞跃”,这是因为PCIe 6.0提供的带宽是其前身的两倍,原始数据速率可达64GT/s,通过x16配置则高达256GB/s。

图1:PCIe规范每三年将I/O带宽翻一番。(图片来源:PCIe SIG)

PCIe 6.0还实现了脉冲幅度调制4级(PAM4)信令和基于流控制单元(Flit)的编码,后者支持PAM4调制,通过与新添加的前向纠错和循环冗余校验结合使用,可实现带宽翻倍。Yanes解释说,所有这些都是在不牺牲延迟的情况下完成的,而且向后兼容PCIe 5.0。

Yanes表示,不是每个人都需要PCIe 6.0,但它确实为设计人员提供了在保持带宽的同时又减少引脚数量的选择。PCIe SIG成员了解发展路线图也很有帮助,这样他们就可以在规划产品时做出明智的决定。

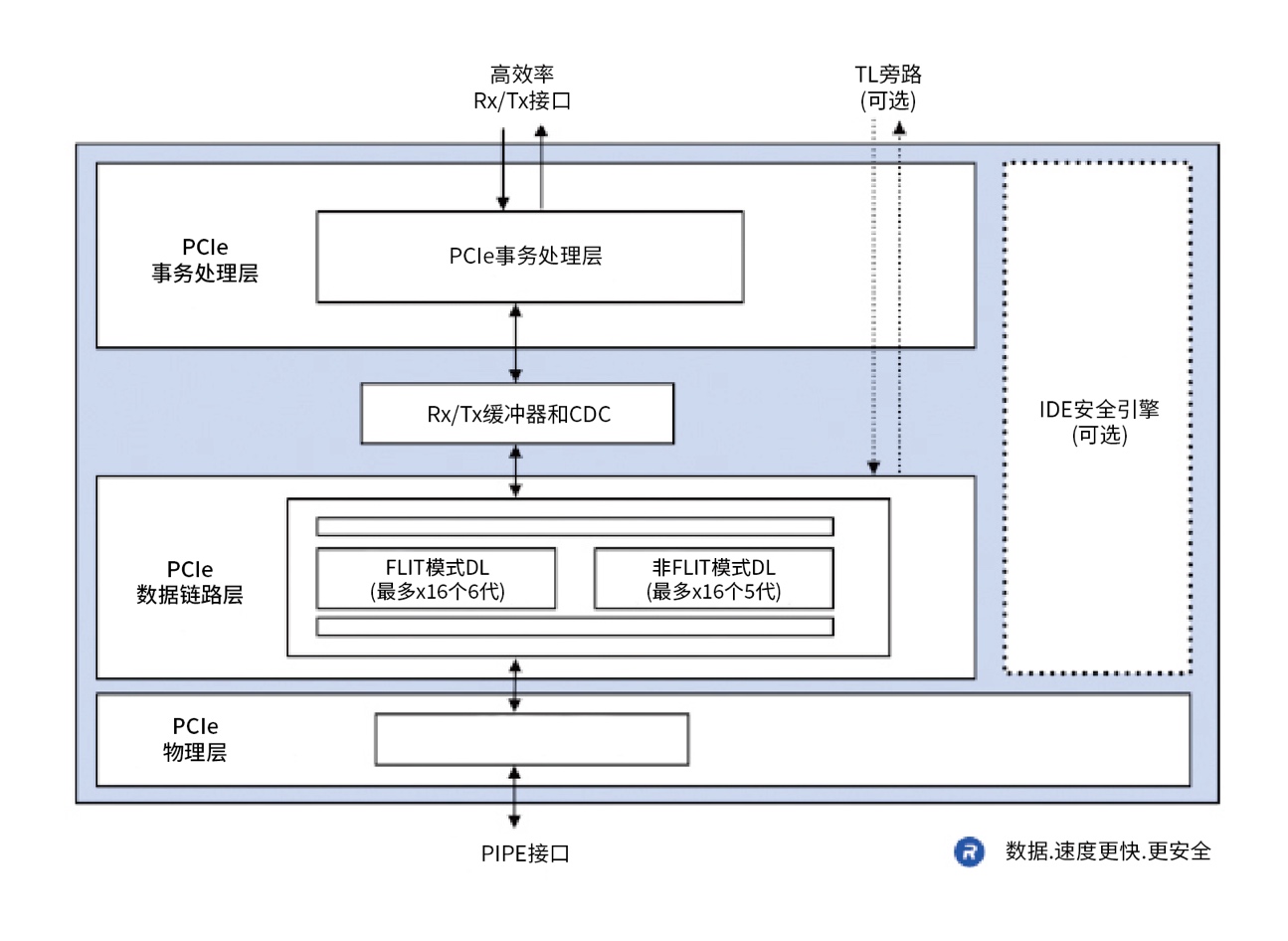

在市场需要时帮助客户整合最新的PCIe迭代,是Rambus宣布推出其PCIe 6.0控制器背后的动力,该控制器旨在满足快速推进的人工智能/机器学习、以及数据密集型工作负载的预期需求。该公司的PCIe 6.0控制器还具有安全功能,包括监控和保护PCIe链路免受物理攻击的完整性与数据加密(IDE)引擎。

Rambus公司IP内核部门总经理Matt Jones表示,控制器开发的关键考虑因素之一是PCIe 6.0和CXL3.0需共享相同的电气接口,这是因为时延是PCIe和CXL数据平面连接的关键。

“我们已经做了一些非常明智的事情,添加IDE后时延基本为零,”Jones透露。比如Rambus充分利用了Flit功能使控制器中的逻辑得到了更好的优化。

对于Rambus来说,准备好支持超前几个月甚至几年的技术并不少见。HBM 3(高带宽内存)规范才刚刚正式推出,但该公司已经帮助其客户准备好了相关设计,这些设计可能要再过18个月才会出现在产品中,而设计中使用的HBM 3内存接口由一个完全集成的物理层和一个数字内存控制器组成。

图2:支持PCIe 6.0的Rambus解决方案。(图片来源:Rambus)

已经宣布PCIe 6.0解决方案的其他公司还包括Tektronix,该公司声称这是业界第一个与PCI Express 6.0兼容的基站发射机测试解决方案。与此同时,PCIe 6.0的普及还有一段路要走,因为PCIe 4.0才刚刚获得广泛的关注,例如美光科技的最新SSD才使用PCIe 4.0和176层的3D NAND。

(参考原文:PCIe 6.0 Designed to Meet Automotive, AI Bandwidth Demands )

本文为《电子工程专辑》2022年6月刊杂志文章,版权所有,禁止转载。点击申请免费杂志订