在实现高密度3D DRAM存储器方面,基于无电容器铟镓锌氧化物(IGZO)的DRAM单元架构具有很大的潜力。本文中,imec公司的存储器项目总监Gouri Sankar Kar向读者展示了一种基于IGZO的DRAM单元。经过IGZO晶体管架构的优化,该单元具有适合DRAM存储器应用的“卓越指标”。此外,在对IGZO薄膜晶体管可靠性的新认知基础上,他还提供了DRAM单元关键元件的首次寿命估算。详见IEEE国际电子器件会议(IEDM 2021)上发表的两篇论文。

迈向高密度3D DRAM

在2020年的国际电子器件会议(IEDM)上,imec首次展示了一种无电容的动态随机存取存储器(DRAM)单元,实现了两个铟镓锌氧化物(IGZO)薄膜晶体管(TFT)且没有电容的单元架构。这种新颖的2个晶体管无电容器(2T0C)的DRAM单元架构,有望克服传统的1个晶体管+1个电容(1T1C)DRAM在密度提高方面的关键约束,该约束就是尺寸小的单元硅晶体管的截止电流太大,以及存储电容器占用太大的面积。而在2T0C IGZO-TFT DRAM单元中,不需要存储电容,因为可以将读取晶体管的寄生电容用作存储元件。此外,IGZO-TFT以其非常低的截止电流而著称,从而可以提高存储单元的数据保持能力。最后,在生产线后端(BEOL)处理IGZO-TFT的能力允许减少DRAM存储器的占用空间(通过将存储器单元移动到存储器阵列下方),并堆叠单个DRAM单元-从而提供一条迈向高密度3D DRAM的路径。这种演进是业界所需要的,可以不断为数据密集型应用(例如人工智能、物联网、数据中心和云计算)提供足够的DRAM容量。

与经典DRAM产品相比,初次演示的首个基于2T0C IGZO且数据保持时间超过400秒的DRAM单元,具有显著更低的刷新率和功耗。这些器件是在300mm晶圆上制造的,栅极长度缩短到了45nm。然而,在这第一个“概念性”演示单元中,IGZO TFT并未针对最长保持时间进行优化,并且仍然缺少对耐用性(即故障前的读/写循环次数)的评估。另外,当时还没有准确模型来预测IGZO器件的寿命。

数据保持时间超过103秒,耐用性不受限,栅极长度可缩短至14nm

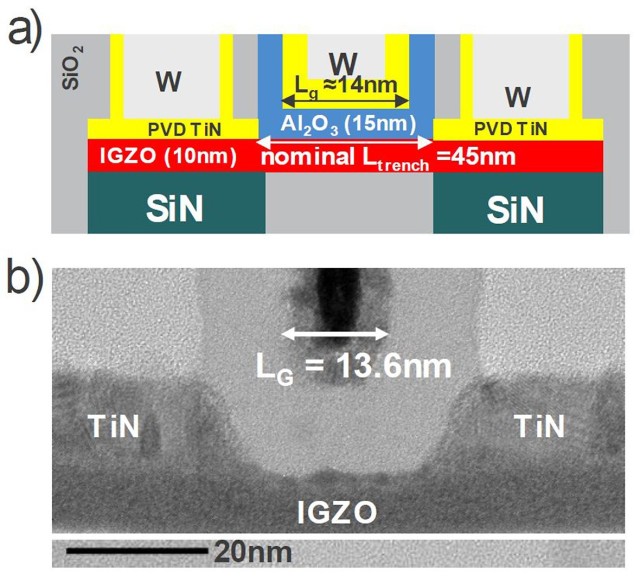

在2021 IEDM上,imec推出了一款完全兼容300mm BEOL的基于IGZO的无电容器DRAM单元,并且指标有所改进,即超过103秒的数据保持时间和基本无限制(>1011)的耐用性。这些结果是在为单个IGZO晶体管选择最优集成方案后获得的,即采用掩埋氧隧道和自对准接触技术的后栅极集成方案。实践证明,埋氧隧道与O2环境中的退火相结合,可以降低IGZO通道中的氧空穴浓度,而且不会影响源极和漏极区的串联电阻,从而支持更大的导通电流和更小的截止电流。

使用这种架构后,IGZO TFT的栅极长度可以缩短到前所未有的14nm,同时仍然具有超过100秒的数据保持时间。通过调节等效氧化物厚度(EOT)来控制阈值电压(Vt)、改善接触电阻以及减少IGZO层厚度,可以进一步优化短栅极长度下的数据保持性能。当IGZO层的厚度减小到5nm时,甚至可以省略O2中的氧隧道和退火步骤——从而大大简化集成方法。

A. Belmonte等人在2021年IEDM发表的题为“对无电容DRAM用的IGZO-TFT架构进行裁剪可获得超过103秒数据保持时间、超过1011循环次数耐用性以及低至14nm的Lg可扩展性”的论文中,对所选集成方法和实现的器件指标提供了更多详细信息。

图1:(a)原理图,(B)具有氧隧道和14nm栅极长度的后栅极架构中单个IGZO晶体管的TEM图像。

基于PBTI可靠性建模的寿命估算

到目前为止,由于尚未完全了解IGZO TFT的劣化机制,因此缺乏用于预测基于IGZO的DRAM寿命的精确模型。IGZO晶体管本质上是n型器件,这表明正偏置温度不稳定性(PBTI)可能是主要的劣化因素。

PBTI是硅n型金属氧化物半导体场效应晶体管(MOSFET)中众所周知的一种老化机制,它会严重影响器件的性能和可靠性。它通常表现为器件阈值电压的意外偏移和漏极电流的降低。对于这些硅基器件而言,PBTI归因于栅极电介质中电子陷阱的存在,会从器件传导沟道捕获电荷载流子。

然而,大多数现有的对IGZO TFT的可靠性评估,都忽略了栅极电介质的影响。Imec首次研究了栅极电介质对IGZO TFT PBTI的影响。结果总结在A. Chasin等人在IEDM 2021发表的题为 “理解和建模薄膜IGZO晶体管的PBTI可靠性” 论文中。

该团队发现有四种不同的机制在劣化过程中起作用,每种机制具有不同的时间动力学和激活能量。它们主要归因于栅极电介质中的电子捕获,以及在PBTI应力期间氢物质从栅极电介质进入IGZO沟道的释放。

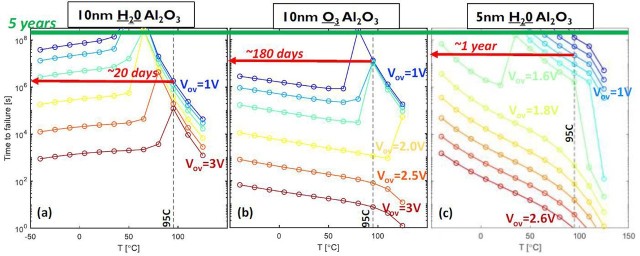

图2:基于不同栅极电介质的(具有12nm厚的非晶IGZO膜)IGZO TFT的无故障时间。

如图2所示,通过在工作条件下对栅极电介质优化,可将寿命从大约20天大幅延长至一年左右。而最终平均无故障时间目标是5年。

imec团队将这多种劣化机制组合成一个模型,进而使得在目标工作条件下,预测IGZO TFT寿命成为可能。他们发现该模型适配实验数据,可用于提出延长寿命的优化方案。

本文小结

对基于IGZO的DRAM单元架构和集成的改进,可以使2T0C DRAM存储单元具有超过103秒的数据保持时间以及无限的耐用性,并可将栅极长度缩短至14nm。这些指标使无电容的IGZO-DRAM成为实现高密度3D DRAM存储器的理想之选。器件改进与对IGZO TFT可靠性的新认知相辅相成,揭示了导致PBTI的不同劣化机制。这些机制构成了一个精确模型的关键要素,通过该模型可实现DRAM存储器关键元件的寿命预测。

(参考原文:Capacitorless DRAM Cell on IGZO Base Shows Promising Values )

本文为《电子工程专辑》2021年3月刊杂志文章,版权所有,禁止转载。点击申请免费杂志订