我们此前曾经探讨了电路原理图中隐含的一些模拟电路结构,但并没有详细说明。其中的关键示例包括阱、抽头和保护环,它们对MOSFET电路的正常工作是必不可少的。

了解衬底在MOSFET电路中的作用对创建有效的模拟设计至关重要。但首先,我们有必要了解MOSFET晶体管的工作原理。

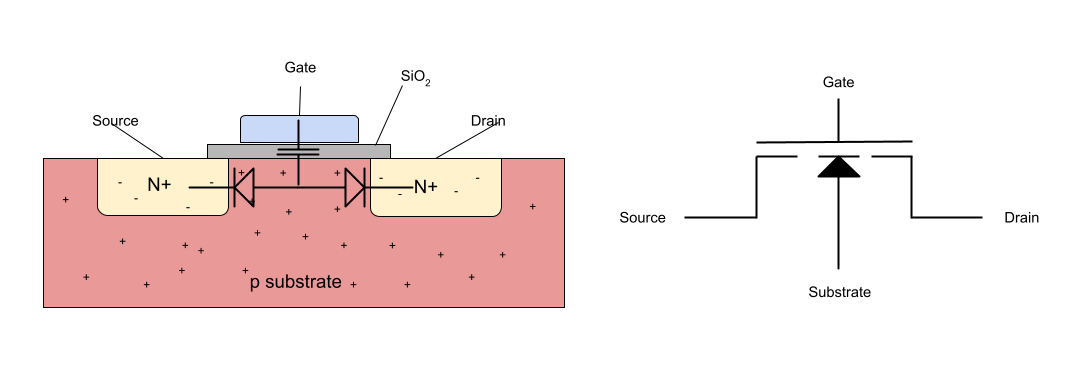

我们以增强型N沟道MOSFET为例进行说明。在N沟道器件中,器件的源极和漏极端子是设置在P型衬底中的N型半导体区域。N-P和P-N结有效地构建了两个反向偏置的二极管,可以阻断电荷流过器件。

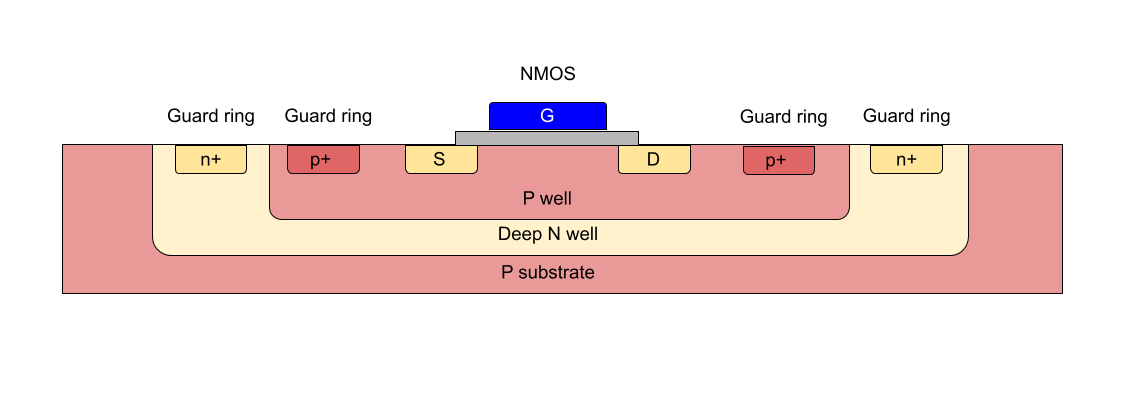

图1:在N沟道MOSFET中,器件的源极和漏极端子是设置在P型衬底中的N型半导体区域(来源:Pulsic)

栅极端子是一个导电板,它通过一层薄薄的SiO2绝缘层与P型衬底隔开。实际上相当于在栅极和衬底之间形成了一个电容器。

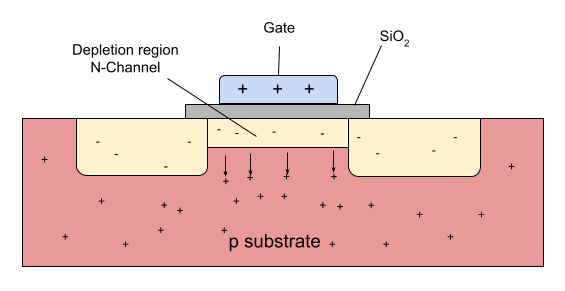

图2:栅极端子与P型衬底之间通过SiO2绝缘薄层隔开(来源:Pulsic)

在工作中,相对于衬底电位的正电位差被施加到栅极上。它通常与源极保持相同的电位,因此通常称为VGS。栅极上的正电荷排斥正电荷载流子(空穴),并吸引紧邻栅极下方P型衬底材料中的负电荷载流子(电子)。其效果是在栅极正下方创建一个耗尽正电荷载流子的区域,称为耗尽区。耗尽区多余的电子被诱导成N型区,或源极和漏极端子之间的N沟道。电子可以通过 N沟道从源极流向漏极,从而产生通过器件的电流。

在数字电路中,栅极电位在轨与轨之间切换,导致器件要么完全关断,要么完全导通,N沟道完全耗尽。这种完全耗尽的模式称为饱和。

在模拟电路中,晶体管通常工作在欧姆区,此时,流过器件的电流ID与VGS成正比。为了实现这一点,VGS要在导致部分耗尽的N沟道电位范围内工作。

在欧姆模式下,器件的增益对栅极和衬底之间的电位差非常敏感。衬底电位的微小变化都将对通过器件的电流产生很大影响。为了构建出能够按要求工作的模拟MOSFET电路,有必要在布局中插入一些特别的结构,以精细控制衬底电位。

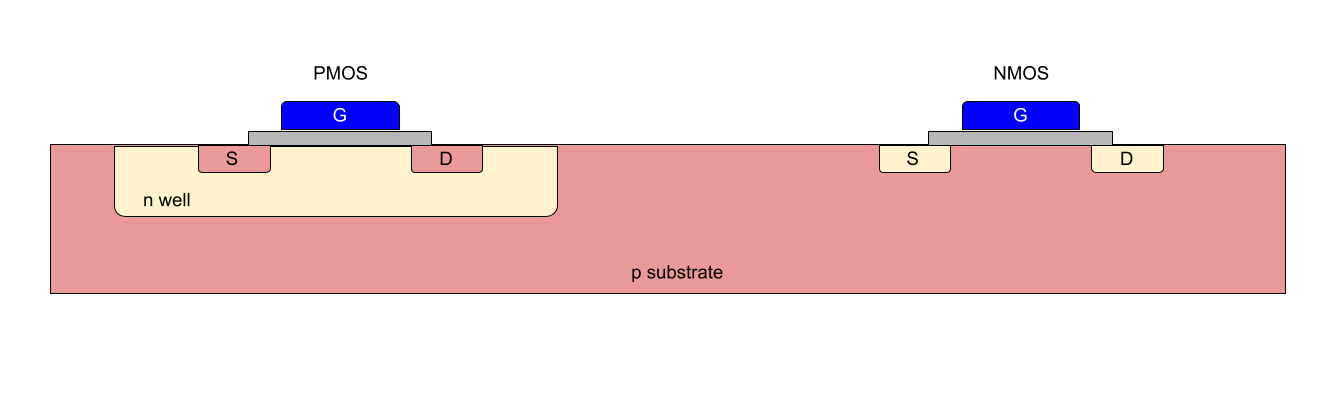

在大多数工艺中,主要采用三种MOSFET器件,即P型衬底中的N沟道器件(如上所述)、N阱中的P沟道器件,以及深N阱中的N沟道器件。

N-阱

大多数工艺都会先利用掺杂在整个芯片表面形成P型衬底,N沟道器件可以直接构建在这个 P型衬底之上。而P沟道器件则需要N型衬底来形成P型沟道。为了实现这一点,首先需要在将要制造P沟道器件的地方沉积出N型材料区域,这一N型区域称为N阱。

图3:N型区域包括沉积的N型材料,在这里可构造P沟道器件。(来源:Pulsic)

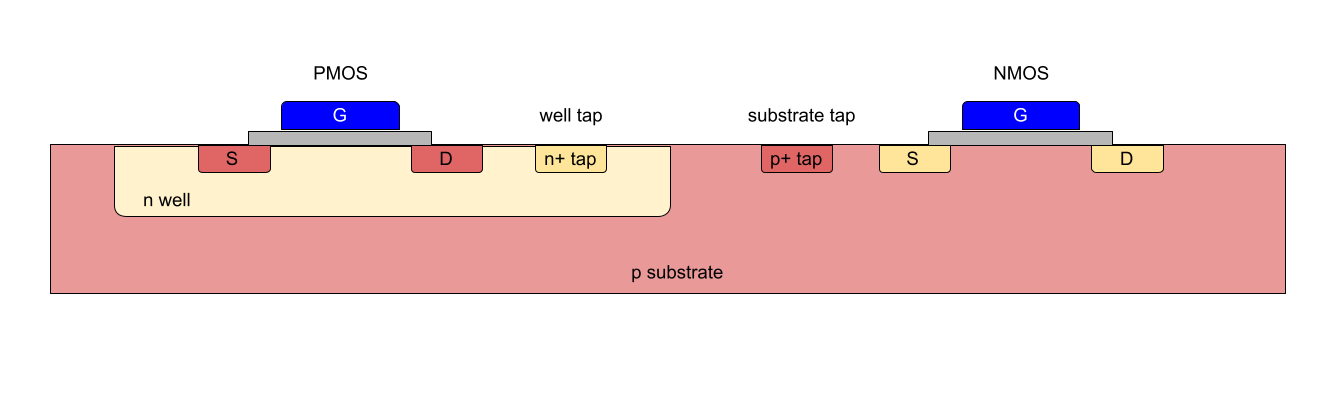

抽头

N阱会与电路的其他部分有效隔离,但在工作期间,N阱中会积蓄电荷。这些电荷会改变P沟道器件的VGS,从而改变电路性能。为了防止这种情况的发生,可以将N+“抽头”插入到布局中,让电荷流失,从而将N阱保持在正确的电位上。

阱中的N型材料电阻相当大,因此为了确保对电位的良好控制,整个区域中的每个N阱都需要多个抽头。类似地,将P+衬底抽头添加到P型衬底中以控制P型衬底中的电荷积蓄。通常,工艺设计规则手册(DRM)中将指定抽头间的最大距离以避免闩锁,但抽头仍然需要非常频繁地插入,才能确保模拟电路的良好运行。

图4:将抽头插入布局中以排出电荷。(来源:Pulsic)

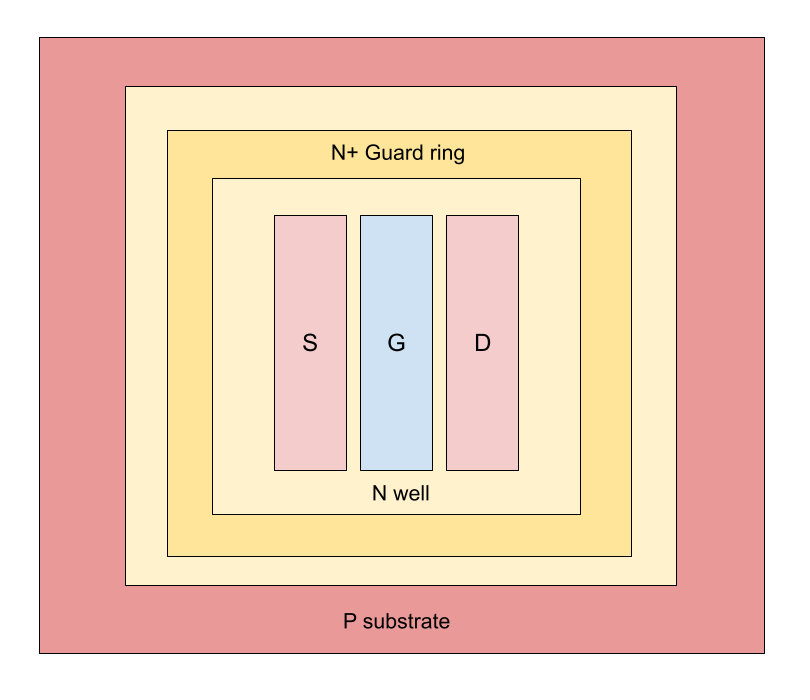

保护环

模拟设计常常利用“保护环”来扩展抽头结构。保护环是可以完全包围一组器件的大型抽头。通过在一组器件周围的阱/衬底中创建一个低电阻环,可以更有效地将器件彼此隔离。这样可以防止其他器件的电荷积累或波动电位影响到这组受保护器件的正常工作。

图5:保护环是完全包围一组器件的大型抽头。 (来源:Pulsic)

保护环的形状通常在金属1中重复,并引出多个触点,将金属1环与N+环连接起来。这样确保了保护环与电源或地之间的良好连接。增加保护环的宽度和触点数量可以进一步提升隔离度,但将以增加布局面积为代价。

保护环在混合信号设计中尤为重要,电路中敏感的模拟电路通常位于“嘈杂”的数字CMOS电路附近。在某些特别敏感的电路中,甚至需要将每个器件都置于其自己的阱中,并拥有自己的保护环;但大多数情况下,同一电路中的器件可以共用阱。一种常见的策略是在电路的特定部分周围创建额外的保护环。例如,用差分对来提供额外的保护,隔离其周围环境。

深N-阱

直接内置在P型衬底中的N沟道器件不能像其N阱中的P沟道器件那样有效隔离,这是因为尽管在器件周围创建了P+保护环,但保护环下方仍有一条电气路径供电荷流动。为了解决这个问题,可以构建深N阱来更有效地隔离这些N沟道器件。

图6:深N阱可以更加有效地隔离N沟道器件

在器件的P阱周围和下方构建一个N阱,N沟道器件在P阱中运行。P阱和深N阱都需要抽头,但在多数情况下,这两个阱都用保护环来保护。这意味着器件周围有两个环,这大大提高了器件的隔离度,但从布局角度而言,它需要的空间也更大。

设计阱、抽头和保护环时,还需要考虑其对器件匹配的影响。许多模拟结构(例如电流镜和差分对)都需要精确匹配不同器件的特性。在两个器件之间实现良好匹配的主要方法是尽可能地匹配其几何形状,包括器件周围的阱、抽头和保护环。另外,靠近保护环放置的器件将与放置更远的器件具有不同的特性。

对大多数设计人员来说,MOSFET布局的几何形状都由PCell/PyCell创建,但阱、抽头和保护环的位置和几何形状设计则需要设计人员的专业知识。大多数情况下,DRC和LVS检查会告诉设计人员他们错在哪里,但这些工具无法衡量最终布局的质量。因此,作为一个专业的布局设计人员,应该了解这些结构的作用,为什么需要它们以及它们对电路的影响。

(参考原文:Analog layout Why wells, taps, and guard rings are crucial)

责编:Amy Guan

本文为《电子工程专辑》2021年10月刊杂志文章,版权所有,禁止转载。点击申请免费杂志订阅