片上系统(SoC)无处不在,尤其是在服务于新兴细分市场的电子产品中,例如5G、自动驾驶汽车和人工智能。这些复杂的业务需要实时处理每秒数十亿次的操作。随着系统复杂性的不断提高,SoC设计团队承受着越来越大的压力,他们要以前所未有的更低成本和更短时间交付更高效的产品,而传统的设计方法和工具已达到极限。电子设计自动化(EDA)必须不断突破才能应对不断发展的SoC设计挑战。

SoC设计从集成步骤开始,期间必须完成所选知识产权(IP)模块的互联。SoC设计目前所面临的挑战是要在紧迫的期限内实现最佳功耗、性能和面积(PPA)组合,同时,控制工程成本。在传统的EDA设计流程中,每项任务(功耗、架构、测试等)都由一支超专业的工程师团队执行。要完成设计,不同团队之间必须进行紧密沟通和持续的信息交换。而每一次新迭代都会重新启动信息交换过程。因此,迭代次数越多,对项目最终成本和完成时间的影响就越大。

传统SoC集成流程之所以不可避免地产生多次迭代,是因为寄存器传输级(RTL)设计需要不断微调和逐步优化,直到RTL2GDS合成流程实现最佳PPA结果为止。另外,前代项目软IP核的设计复用率需要提高到较高的水平,才能将设计价值最大化,并使IP核和SoC成为现成的商品。因此,设计方法必须做出创新变革,彻底颠覆传统EDA范例和工具,才能完成当今SoC项目要求的更多任务,而又不会占用过多的工程资源。值得注意的是,大多数EDA创新预计都将在架构级别、在SoC集成期间以及RTL2GDS实施之前进行。

以下所述的创新方法将有助于应对SoC目前面临的挑战。

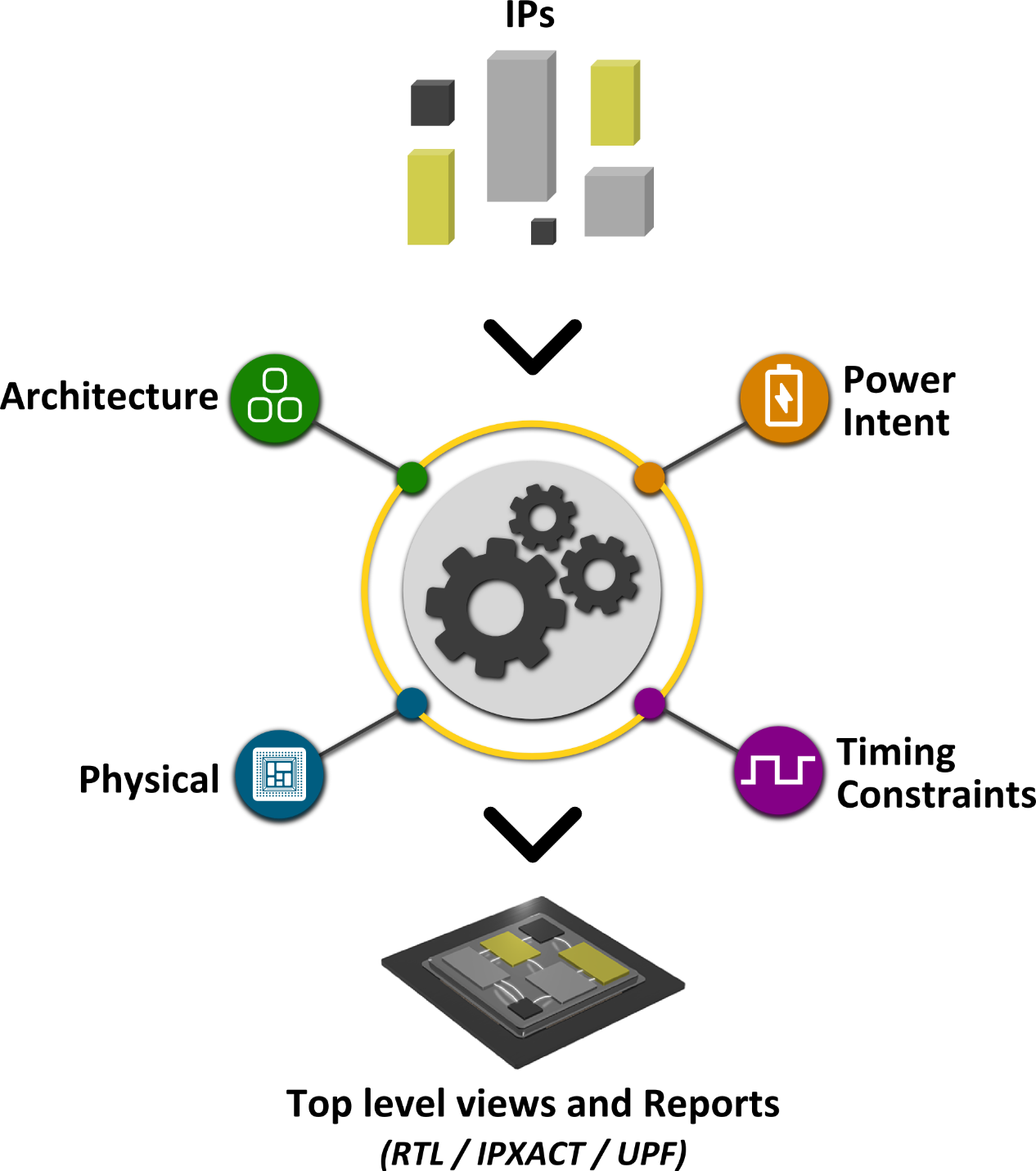

图1: 设计信息的综合处理(来源: DeFacto Technologies)

图1: 设计信息的综合处理(来源: DeFacto Technologies)

更早开始SoC构建过程

加速SoC构建过程需要EDA设计工具在处理设计信息时实现更高程度的自动化。本文介绍的解决方案包含了一个可容纳多种设计领域和格式的统一数据库。在SoC构建过程中,必须尽早考虑所有设计信息,包括RTL、时序限制、功耗、物理实现和测试。

在实际操作中,这种方法应允许非领域专家做出重要的设计决策。例如,CAD工程师或RTL设计人员将能够拥有构建从设计装配到合成第一个SoC配置的能力。

最大化设计复用率

为复杂的SoC构建可配置的IP子系统时,会消耗大量资源。因此,要降低SoC设计的总体成本,需要远高于传统的IP复用率;而实现这一点,则需要新型的设计复用方法和工具。在SoC集成过程中,EDA工具必须提供具有基本和高级设计提取功能的通用API。

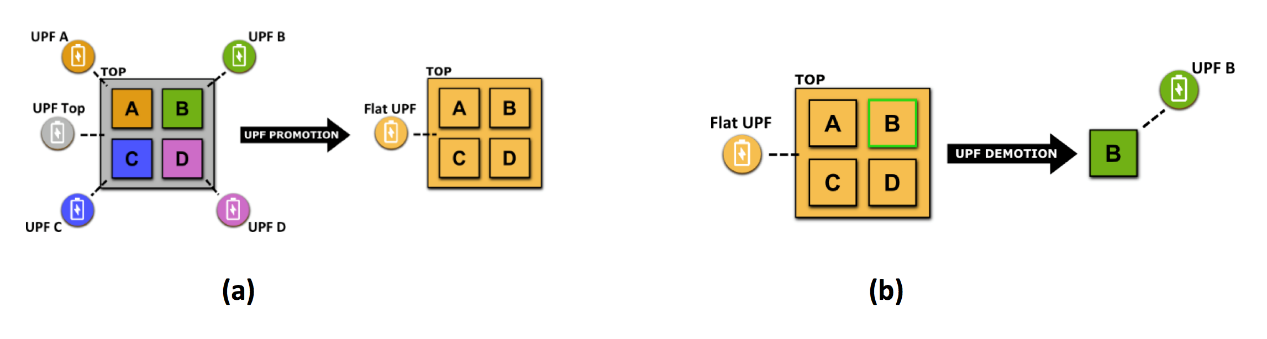

让我们以低功耗应用的SoC集成需求为例进行说明。电源架构或意图可以通过统一电源格式(UPF)数据库捕获。在进行组装或提升SoC级功率信息之前(图2a),不同模块的功耗信息被提取出来。传统上,功耗提取是一个繁琐的手动过程。但现在,UPF降级(图2b)正逐渐成为一个要求完全自动化的过程。

图2: SoC集成过程中的功耗设计复用。顶层功耗集成(a)来自于功耗设计提取(b)(来源: DeFacto Technologies)

图2: SoC集成过程中的功耗设计复用。顶层功耗集成(a)来自于功耗设计提取(b)(来源: DeFacto Technologies)

促进设计空间的探索

传统SoC集成方法的另一个缺点是自动化不足,不能探索设计空间并确定最佳PPA设计配置。手动运行多个假设场景会耗费过多工程资源,从而使设计团队无法获得最优解决方案。

配备了物理设计信息之后,EDA工具应通过在RTL创建不同的设计配置,以实现具有物理意识的SoC组装。这允许RTL检测和纠正以往设计人员只有在合成后才可能发现的问题,如连接性问题,其可能会令布局布线(P&R)变成一场噩梦。

让EDA工具更加智能化

AI及其衍生(尤其是机器学习,ML)应用正在不断扩展。在解决SoC设计难题时,EDA社群不应忽视ML算法可能带来的优势。从系统级到物理实现设计,每个EDA工具通常都基于复杂的算法构建,而与设计任务(模拟、形式验证、综合、DFT、P&R等)无关。现在关键就在于如何使此类算法与AI / ML兼容,并使其在运行大量设计项目时从大量可用的收集数据中获益。

让我们以一个简单的SoC顶层模块集成为例。AI / ML的典型输出应是能够实现优秀PPA的SoC配置最佳选择,例如更小的面积或CPU time的大幅降低。但没有真实的生产数据,体现不出AI / ML的价值。因此,EDA工具提供商与最终用户之间的紧密协作才是成功的关键因素。

总而言之,相比其他行业(例如机器人技术和医疗保健)采用AI / ML的步伐,EDA工具提供商的AI / ML计划显得尤为保守,但AI / ML对于EDA的重要性业界实不容忽视。

(参考原文:To Conquer SoC Design Challenges, Change EDA Methods and Tools)

责编:Amy Guan

本文为《电子工程专辑》2021年5月刊杂志文章,版权所有,禁止转载。点击申请免费杂志订阅