在芯片的制程工艺上,台积电、三星的竞争再次升级。台积电早就主动爆料已经在研究1nm工艺,不过其实际投产时间未定。三星的3nm GAE工艺却或许在2022年部署。

由贴吧和微博爆料可知,三星在近日举办的2021代工论坛上,展示了其最新的公共技术路线图。尽管初代3nm GAE工艺较预期晚了一年转入量产,但新路线图表明它可能仅供内部使用。同时作为3GAE的继任者,3GAP节点仍在官方路线图上,可知其有望于2023年实现量产。

(来自:微博 @科技芯时空)

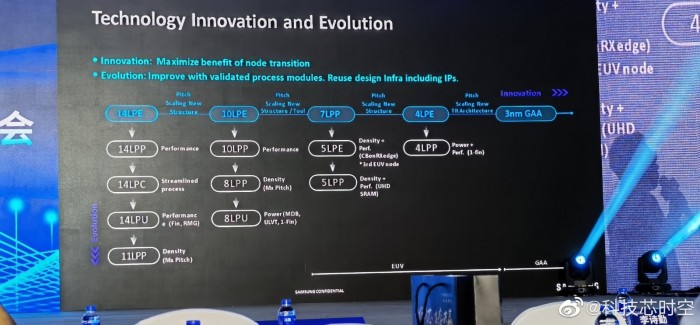

FinFET 技术方面,5LPP 和 4LPP 节点都是路线图上的新节点,分别将于 2021 / 2022 年开启大批量制造(HVM)。

GAA 技术方面,路线图中看不到 3GAE,但出现了 3GAP 。在与三星取得联系后,公司一位代表向 AnandTech 证实,3GAE 技术仍有望在 2022 年实现量产,但不是所有人都能够用上。

此外从 PPT 来看,可知基于 MBCFET 的 3GAP 工艺将于 2023 年的某个时候,转入大批量制造阶段。

三星发言人称:“至于 3GAE 工艺,我们一直在与客户进行商议,预计可于 2022 年实现量产”。

AnandTech 预计,之所以没有在公共路线图中出现,或许是 3GAE 仅适用于三星自家的 LSI 部门,就像其它一些早期节点那样。即便如此,该公司还是在 PPT 上提到了上一代早期节点。

据悉,三星最初于 2019 年 5 月宣布了基于 MBCFET 的 3GAE 和 3GAP 节点。 当时该公司承诺,与 7LPP 相比,3GAE 可提升 35% 的性能、减少 45% 的面积、同时降低 50% 的功耗。

然后,该公司宣布了 3nm PDK v0.1 的可用性,当时宣称将于 2021 年底开启 3GAE 的量产。然而最新消息称,受多方面因素的影响,三星已将之延期至 2022 年。

不过从好的一面来看,三星已于几周前完成了首批 3nm 测试芯片的流片,且宣布了与新制造技术兼容的 Synopsys EDA 工具。

AnandTech 指出,使用全新晶体管制造工艺,始终是一项艰巨的挑战。除了新的电子设计自动化(EDA)工具,厂商还需动用全新的 IP,预计后续可听到更多有关这方面的消息披露。

最后,尽管普通客户似乎要等到 2023 年,才会用上三星的 3nm 制程。但新发布的 4LPP 工艺,仍将于 2022 年满足大部分客户的需求。

由于 4LPP 依赖于熟悉的 FinFET 工艺,其面临的设计挑战,将较任何 3nm GAA 工艺要少得多。需要注意的是,三星已在 PPT 上,将其 5nm 和 4nm 节点,分别视作不同的工艺分支。

此前代工厂将 4LPE 视作 7LPP 的工艺演进,这或许是因为 4nm 提供了较 5nm 更显著的功率、性能、面积、以及成本优势(简称 PPAc),亦或存在其它实质性的内部变化(比如新材料、极紫外 / EUV 光刻等显著提升)。

责编:EditorDan