Intel最新2nm以下制程节点新突破

据台湾省经济日报消息,Intel高级副总裁兼中国区董事长王瑞近日对媒体表示,Intel 20A(业界的2nm制程)和Intel 18A(相当于1.8nm制程)已经流片(流片:是指像流水线一样通过一系列工艺步骤制造芯片,该词在集成电路设计领域,“流片”指的是“试生产”。)。这也是Intel在四年内快速发展五个制程节点的目标之一,此次流出的信息也备受外界瞩目。

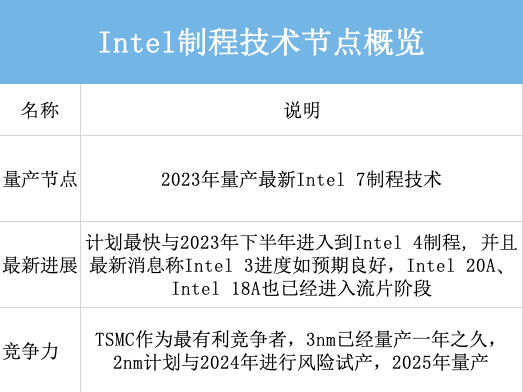

Intel近几年对于芯片制程工艺的发展令人叹为观止,规划从Intel 10制程开始,逐步有序进入到Intel 7和Intel 4技术节点,然后就是 Intel 3、Intel 20A 和最新的Intel 18A制程。目前Intel已经量产的最新技术是Intel 7制程,Intel 18A制程则预计2024年下半年就位。也就是说,现在举例2024年的下半年九月刚好18个月的时间,Intel预计在这18个月里攻克数个技术节点,进程之快颇令市场震惊。

资料来源:网络整理(经济日报等媒体),制表:电子工程专辑编辑

Intel 4 物理参数:密度是 Intel 7 的 2 倍

不妨来深入研究一下今年下半年就要上场的Intel 4制程,究竟是何方神圣。不难看出,Intel已经开始着手解决之前遗留下来的问题。首先要解决的密度问题,到了如此精细的工艺节点,不少业界人士均对于制程工艺铁律 “摩尔定律”和“登纳德缩放定律”开始起了动摇之心。

摩尔定律:集成电路可以容纳的晶体管数目在大约每经过18个月到24个月便会增加一倍

登纳德缩放定律:随着晶体管尺寸的缩小,其功率密度保持不变,从而使芯片功率与芯片面积成正比。

追溯到Intel之前发布的数据中,Intel 4的 Fin Pitch间距下降到30nm,是Intel 7的34nm的88%,而且Contac Gate Poly Pitch 也从原来的60nm缩减到50nm,Min Metal Pitch(M0)则降低了75%之多,从40nm降到30nm;HP Library Height的高度则减少了近乎一半,从原来的408h减少到140h,仅为Intel 7 的0.59倍。因此,Intel对外宣称,Intel 4的密度是Intel 7的2倍之多,当然业界更喜欢的说法是,在获得相同的芯片性能下,Intel4可以比Intel 7做出来的芯片尺寸缩小一半。

由于芯片的晶体管是二维结构,所以Intel的单个单元的计算方式是: HP Libnrary Height *Contact Gate Poly Pitch;按照如此计算方式,Intel 7制程是24408nm²,Intel 4制程则是12000nm²,纸面计算是Intel 7的49%。当然芯片内部各种电路结构有很多,不是每种结构都能用上述公式计算,所以Intel 4 的制程节点据官方称,相同单元的大小为Intel 7的77%。

决战2025,Intel放狠话,将重回领导地位

我们再把视野放到更远的 Intel 3、20A和18A制程节点,虽然官方还未透露出具体的性能参数,但是最新的消息是,Intel 3制程的进度也如预期良好,一扫之前市场传出的Intel 3制程节点技术开发出现延迟的谣言。

关于Intel Granite Rapids及Sierra Forest系列处理器,计划都将采用自家的Intel 3制程生产,并且先前的消息也支出,Intel 3制程可以进一步发挥 FinFET的优势和EUV的使用率。对于芯片密度、面积和功耗等等性能参数都会有大幅度的提升。

根据Intel高级副总裁暨中国区董事长王锐表示,全球需求晶圆代工的大客户中,十家有七家都在与Intel积极磋商合作业务,晶圆代工(IFS)也与43家潜在客户进行合作和晶圆流片生产。目前从Intel的动作来看,积极扩充产能和提升制程工艺节点技术,借助着美国芯片法案的辅助,Intel有信心在2025年,重回芯片制造领导地位。

责编:我的果果超可爱

参考资料:

《英特爾強碰台積電 傳2奈米研發突破》-经济日报

《Intel 4 Process Node In Detail: 2x Density Scaling, 20% Improved Performance》-Anandtech