制程节点与半导体尺寸似乎不再线性相关

各大论坛和社区经常拿Intel开玩笑,不管今年各个家的芯片是几nm的,intel家的一定是14nm,而且已经++++了好多年了,很多网友都对于intel戏称为“牙膏厂”。但是从FinFET之后单用nm来说说制程其实有些不妥的。

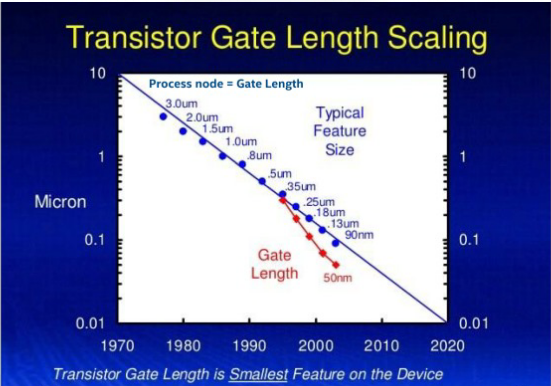

在过往制程的命名方式是依据芯片内部的闸极长度(Gate Length)而定,虽说闸极长度一定程度能代表芯片尺寸,因为闸极长度越小(沟道越窄)其内部的晶体管就越微缩,不仅耗电减低,其单位面积能塞进去更多的晶体管,同时散热、功耗和运算频率都有提升。但是单纯谈闸极的尺寸在现代工艺中未免有失偏颇。

FinFET(鳍式场效应晶体管)横空出世

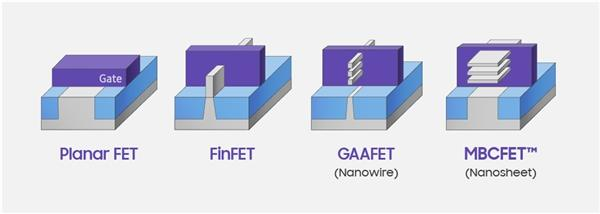

为了在晶体管中增加闸极长度,加州大学伯克利分校胡正明教授于1998提出FinFET(鳍式场效晶体管)技术,透过立体结构的闸极在有限尺寸中延长了闸极长度,Intel也于2011年开发出FinFET的新的工艺。

(图源网络,侵删)

过去制程是以晶体管闸极长度命名,但随着制程精进,这种命名方式已经无法反映芯片特性。并且在新的多鳍式的结构中,虽然其制程还停留在12nm或者10nm,但是其效率其实已经超越了传统意义上本代制程的极限。

PS:制程指的是,MOS管漏极和源级之间的沟道长度,就是下图中平面MOS中的黄线部分,这段距离会决定着工艺参数中的最小线宽选取。

新的FinFET结构可以有效减少其沟道长度,并且还没有减小其和闸极Gate的接触面积。虽然intel新的CPU“Rocket Lake-S”中采用了SuperFin技术,但是其命名制程按照自己的一套逻辑,无论其芯片性能已经超过了9nm或者8nm,但是没有达到7nm的密度和性能,那只会在后面加一个我们最喜欢的“+”,所以此次命名可能是 “10nm+”或者“10nm++”。

(图源网络,侵删)

摩尔定律不死,但是各家的命名也逐渐不再遵循

目前现今制程节点基本都是掌握在大厂手里,而且其进展也越来越缓慢,在尺度缩小的同时,工艺和机械误差的影响变得越来越大。在几百道工序中,一丁点的波动都有可能让整个元件报废,所以各家的技术路线出现了不同,也就出现了很多各家自己命名的“节点”。因为之前的平面的工艺节点已经不再适用,各家先进的工艺制程都在网三维空间进发,所以每家的命名规则也不是单一的一个尺寸参数所能概括的了。

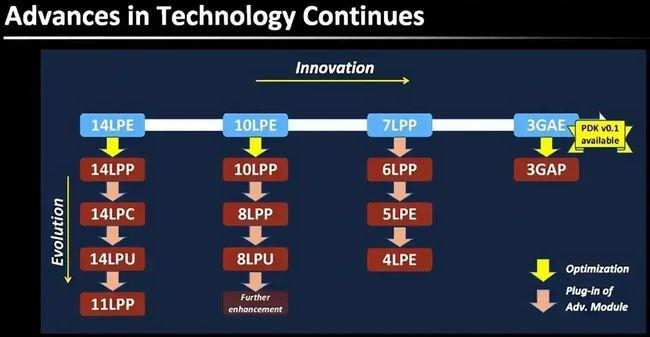

如下图所示,三星的工艺节点有着其特有的命名方式,并且其新的类似于FinFET技术是GAAFET(Gate-All-Around),并且早先发布了3nm的GAA技术已经在开发中。而后面的还有MBCFET等技术在不断的研发当中,在这些不同的工艺方式中,单纯讨论闸极长度也已经没有说服力了。

(图源网络,侵删)

无论是上述介绍的Intel家的10nm FinFET还是三星家的GAA技术,其在制程节点上都是或10nm或7nm甚至3nm。但是其制作出的元件性能本身早已超过平面的FET技术,所以我们会看到各家CPU或者GPU等等消费级、企业级的芯片还停留在10nm左右的时代,但是每一代新的芯片其性能都带了不少的提升。

(图源网络,侵删)

其实鼓吹制程是各家的宣传手段

纵观现在各大手机厂商,发布会从来都是大谈特谈7nm、5nm等,不禁让广大消费者觉得似乎芯片制程越小就越厉害,5nm一定会“吊打”7nm的,并且似乎那家抢先发布了新节点做的手机,就是占领了性能高地。不能说这种思想完全不对,新的工艺节点是有着明显的性能提升,但是一味鼓吹和不谈性能就单纯比较,未免有失偏颇。

而且每家命名方式都不统一,如果我命名为10nm的芯片各项参数已经比你7nm的还要好,你能说你的7nm一定比我的好吗?所以,小编在此的分享是希望广大网友不要单纯看那个一维的制程数字,因为现在是3D工艺的时代,一个nm的长度单位是远远难以概括芯片内部纷繁复杂的三维结构的。

责编:我的果果超可爱

参考:

[3].半導體製程怎麼命名比較好?Intel:遵照摩爾定律走就對了

[4].Intel Node Names - Read more about this on SemiWiki

- test

- test