在半导体行业不断追求更高性能和效率的背景下,集成技术的进步显得尤为重要。在这一领域,imec作为全球领先的纳米电子和数字技术研发中心,持续探索前沿技术解决方案。在慕尼黑ITF SEMICON Europa 2024上,笔者采访了imec的高级研究员兼3D项目总监Eric Beyne,以了解更多有关imec为工业界准备的新型2.5D和3D集成方法的信息。

2.5D和3D集成的研究主要是为了克服内存屏障,即计算性能受限于内存单元和处理单元之间相对缓慢的数据传输。这一瓶颈促使人们努力采用不同的方法,将内存堆栈放置在更靠近芯片的位置,而这些方法不可避免地需要在硅中介层上对不同的裸片和内存单元进行异构集成。

“我们需要芯片之间横向互连的技术,我们有时称之为2.5D。”Beyne说,“我们需要3D集成,在3D集成中,你可以利用裸片的整个表面进行垂直互连。当你的主要目标是芯片之间的高容量和快速I/O时,这种方法会更加有效。”

2.5D研究

2.5D技术还受到芯粒(Chiplet)趋势的推动。芯粒是由不同制造商或同一公司内不同团队开发的集成电路,通过标准总线接口——例如高带宽内存(HBM)或通用芯粒高速互连(UCIe)进行通信。当需要连接两个或多个芯片(或芯粒)时,需要在衬底上增加一个区块。根据所使用的标准,这可能是HBM或UCIe接口块,带有超细间距重分布层(RDL)互连或硅中介层互连,以促进与该接口块的传输。

Imec公司高级研究员兼3D项目总监Eric Beyne

“我们一直使用硅中介层。”Beyne说,“但大约10年前,我们开始更多地关注硅桥。现在,我们的方法是使用细间距RDL优先技术,并在其上焊接芯片。”

据Beyne介绍,这项研究涵盖两个领域。一个是超细间距RDL,imec正朝着镶嵌RDL技术的方向发展,以实现500nm的线和空间。这比目前业界使用的2μm最小线和空间尺寸小得多。使用有机衬底技术,这种500nm线空间连接技术可以取代一些硅中介层。

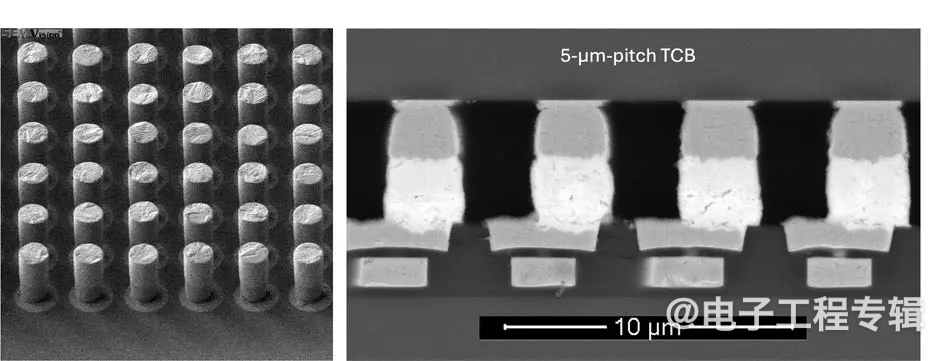

“在这些超细间距连接上组装芯片应遵循缩放定律,因为凸块阵列与芯片之间的互连间距有关。”Beyne说,“我们主要关注微凸块技术,我们称之为嵌入式微凸块,高度只有几微米。我们可以缩小到5μm的间距(图1)。”

Beyne表示,使用2.5D技术(相对于3D技术)有两个最大的缺点,一是延迟时间更长,二是需要更多的电力。不同芯片(或芯粒)之间通信所需的接口块会带来延迟,而较长的线路传输则需要更高的电压支持。

图1:直径2μm、间距5μm的微凸块。(来源:imec)

3D SoC研究

3D集成不需要额外的接口,不同的单元之间的通信就像有一根线将它们连接起来一样。也不需要改变电压。3D堆叠可带来更高的性能,Beyne说。但也存在一些缺点——包括设计流程需要改变。

“要实现真正的垂直集成,就必须对3D堆叠进行协同设计。”他指出,“可以将系统划分为三个维度,然后执行一次电子设计自动化(EDA)操作,对所有单元进行布局和布线,并在没有接口开销的情况下进行优化。”

重新考虑设计流程并不是使用3D集成时出现的唯一问题,另一个问题是功耗墙。随着越来越多的器件被堆叠在一起,单位面积上的功率密度增加,这使得系统的散热变得更加困难。

“我们需要能够以更高的功率密度从更大的系统中吸收热量的子系统,但与此同时,我们需要通过从衬底到封装再到器件的一小块区域,为3D堆栈中的器件提供更多的功率(即电流)。”Beyne说。一种解决方案是向封装提供更高的电压,并使用集成电流稳压器电路将更高的电压转换为封装内甚至芯片和中介层本身的较低电压。

Beyne解释说,从设计的角度来看,芯片是由不同的IP块组成的。在这些IP块中,可以在不同级别进行互连——在子单元级别、标准单元级别,一直到晶体管级别。

“从邦定路径、外部I/O连接,到全局互连级别,到中间互连级别,最后到本地互连。”Beyne说,“相应地,如果在互连层次结构的不同级别上拆分系统,则必须在第三维度上采用越来越高的互连密度。”

根据不同应用,堆叠组件可以在1、2或3级缓存中拆分。在每种情况下,为了成倍地提高互连密度,3D连接需要更小的互连间距。

没有一种技术能够涵盖所有这些不同的可能性,因为它们在规模上存在数量级的差异。“在imec的3D项目中,我们活跃于其中的许多领域,主要几种在裸片到晶圆的混合邦定、堆叠和微凸块堆叠、晶圆到晶圆的混合邦定和纳米硅通孔(TSV)集成。”Beyne说。

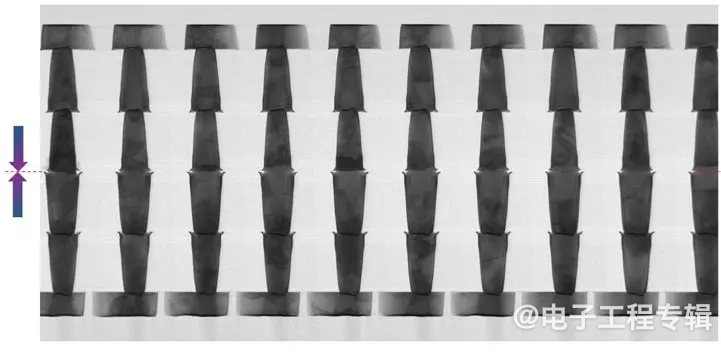

imec曾在2023年12月的IEDM会议上报告称,该公司已将300mm晶圆上的高产量混合邦定缩小到400nm间距,这要求整个晶圆的叠加精度优于100nm(图2)。

图2:400nm间距晶圆到晶圆邦定。(来源:imec)

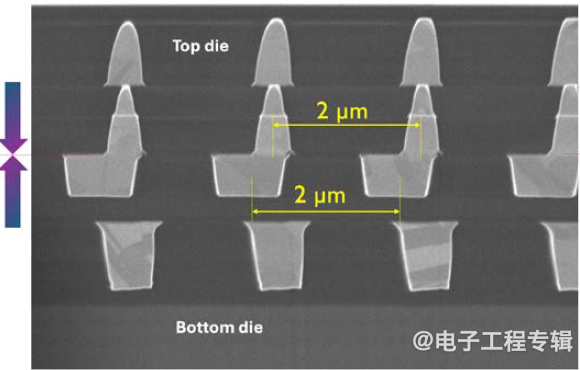

裸片到晶圆的混合邦定涉及的问题更多一些,因为裸片必须在不损坏凸点结构的情况下进行分割。分割涉及光刻工艺后的划线和折断、机械锯切或激光切割。“还必须在没有颗粒污染的情况下拾取和放置裸片。”Beyne说,“我们已经能够将该技术缩小到2μm间距(图3)。”

图3:2μm间距裸片到晶圆邦定。(来源:imec)

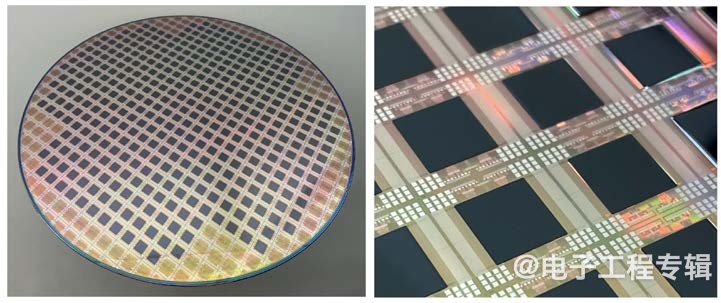

Beyne表示,imec正努力保持在行业技术应用的前列。“我们已经在晶圆到晶圆和裸片到晶圆邦定方面取得了进展(图4),但我们还将继续探索背面纳米TSV邦定和微凸块组装领域。所有这些不同的技术结合在一起,使我们能够致力于实现复杂3D集成系统的宏伟愿景,将所有这些异构集成结构都结合在一起。”

图4:裸片到晶圆邦定。(来源:imec)

(原文刊登于EE Times欧洲版,参考链接:imec: New Methods for 2.5D and 3D Integration,由Franklin Zhao编译。)

本文为《电子工程专辑》2025年3月刊杂志文章,版权所有,禁止转载。免费杂志订阅申请点击这里。