FD-SOI(全耗尽绝缘体上硅)是一种先进的半导体制造技术,它结合了传统的CMOS技术与绝缘体硅(SOI)的优势,提供了一种具有超低功耗、高性能和高集成度的解决方案。

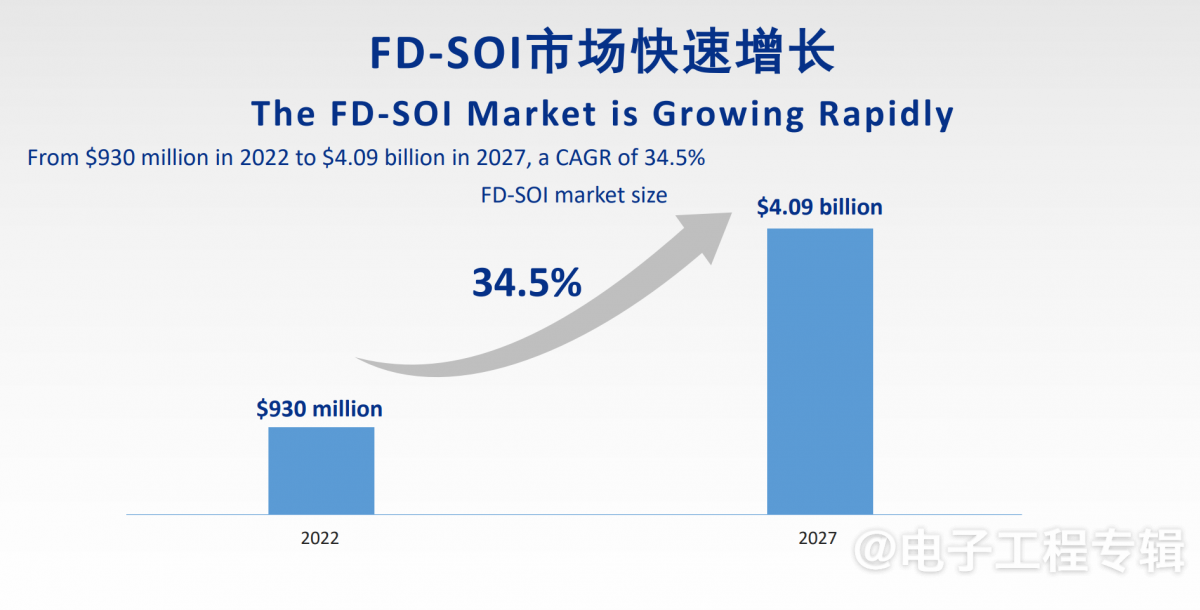

近年来,FD-SOI技术实现了快速增长。数据显示,市场规模将从2022年的9.3亿美元增长至2027年的40.9亿美元,年复合增长率为34.5%。

一些国际巨头正在推动这一技术的发展。2024年3月,意法半导体和三星电子联合推出了18nm具有嵌入式相变存储器的 FD-SOI 技术(ePCM),更大的内存、模拟和数字外设的集成度更高等优点都显著提高了芯片性能并降低了功耗。首款基于该技术的全新 STM32 MCU将于 2024 年下半年开始送样,并计划于 2H2025投入量产。

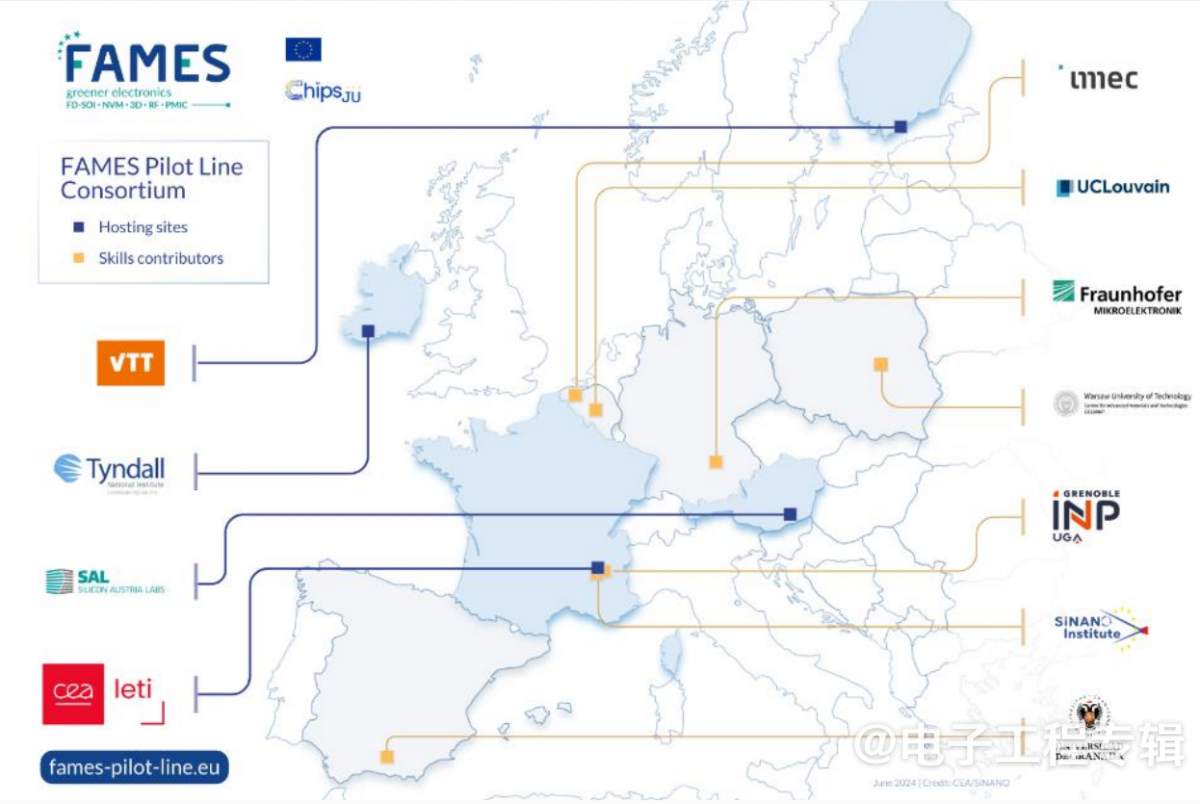

与此同时,在《欧盟芯片法案》的推动下,法国CEA-Leti也于今年6月宣布了10nm和7nm FD-SOI试验线(FAMES Pilot Line),并且获得了整个电子系统价值链中价值链中至少有 43 家公司的正式表示支持。

在中国,FD-SOI市场预计将在未来几年内保持快速增长,特别是在物联网、汽车电子和工业控制领域。中国政府对半导体产业的支持和本土技术公司的发展,共同推动了这一技术在中国的快速发展。在日前举办的第九届上海FD-SOI论坛上,进行了两场关于FD-SOI的讨论,来自国内外的重磅嘉宾们分别就FD-SOI工艺的技术优势、发展趋势以及设计实现进行了精彩分享。

上午场圆桌论坛主题《FD-SOI工艺的技术优势和发展趋势》

主持人(左一):戴伟民,芯原股份创始人、董事长兼总裁

嘉宾(由左至右):

Handel Jones,IBS 首席执行官

Ruby Yan,格罗方德产品线总监

John Carey,意法半导体射频与通信部总监

Jinha Park,三星电子18FDS工艺集成与项目经理

James Zhang Hongliang,Soitec 边缘与人工智能部门高级业务发展经理

下午场圆桌论坛主题《FD-SOI 的设计实现》

主持人(左一):戴伟民,芯原股份创始人、董事长兼总裁

嘉宾(由左至右):

Ying Zhao,Dolphin Design 亚洲区销售总监

朱炯,芯原股份设计实现高级总监

曾毅,芯原股份无线 IP 平台高级总监

成飞,至成微科技 (浙江) 有限公司首席执行官

凌峰,芯和半导体科技 (上海) 股份有限公司董事长

22nm之后,还有必要推出12nm吗?

众所周知,FD-SOI工艺停留在22nm已经很久了,直到意法半导体和三星联合推出18FDS才打破了这一沉寂。为什么选择18nm而不是12nm,其中一个原因是基于意法半导体MCU产品有明确市场的前提下。

而另一个原因,是工程师致力于开发适用范围最广的方案。三星电子18FDS工艺集成与项目经理Jinha Park表示,“18nm同样也是FD-SOI技术的关键节点,且推进效率较(12nm)高,适用于广泛的应用场景。”

除此之外,目前有明确进一步发展更先进工艺的,只有格罗方德的12FDX(12nm)。

格罗方德产品线总监Ruby Yan在早先的演讲中提到了FD-SOI的“next”(下一代)工艺,即12nm。她表示,目前公司关于FD-SOI所有的研发进展和与客户之间的互动,都集中在12nm技术上。

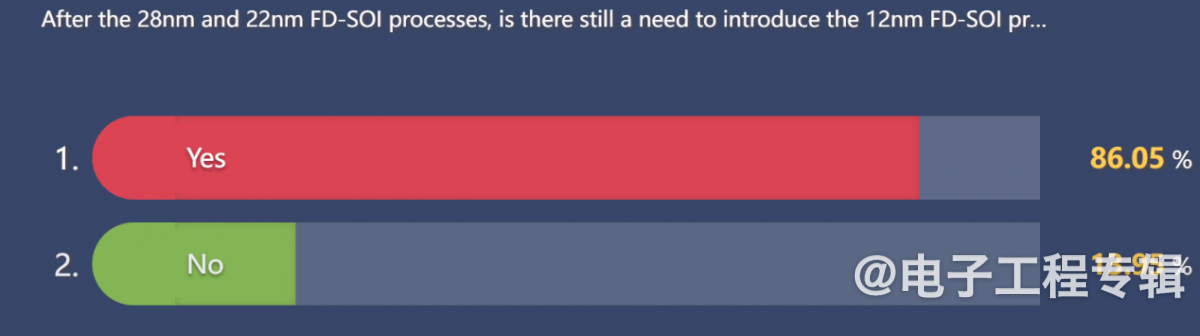

戴伟民问到:“在到达22nm之后,FD-SOI工艺是否有必要继续推进到12nm呢?”从现场观众投票来看,继续发展12nm FD-SOI的支持率达到86%。

“12nm节点实际上是double pattening(双重图形技术)能做到的最小节点,它确实带来了相应的益处。若考虑到客户对于产品价格的接受度,那么12nm技术就是下一代FD-SOI工艺的最佳选择。”戴伟民补充道,“有的时候我们选择FinFET是因为没有其他更好的选择,而12nm FD-SOI的成本其实和28nm CMOS Bulk相差无几,还能实现比7nm FinFET更好的性能和功耗。”

那么格罗方德的12nm FDX究竟什么时候会来?

“许多合作伙伴都了解我们在12nm技术上的进展。”Ruby Yan表示,“目前我们PDK1级的流程设计套件计划在2026年底推出,而2027年的目标是将此提升至产品层面。”目前格罗方德也在评估哪些设计合作伙伴对这项技术特别感兴趣,并希望与他们合作,以确保能够共同研发出成品。

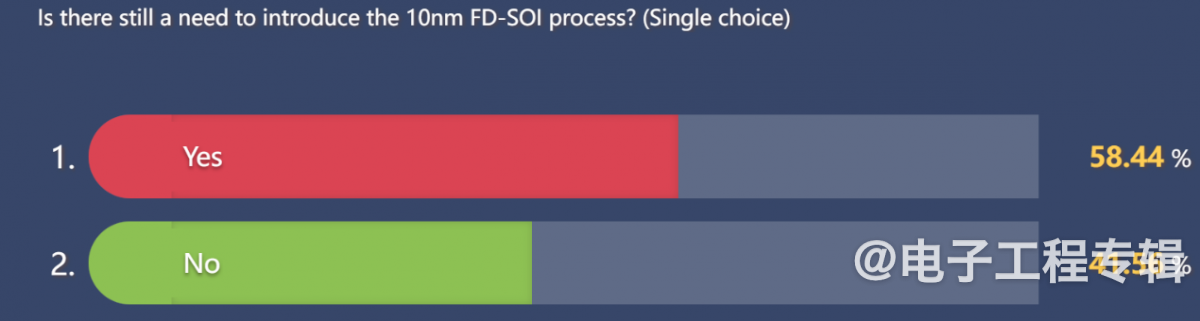

那么问题又来了,12nm之后是否还有必要做10nm?要知道下一步做10nm或8nm就需要triple patterning(三重图形技术)来实现了,成本会是一个很大制约的因素。从现场观众投票也能看出,对于进入10nm的支持率大幅下降,仅有58%。

这样看来,CEA-Leti推出10nm和7nm试验线,是否有点过于激进?对此Soitec 边缘与人工智能部门高级业务发展经理James Zhang认为,为了持续推进FD-SOI技术,业界需要制定一个技术路线图,“我们不能永远停留在28、22nm的水平,整个行业要为12、10nm或更先进的工艺做好准备。这是市场需求决定的,也是欧洲(EETC编按:Soitec和CEA-Leti均位于欧洲)投入大量努力研发FD-SOI技术的原因。”

James Zhang介绍到,FD-SOI大约在30年前从CEA-Leti开始研发,随后这项技术转让到Soitec。如今AI已经成为业界热门话题,FD-SOI的发展也需要更多考虑对AI功能的支持。“在CEA-Leti对前沿技术的突破之下,我们是有可能实现7nm工艺的。”

戴伟民补充了一点,如果要与数字芯片实现高度集成,22nm FD-SOI工艺的密度是不够的。“尤其是当前一些AI芯片对数字工艺的要求极高。所以尽管FinFET在RF上的表现远不如FD-SOI,但很多厂商仍旧选择前者。如果12nm FD-SOI早一点出来,很多芯片设计公司甚至不选择FinFET、不用EUV,就能达到同级别7nm的性能。”

IBS 首席执行官 Handel Jones对此表示认同,“我们需要更先进的工艺技术,因为许多公司都希望降低功耗。例如微软收购了多家AI技术公司,它们需要更高算力的硬件支持以推动生成式AI技术的发展。”

此外Handel Jones还提到功耗敏感的可穿戴设备,还要求完善的IP生态系统以支持其围绕应用进行设计,为什么FD-SOI的发展速度相对缓慢?就是当前生态系统狭窄造成的,应用不足造成产能需求小。“虽然目前呈现增长趋势,但整个行业还不成熟,若要实现12nm量产,FD-SOI行业必须进一步提升产能。有市场有需求,才有投资市场;当这些局势都不理想时,投资就会趋于保守。”

部署新的存储技术:MRAM/RRAM/PCM

随着 5G、人工智能 (AI) 和智能汽车等新兴应用的快速迭代,市场在速度、功耗、容量、可靠性等方面对数据存储提出了更高的要求。新兴的存储技术旨在将 SRAM 的开关速度与 DRAM 的高密度特性集成在一起,并具有闪存的非易失性。

在第二个问题上,大家讨论了MRAM和RRAM的潜力,由于这类新型存储技术在14nm FinFET工艺以下面临着巨大挑战,因此业界也在积极寻找20nm以下的替代解决方案,这也是FD-SOI被拿出来比较的原因。相较于业界较常提及的MRAM和RRAM,PCM被谈到的次数较少,但意法半导体为何选择了这一路径?

意法半导体射频与通信部总监John Carey表示,在方法选择上,意法更倾向于寻找一种有效且可靠的方法。“因此我们选择了PCM(相变记忆存储),因为它可以实现各功能之间的良好平衡。例如,通过将这些功能结合,我们可以获得稳定性、可测试性和耐用性,同时保持良好的单元尺寸。”

就PCM的表现性能而言,它具有出色的鲁棒性,对磁场不敏感。同时也可以实现28到18nm的平衡。意法半导体在PCM技术上已经投入了多年,可以达到车规级水平,对其他市场也有积极作用。

格罗方德的选择不太一样,他们首先选择做MRAM,随后转向RRAM。Ruby Yan表示,这两种技术在业界使用得更广泛,能耗更低,也是公司生态系统合作伙伴中选择更多的。“我们优先考虑的是低功耗、低漏电流的IoT应用方案,所以这两种更适合我们。”

至于MRAM和RRAM的对比,Ruby Yan认为MRAM在抗磁场能力方面更强且具备耐久性,汽车行业对此反馈积极,格罗方德也会利用这一点来进一步完善车规级产品线。而RRAM提供了适合消费电子的、成本更低的解决方案,同时在扩展性和尺寸方案也具有竞争力,格罗方德已经做好投产准备。

James Zhang表示,RRAM除了成本上的优势,在能耗表现上也非常优秀,更适合IoT应用。“当然RRAM也有自己的劣势,尤其是对于一些需要频繁重写的应用来说,可能不是一个最佳选择。对车规级等可靠性要求更高的应用,MRAM和PCM确实是更适合的选择。”

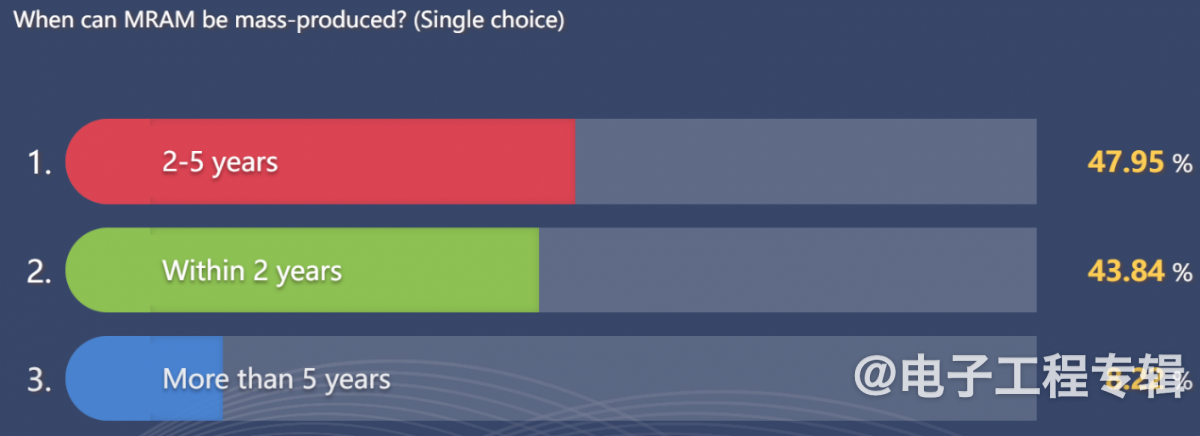

在针对嵌入式MRAM(eMRAM)何时能实现量产的问题上,现场观众大部分认为会在2年内或者2-5年。

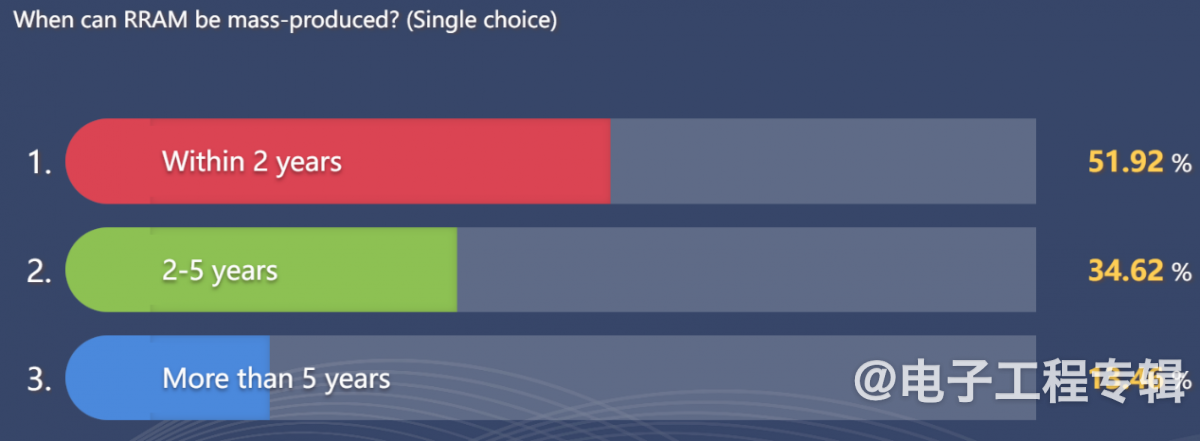

在针对嵌入式RRAM(eRRAM)何时能实现量产的问题上,现场观众大部分认为会在2年内。实际上,MRAM是先引入的一项技术,量产时间落后于后来者RRAM的原因,戴伟民认为这取决于其关注的具体应用,“比如RRAM用于迭代更快、用量更大消费电子领域,同时台积电非常重视RRAM技术。”

车规级产品是不是FD-SOI的出路?

2023 年 11 月,格罗方德分享了其在 22FDX 工艺方面的最新进展,包括对汽车芯片的支持。那么汽车应用会不会是FD-SOI技术的突破口呢?

John Carey认为,可靠性和能效对于新能源汽车来说至关重要,借助FD-SOI在低漏电流方面的优势和Body Bias技术,可以更有效地对电动汽车进行能源管理,“甚至优于FinFET。由于FD-SOI的应用没有达到一定规模,所以汽车电子中的应用比例也不高,也导致了各种各样的问题。未来我们希望有更多与FinFET技术集成的FD-SOI方案,能出现在数字芯片或是毫米波雷达中,这样能够同时实现更好的成本和性能。”

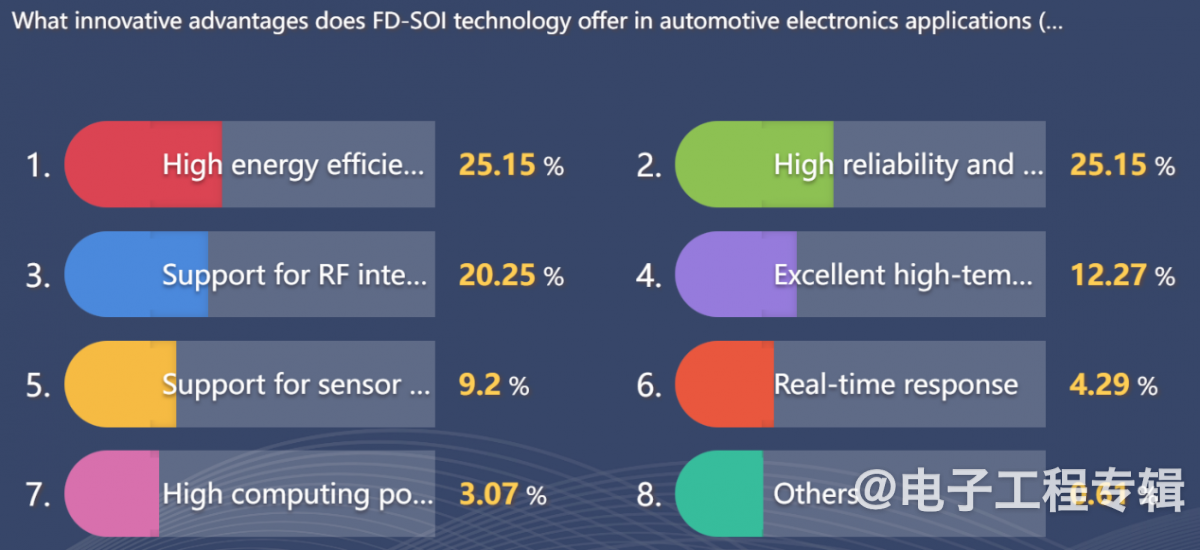

在汽车电子领域,哪些创新性优势是FD-SOI能够提供的?现场观众选出的前三名分别是高能效和低功耗、高可靠性与系统安全以及支持射频集成。

FD-SOI在Wi-Fi 6/7和GNSS领域的应用

新一代 Wi-Fi 技术 ax (6) 和be (7)的推出,代表了业界对无线通信算力的需求不断增长,虽然射频带宽被增加了(80MHz → 320MHz),但仍然需要高度集成、经济高效的大规模单芯片 SoC。在这个领域,FD-SOI 技术带来的优势包括更低的功耗、更高的射频/模拟集成度、来自 Body Bias 的弹性计算能力以及降低 NRE 总投资,可以满足多样化的终端芯片需求。

此外,索尼发布了采用22FDX的低功耗GNSS SoC,博世发布了基于22FDX工艺设计的77G毫米波雷达芯片,都代表了FD-SOI技术在无线应用领域具有很大的市场前景。

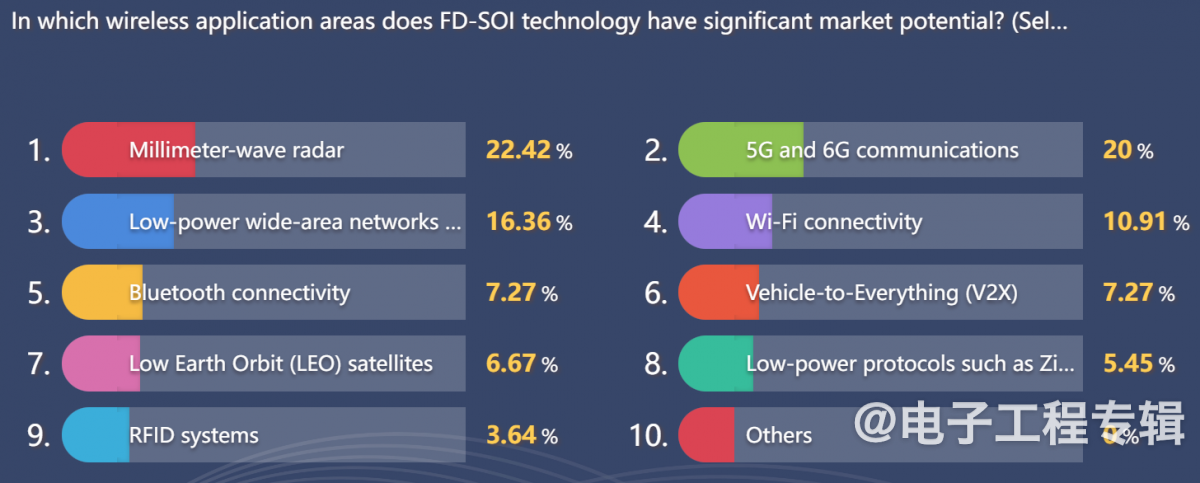

在关于FD-SOI技术在哪些无线应用领域具有很大的市场前景的问题上,现场观众选出的前三名分别是毫米波雷达、5G/6G通信、低功耗广域网。

Jinha Park表示,5G和6G拥有广泛的应用场景,且对于设备结构要求高,FD-SOI技术在其中能充分发挥其优势。此外在低轨道卫星应用和低功耗广域网方面方面也具备低功耗优势。

James Zhang指出,28nm FD-SOI的频率已经达到300GHz,22nm则超过400GHz,这令FD-SOI非常适合5G/6G以及汽车雷达应用。“同时自适应Body Bias技术带来更多降低功耗的空间。”

在上午场的最后,戴伟民强调了Chiplet技术和FD-SOI的结合,也就是所谓的“两条腿走路”观点。

用FD-SOI做独立芯片听起来不错,但“因为在芯片中的某些模块中,其实并不迫切需要FD-SOI工艺。对于迫切需要建立生态系统的FD-SOI来说,与生态系统更成熟的FinFET分工合作或许是更好的选择。” Handel Jones说道,“Chiplet技术的最大特点是不同工艺的IP核复用带来成本降低,FD-SOI可以抓住这个机会建立自己的生态系统。”

Handel Jones强调,抢先建立这样的生态系统对于中国来说尤其重要,因为可以在一个全新的竞争力领域实现领先。例如在可穿戴设备等应用上,与西方国家主导的FinFET分庭抗礼,占据一席之地。“未来脱钩可能变得严重,但我们已经观察到中国半导体市场的高速增长。我认为中国可以通过建立FD-SOI生态系统来适应这一趋势,如果有自己的Foundry来实现FD-SOI产品的生产就更为理想,我对中国很有信心。”

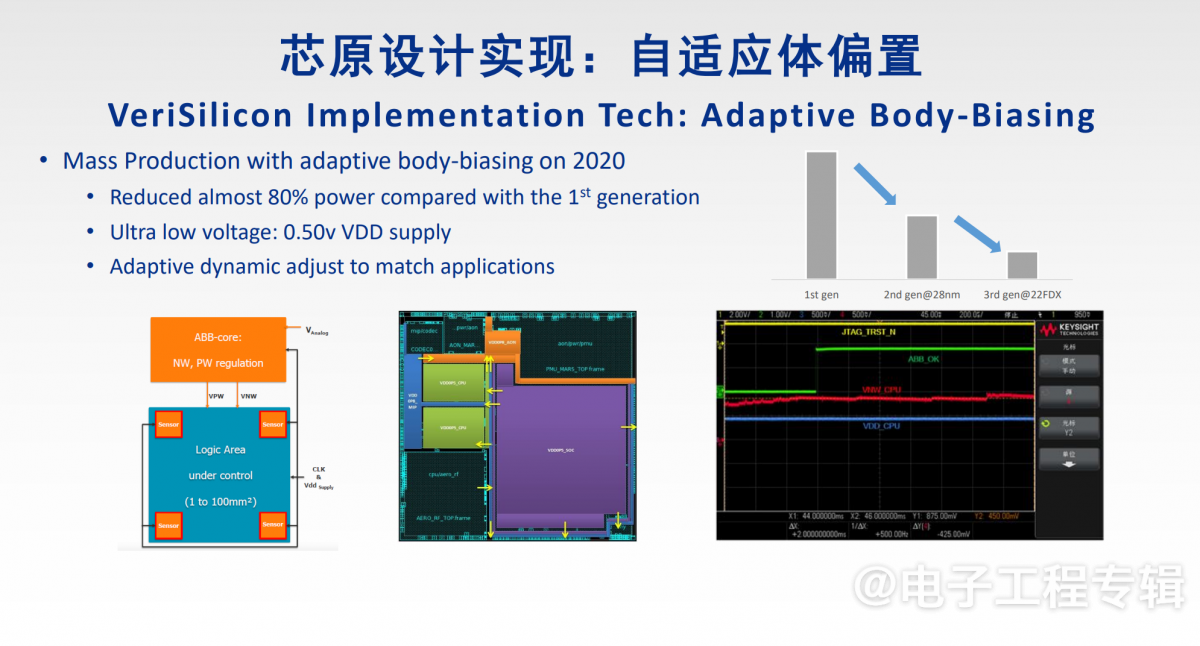

体偏置技术(Body Bias)到底是什么?

下午场的讨论主要集中在设计实现,如何体现FD-SOI的优势?IP厂商、设计厂商谁先来破局是一个问题,戴伟民首先邀请芯原股份设计实现高级总监朱炯详细介绍了Body Biasing技术。

朱炯表示,如果从传统的bulk工艺迈入到新的FD-SOI工艺。可以把传统bulk 工艺比喻为在开一辆汽车,可能有不同品牌、不同性能、不同速度。“进入到FD-SOI之后,就像在开一辆驾驶舱里有很多按钮的超级跑车,给你带来了各种设计灵活度。这辆跑车还配了氮气加速功能,对应到芯片就是body biasing技术。”

开车控制速度是靠油门,油门对应芯片电压,通过调节电压去控制芯片速度。而氮气加速是独立于工作电压之外,另一个可以加速或减速的新途径。如果需要保持恒定速度,那么氮气加速开大一点,油门就可以少踩一点。“这就是Body Biasing带来的动态功耗节省。节约油耗,就是节约芯片的主要功耗。” 朱炯说道。

氮气加速可以让车跑得更快,也可以跑得更慢,这就衍生出forward body basic和reverse body basing。如果人为对这个阀门进行控制,或者设定一个固定的值来控制它,那就衍生出Fixed Body-Biasing概念——让氮气加速以一个恒定的速度喷射,控制者的油门在该基础上做其他调整;而Adaptive Body-Biasing概念中的A,就像一个AI小助手,帮助你在查看这辆汽车在公路上的路况和天气,以此决定氮气加速应该开得更快还是更慢。

“这对于视频监控一类的IoT应用尤为重要,因为这类设备不需要Allways on,而是在需要启动时才全力加速。Dynamic Power和Leakage Power是不一样的场景。”戴伟民补充道,智能眼镜等应用也是同理,有时需要高性能运算,有的时候只需待机,“对于这类应用,芯片厂商在流片之前往往要预留很多buffer以备不时之需,也因此导致流片时间加长。Body-Biasing技术可以在Typical table条件下流片回来后,用软件调节控制芯片设备,无论怎么‘飘’都可以拉回来。这是FinFET工艺做不到的。”

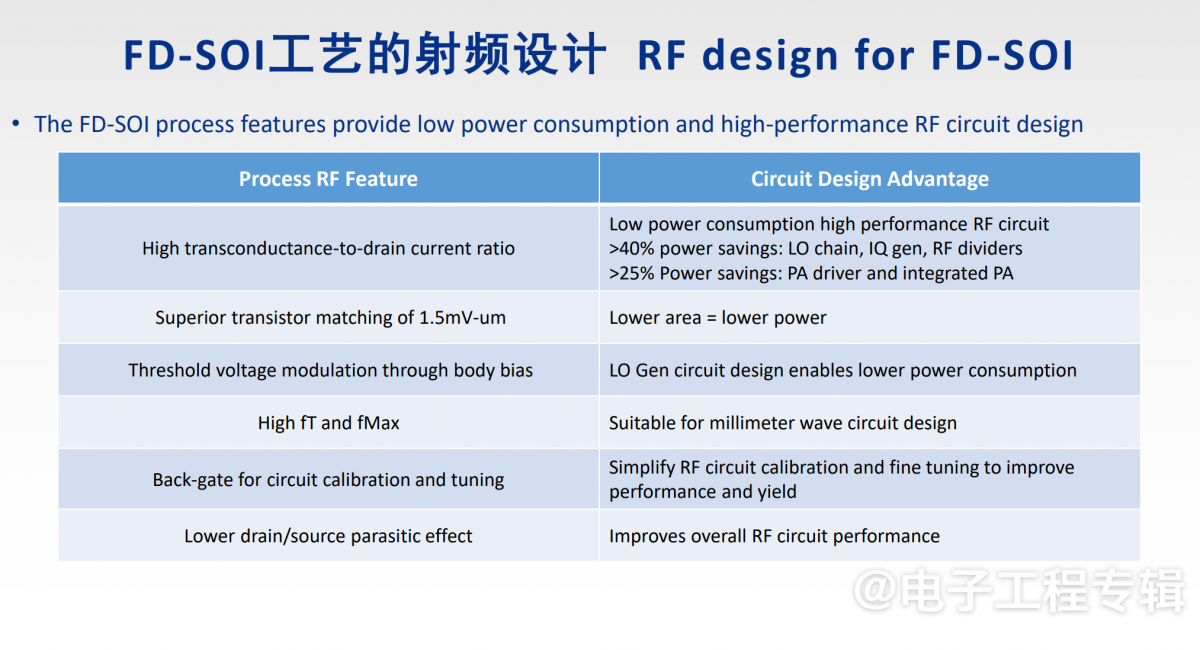

基于FD-SOI工艺的嵌入式RF有哪些关键技术优势?

FD-SOI工艺在射频设计上具有多项优势,这些优势主要体现在以下几个方面:

- 低功耗:FD-SOI工艺提供了超薄的埋氧化层,这有助于降低器件的漏电流,从而实现低功耗设计。

- 高性能射频特性:FD-SOI工艺的晶体管具有高电子迁移率,这使得射频器件能够达到更高的频率,如毫米波和太赫兹波频段的通信。

- 良好的射频性能:FD-SOI工艺的晶体管设计可以提供低噪声系数和高线性度,这对于射频通信系统来说至关重要。

- 集成度高:FD-SOI工艺允许在单一芯片上集成更多的功能,如射频前端模块、数字信号处理器和存储器等,这有助于减小设备的尺寸和重量,提高集成度。

- 抗干扰能力强:FD-SOI工艺的绝缘体结构提供了良好的抗干扰能力,这对于需要高频率和高速数据传输的应用场景尤为重要。

- 温度稳定性好:FD-SOI工艺的器件在宽温度范围内能够保持稳定的性能,这对于汽车和工业应用等对温度变化敏感的应用场景非常关键。

- 设计灵活性:FD-SOI工艺支持多种晶体管设计,为射频前端模块的设计提供了更大的灵活性。

Dolphin Design 亚洲区销售总监Ying Zhao认为FD-SOI在RF设计中最重要的优势是基于自适应Body-Biasing(ABB)的功耗调节功耗特性最为重要的,其次能够提高系统可靠性也很重要。“因为ABB是一种close loop的design,可以用最可靠的方式去实现需要达到的频率。同时低功耗带来的电池寿命延长,对于IoT应用来说也很重要。很多IoT设备从开始使用,就再也没有充电的机会了。”

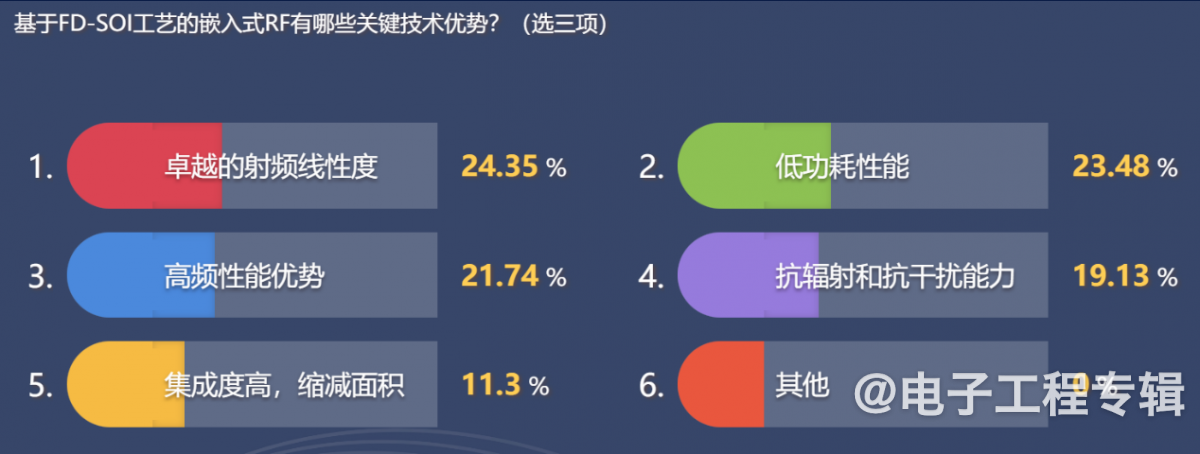

从现场观众投票来看,选择的前三项优势分别是卓越的线性度、低功耗性能以及高频性能优势。而对于抗干扰和靠辐射能力,芯原股份无线 IP 平台高级总监曾毅认为,未来在汽车、航空航天应用中都是必不可少的特性。

曾毅表示,以往大家都认为射频设计比较难,它最具挑战的地方就是“两个率”——频率和功率。频率除了高频设计的挑战,还要保持在某个频率、带宽内的稳定工作,这就要求很好的一致性,“这对于物理器件是很大的挑战,因为所有的材料都有阻抗、容抗、感抗等电抗特性,和频率相关。一旦频率改变,模型就会随之变化,这就导致在不同频率下的电路设计要考虑到模型的非线性变化。”

其次是功率,所有射频都是处理从天线接收或发出的功率信号,大的时候可以到20-30dBM以上,小的时候可以到-100dBM,具备非常宽的功率动态范围(10的12次方)。“如果到了电路中折算成幅度,大约是10的6次方变化范围。要处理如此大的变化,也是射频设计的难点。”曾毅说到,FD-SOI体现在射频设计上的优势是降低了物理限制,主要体现在三点:

- 全耗尽的绝缘体上硅里面整个器件结构是一个极薄的沟道,下面是绝缘层。它是没有掺杂的,所以噪声天然就小。射频信号处理的就是SNR(信噪比),噪音越小,就可以用越低的功耗去处理这个信号。由于绝缘层的存在,寄生电容也小,这与频率直接相关。往往频率的改变会导致寄生电容参数不一致,电路拓扑也会不一致,FD-SOI杜绝了这个问题。

- Body Bias功能在RF电路设计中一般叫背栅偏置,当做一个栅极使用,而不是直接接入固定或指定电压。这可以动态调节VTH(阈值电压),使得其整个IV curve特性会发生较大变化。在整个系统里可能在每一个模块设计的线性度不一样,就可以根据需要去调节背栅,得到一个需要的工作区间。

- 电流增益。FD-SOI适合毫米波是因为其截止频率高,一般来说频率越高,增益就会下降。FD-SOI则在很高的频率下,也能提供较大的明显电流增益。对于毫米波的设计,尤其是前端的PA放大器就非常有好处。

至成微科技 (浙江) 有限公司首席执行官成飞认为,如果只是做一个比较低频的窄带应用,FD-SOI的射频优势还不能充分发挥出来。RF企业往往追求两个极端,一是追求超低功耗,二是追求高带宽高频率。“FD-SOI低功耗的特性已经毋庸置疑非常适合智能眼镜这类设备对连接性的要求,而如果从高带宽高频率应用来看,FD-SOI的优势也同样明显。”

以蜂窝通信为例,过去高通的5G RF一直在用14nm或12nm FinFET工艺在做,但到了5G毫米波阶段他们做出了改变,开始采用22FDX来做,这就很好的说明了FD-SOI在高频性能层面的优势。

对于Wi-Fi来说,2.4G频段其实用40/28nm、Bulk CMOS什么工艺都可以,但是到了6G频点的时候,对射频的需求就更大了,如果是端侧芯片还需要集成。成飞举例到,比如5G FEM对前端模组的集成,而且对线性度要求较高的话,FD-SOI会具备非常强的收益。“无论是802.1层级的RF,3GPP层级的RF,还是4D成像毫米波雷达的RF,我发现大部分都在用22DX。”在77G、78G这类高频点层面上,FD-SOI的优势更加明显,据说博世也在用FD-SOI来做这类产品。

除了使用FD-SOI工艺之外,还有哪些射频设计技巧?11月5日,Aspencore将在深圳IIC期间举办一场无线连接技术与应用论坛,报名来现场,发现更多射频设计小妙招:https://app.zhundao.net/event/pc/index.html?track=0005&id=371182

EDA如何针对FD-SOI设计进行优化?

EDA工具对于FD-SOI设计的支持,其实flow上与Bulk工艺差不多,但从目前几大龙头EDA企业来看并没有太大的投入。对此芯和半导体科技 (上海) 股份有限公司董事长凌峰表示,关于对FD-SOI的EDA flow,早在2017年时曾经出现过一个高潮,EDA厂商纷纷入局推出FD-SOI ready的工具。

“那个阶段整个design flow都在看哪些领域需要做一些针对FD-SOI的改进,无论从流片还是 sign-off环节,都要看一遍body bias需要在哪个地方加进去。” 凌峰说道,这几年虽然速度放慢了,但FD-SOI本身在不断前进,应用也在不断增多,所以EDA企业在22FDX上还是与客户有着非常多的合作,PDK更新的也很快。“我们EDA企业也是walk with two legs,如果未来本地能有一家FD-SOI Foundry,那我认为本土EDA公司一定要参与进去。”

除了无线连接技术与应用论坛,11月5-6日两天的峰会还将带来以下精彩内容,欢迎扫码报名: