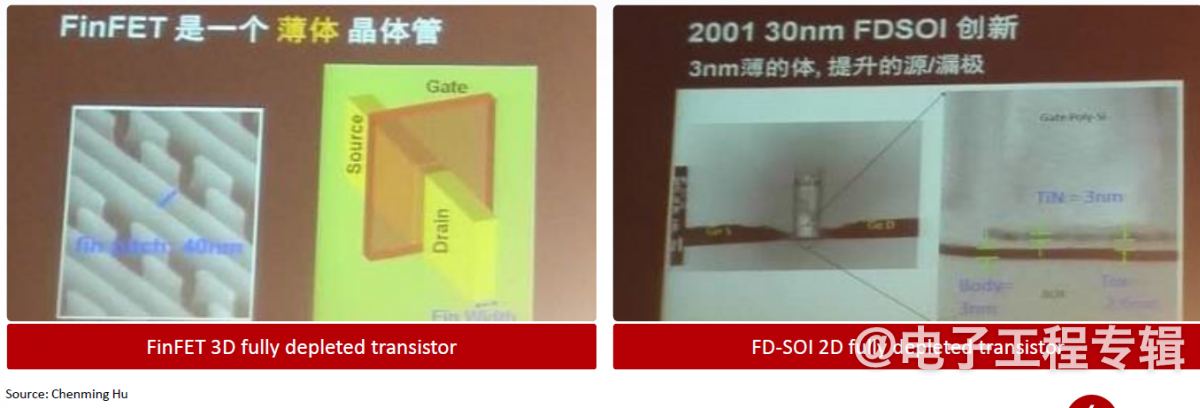

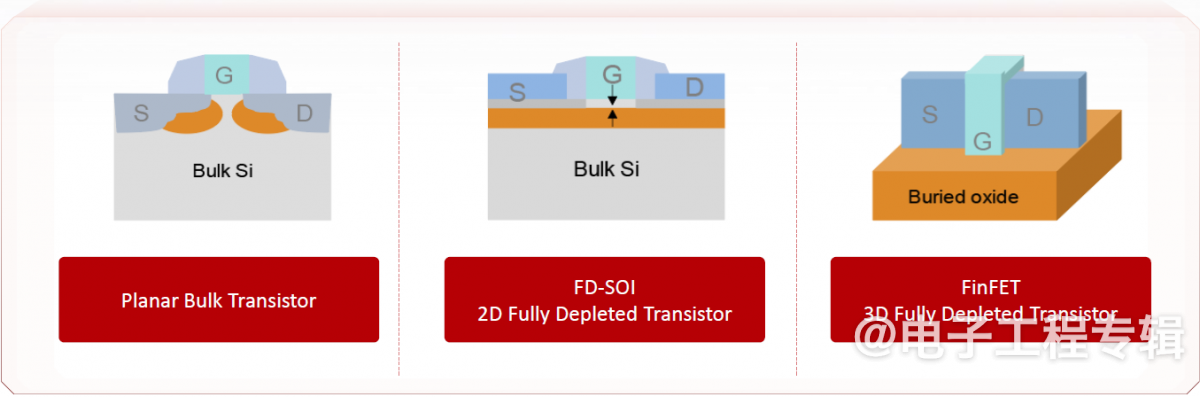

在2001年,加州大学伯克利分校的胡正明教授、Tsu-Jae King-Liu教授和Jeffrey Bokor教授提出了两种解决方案,以将CMOS工艺技术扩展到20纳米以下。这两项技术分别是FinFET 3D全耗尽晶体管和FD-SOI 2D全耗尽晶体管。

什么是FD-SOI?

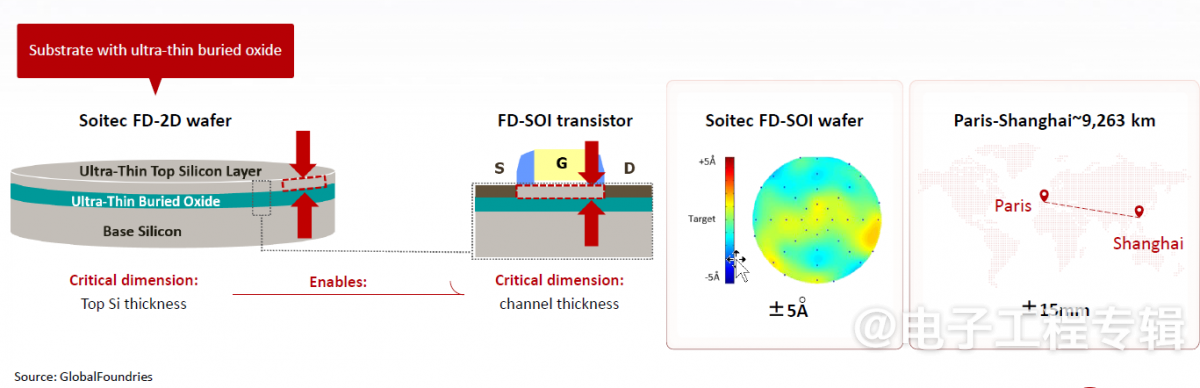

FD-SOI,即全耗尽硅型绝缘体上硅技术(Fully Depleted Silicon-on-Insulator),它主要依赖于两项主要创新:在基底硅的顶部放置一层超薄绝缘体(掩埋式氧化物)和一个非常薄的硅膜来实现晶体管沟道,其关键尺寸包括通道厚度和顶层硅厚度。由于沟道非常薄,无需对通道进行掺杂工序,耗尽层充满整个沟道区,即全耗尽型晶体管。

虽然当前业界主流的先进半导体工艺是FinFET,但FD-SOI技术以其超薄、全耗尽的通道提供了更好的栅极控制,从而实现了更好的晶体管缩放。与传统的平面体晶体管和FinFET 3D全耗尽晶体管相比,FD-SOI技术具有其独特的优势。

FD-SOI产业的里程碑

自2012年以来,FD-SOI技术取得了一系列的产业里程碑。包括:

2012年意法半导体(ST)推出28nm FD-SOI平台;

2013年,Soitec突破了FD-SOI高质量基板的技术瓶颈,芯原微电子(VeriSilicon)与ST合作开发FD-SOI技术;

2014年,三星获得意法半导体28nm FD-SOI工艺平台的授权,芯原开始与三星在FD-SOI技术上合作,同年上海新傲科技获得了Soitec Smart-Cut技术授权;

2015年,格罗方德(GlobalFoundries,GF)推出22FDX,22nm FD-SOI代工平台,芯原与GF合作开发FD-SOI技术;

2016年,上海新昇科技宣布收购Soitec 14.5%的股权;

2017年更是FD-SOI快速发展和批量应用的一年,GF推出了基于FD-SOI技术的FDXcelerator芯片,NXP的i.MX7、i.MX8等8款应用处理器采用FD-SOI技术,索尼的新一代GPS采用FD-SOI技术,欧特莱卫星通信公司的下一代交互应用SoC采用FD-SOI技术,Dream Chip推出首款用于汽车计算机视觉的ADAS SoC。另外国内的瑞芯微、复旦微电子、湖南国科微也宣布使用22nm FD-SOI工艺设计IoT芯片。

在日前举办的第九届上海FD-SOI论坛上,主办方代表芯原股份创始人、董事长兼总裁 戴伟民博士在开幕致辞中表示,自2013年首届论坛举办以来,参与人数从50人增加到2019年第七届论坛的450多人。“这一增长反映了FD-SOI技术在全球范围内受到的广泛关注和快速发展。”

芯原股份创始人、董事长兼总裁 戴伟民博士

“自2013年以来,芯原(VeriSilicon)连续举办了八届FD-SOI论坛。”戴伟民表示,“在第八届上海FD-SOI论坛上,我们与来自GlobalFoundries、意法半导体、三星电子、IBS、NXP等公司的嘉宾一起,讨论了FD-SOI技术当前的市场成就和未来的发展。我们一直在问,FD-SOI什么时候起飞?现在看来,至少IP已经不是一个问题了。”

FinFET和FD-SOI,两条腿走路

从高性能、低功耗的设计需求出发,IP作为设计环节中的关键因素,对FD-SOI技术的应用起到了至关重要的作用。为了支持和促进SoC设计,芯原自十年前就开始投入研发力量,开发并建立了一套基于22nm FD-SOI工艺的IP平台。

据介绍,芯原在22nm FD-SOI上拥有59个模拟和数字模拟混合IP,包括基础IP、DAC IP、接口协议IP等。戴伟民表示,公司已经向40多个客户授权了260多次FD-SOI IP核心,并为全球主要客户完成了约30个芯片设计项目,其中25个项目已投入生产。

其中,丰富的射频(RF)IP和基带IP组合,包括BTDM、BLE、802.11ah、802.15.4g、Cat-1、NB-IoT、GNSS。所有RF IP都经过了硅验证,并设计了基带IP以提供完整的无线IP解决方案。

此外,芯原还提供了包括MIPI DPHYRX、MIPI DPHYTX、USB2.0 PHY、USB3.0 PHY、PCIE3.0 PHY、PCIE2.0 PHY、12G SERDES PHY、HDMI 2.0 TX PHY、LVDS RX、LVDS TX、MIPI CDPHYRX和MIPI CDPHYTX在内的接口IP。

据悉,芯原基于FD-SOI的Turnkey服务包括世界上第一个应用自适应体偏置技术(Adaptive Body Bias,ABB)的案例,累计出货量超过6000万,与28nm体相比功耗降低了55%。以下图一款室外无线监控摄像头产品为例,使用2节AA电池可支持2年的运行时间。

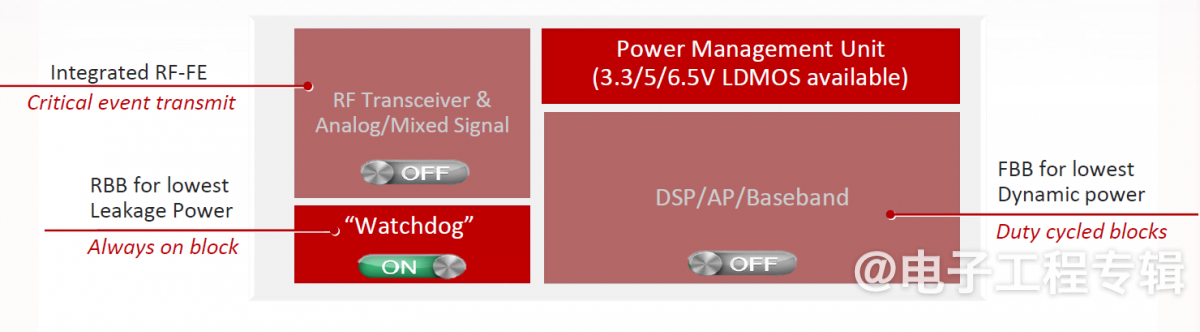

戴伟民介绍了芯原的首个基于体偏置的SoC设计,这为下一代物联网单芯片解决方案提供了新的方向。据悉,这项技术可以实现最低的动态功耗和泄漏功耗,具体包括:

- 反向体偏置,待机监控模块漏电功率降低 10 倍;

- 正向体偏置,基带模块性能更高,动态功耗更低;

- 电源关闭,待机模式下可关闭射频模块和基带模块。

“随着Wi-Fi 6、Wi-Fi 7、LTE CAT-1、CAT-4和毫米波技术的发展,FD-SOI技术在宽带连接领域展现出巨大的潜力。”戴伟民说道,如今业界在半导体工艺上开始采用“双足战略”(Walking with Two Legs),FD-SOI技术在物联网、5G、图像传感器、自动驾驶、航空、毫米波雷达、长待机应用、云服务和高性能服务器等领域有着广泛的应用;而FinFET技术则在前沿消费电子、连续高性能应用、AI和边缘计算等领域发挥着重要作用。“我们可以看到,在一些需要超低功耗、稳定性的终端应用上,FD-SOI具备FinFET没有的优势,例如IoT、5G、图像传感器、毫米波雷达以及需要长续航的应用。”

如今智慧物联网正加速普及,大量带AI、可互联的终端产品正进入千家万户,惠及大众的边缘AI正成为现实。但这类设备对于低功耗、可靠性的要求如何在芯片层面得到满足?FD-SOI和FinFET两条腿走路,实现AI异构计算的融合或许才是发展之道。11月5日,Aspencore将在深圳举办一场关于‘边缘·芯未来’的前瞻性对话暨探讨,芯原执行副总裁,业务运营部总经理汪洋将发表题为《塑造智能计算的未来:惠及大众的AI技术》的主题演讲,欢迎点击链接报名参会:https://app.zhundao.net/event/pc/index.html?track=0005&id=371182

芯原在FD-SOI技术上的布局

近年来,FD-SOI技术在物联网(IoT)、可穿戴设备、智能家居、汽车电子、高精度导航、新能源、无线电池管理系统(BMS)以及医疗健康等领域取得了显著进展。FD-SOI技术以其高性能、高集成度、低功耗和自适应体偏置等特性,在实际设计和应用中展现出了巨大的潜力。

芯原股份无线IP平台高级总监 曾毅在主题为《为SoC设计提供基于FD-SOI的IP技术平台》的演讲中分享了公司在FD-SOI技术上的最新进展和成果。

芯原股份无线IP平台高级总监 曾毅

芯原的无线IP平台覆盖了Sub 6G的所有频段以及多种应用场景,包括短距离连接的蓝牙(BLE)、Wi-Fi,中距离通信的802.11H和15.4G,以及远距离通信的4G LTE和Wi-Fi。

曾毅特别强调了BLE IP平台,该平台提供了完整的BLE技术解决方案,支持BLE5.4标准,具有优秀的整体性能和超低功耗特性。同时,BLE IP平台还具备灵活的架构,方便客户通过软件进行升级,并已广泛应用于智能家居、可穿戴设备、医疗健康和工业控制等领域。

在GNSS方面,曾毅介绍了芯原的VSI GNSS平台,该平台支持GPS/BDS/Galileo/Glonass四种卫星导航模式,在L1和L5频段上实现高精度定位和导航。VSI GNSS平台由双通道RF IP、基带IP和运行在RISC-V CPU上的固件组成,具有高灵敏度捕获和跟踪能力、快速启动和重捕能力,以及厘米级定位精度。

“该平台已集成到多个SoC中,并在智慧农业等领域中取得了成功应用。”曾毅表示。

曾毅还介绍了芯原为客户定制的基于802.11ah标准的Sub-1G无线解决方案。该方案实现了802.11ah物理层(PHY)的完整功能,包括视频收发机、MAC层以及PMU和时钟模块,集成了RF TRX、基带、PMU和XO,主要应用在家庭无线摄像头和智能门铃等设备中。该解决方案支持高达20dBm的发射功率,覆盖范围可超过300米,并支持大于7Mbps的传输带宽,是一款高性能的无线解决方案。

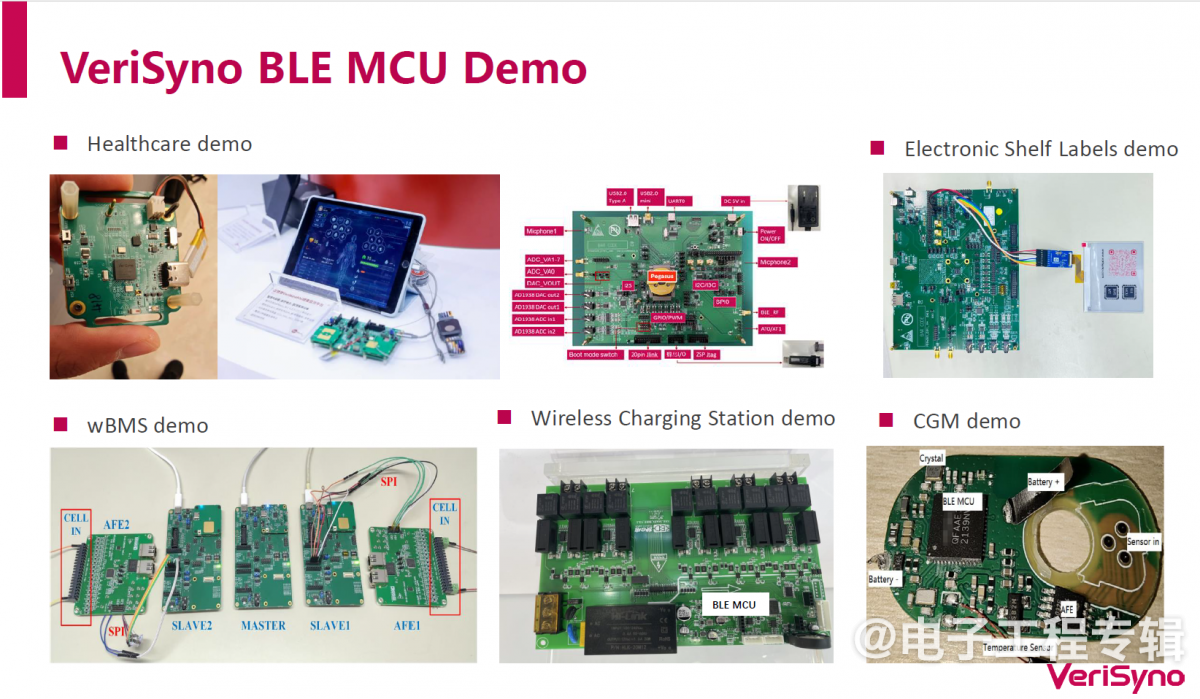

具体案例:FD-SOI用于BLE MCU

有了IP解决方案,还要有落地的产品,以蓝牙MCU为例,过去大多通过两颗Die以SIP封装方式集成(BLE Die + MCU Die)。“业界的目标是将这两颗Die合并到一颗中,这将带来降低系统功耗、缩小PCB尺寸、降低BOM成本、提高系统可靠性等好处。”芯思原微电子有限公司研发总监 高挺挺在主题为《基于FD-SOI工艺的BLE MCU一体化设计》的演讲中表示,“然而,这也带来了如电源管理、RF干扰、安全隐私保护、软件开发复杂性以及调试和测试难度等挑战。在低功耗设计方法论中,FD-SOI技术在模拟设计方面表现出高效率和性能,同时在RF/mmW设计中展现出高频行为优势。”

芯思原微电子有限公司研发总监 高挺挺

芯思原成功开发了基于FD-SOI工艺的BLE MCU一体化设计方案,高挺挺指出,FD-SOI技术在模拟性能、低噪声、高效短设备、高频行为以及非常大的VT调节范围等方面都有显著优势。“这些优势使得FD-SOI技术在所有模拟块的速度上都有提升,通过其独特的结构,能够在不牺牲性能的前提下显著降低功耗。”

他展示了仿真实验数据,对比了28nm FD-SOI LVT NMOS与28/40nm Bulk CMOS在高频行为(fT和fmax)上的表现,实验结果显示,尽管面积相同且输出频率一致,但Bulk CMOS的功耗远高于FD-SOI,后者仅为27nA。考虑到对芯片性能的高要求,客户最终选择了FD-SOI工艺。这证明了FD-SOI具有更高的效率和更低的功耗,这对于BLE MCU在数据传输和实时响应方面的要求十分重要。

高挺挺还提到了埋氧层(Buried Oxide Layer)可以增加击穿电压,这对PA输出功率有积极影响,同时对于BLE设备的通信距离和稳定性至关重要。“FD-SOI技术具有出色的抗干扰能力,能够在复杂的电磁环境中保持稳定的通信性能。”

据介绍,BLE MCU的系统架构设计,包括MCU核心、BLE模块、电源管理单元(PMU)等关键组件。其中系统架构的灵活性和可扩展性,是满足不同应用场景需求的基础。

另外,低功耗、射频也是BLE MCU的核心考量因素。高挺挺分享了芯思原在低功耗和基于FD-SOI技术的RF设计方面的经验和技术,如电源门控、时钟门控、收发机、前端器件等,除了可以进一步优化芯片的功耗表现,还体现出了FD-SOI在RF设计中的优势。

“在低功耗设计方面,芯思原拥有一套独特的know-how,可以概括为四个层级:系统级(system level)、架构级(architecture level)、设计级(design level)以及晶体管级(transistor level)。”高挺挺说道。

基于FD-SOI工艺的BLE MCU在多个市场应用场景中极具潜力,包括医疗保健、工业控制和智能家居。例如,在医疗保健领域,集成BLE MCU的可穿戴设备不仅降低了功耗,还提高了数据传输效率,使用户能够实时监控健康数据并享受更便捷的生活。

随着5G技术的普及,物联网设备的数量将持续增长,对低功耗、低成本、高性能的集成BLE MCU的需求也将随之增加。FD-SOI技术以其在低功耗、高性能和抗干扰能力方面的独特优势,将成为BLE MCU和无线芯片的关键技术之一。随着GF、ST、三星等Foundry厂加大对FD-SOI技术的投入,FD-SOI技术的生态系统将日益成熟,其在高频和低功耗应用领域的作用将越来越重要。

资料显示,芯思原微电子有限公司成立于2018年9月,坐落在安徽省合肥市高新技术产业园区,并在北京、上海和深圳设有分支机构。芯思原微电子有限公司由芯原微电子(上海)股份有限公司(Verisilicon)和美国新思科技(Synopsys)等4家公司共同投资设立,公司基于各类高速接口IP和模拟IP,先后开发了适用于健康、物联网和新能源存储的IC芯片。

FD-SOI的市场增长和技术发展

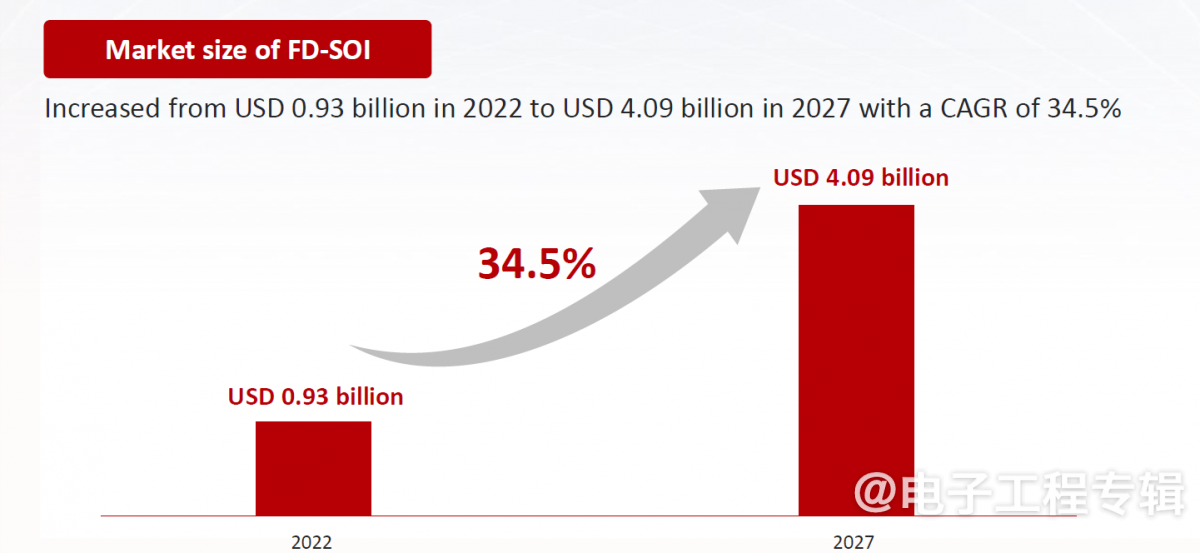

从2022年的9.3亿美元增长到2027年的40.9亿美元,FD-SOI技术市场规模的年复合增长率为34.5%,显示出其在半导体市场中的广泛关注和快速增长。全球各个国家、大型半导体企业和科研机构也在纷纷加码FD-SOI的投资。

欧盟投资12nm FD-SOI:2022年7月12日,法国总统马克龙、欧盟委员、GlobalFoundries首席执行官Thomas Caulfield和STMicroelectronics总裁兼首席执行官Jean-Marc Chery宣布,ST和GF将在法国建设一个新的12英寸晶圆厂,用于12nm FD-SOI技术,以推进FD-SOI生态系统的发展。

ST和三星联合推出18nm FD-SOI技术:2024年3月19日,ST和三星联合宣布了18nm FD-SOI技术,该技术集成了嵌入式相变存储器(ePCM),显著提高了性能并降低了功耗。更大的存储容量和更高级别的模拟和数字外设集成。基于这项新技术的首个下一代STM32 MCU将于2024年下半年开始采样,计划于2025年下半年投入生产。

CEA-Leti宣布启动10nm和7nm FD-SOI试点线:2024年6月11日,法国CEA-Leti宣布启动FAMES试点线,将开发包括10nm和7nm FD-SOI在内的五套新技术。这一举措与欧盟芯片法案的雄心相一致,已有43家电子系统价值链中的公司正式表达了对FAMES倡议的支持。

最后戴伟民表示,随着FD-SOI工艺的不断进步,芯原将继续致力于FD-SOI技术的研发和推广,不断优化和完善其IP平台,以更好地满足市场需求。他相信,在FD-SOI技术的推动下,芯原将继续在设计领域发挥重要作用,推动整个行业的发展。

除了芯原带来的精彩演讲,11月5-6日两天的峰会还将带来以下精彩内容,欢迎扫码报名: