ASML最新一季财报引发了挺多争议,焦点的一部分在high-NA高数值孔径光刻机上,尤其是其高成本问题。业内人士最近普遍也指出了high-NA EUV光刻机光路结构变化,反射镜、夹具系统,乃至真空系统、激光器都需要重新设计,加上生产过程中可能存在的低效,仅有的做先进制造工艺的几家foundry厂不足以承担如此沉重的成本。

援引台积电CEO魏哲家(C.C. Wei)此前曾说过的话:“技术本身没有价值。能够服务客户的才有价值。”(Technology itself is of no value. Only what can serve your customer.)

“我们与客户合作,为他们提供最好的晶体管技术,以及合理成本之下的最佳能效的技术。”“更重要的是技术成熟性,能够规模量产。”...“每次我们看到新的结构,诸如high-NA EUV这样的新工具,我们都会仔细去审视,去了解工具的成熟度,工具的成本和规划——如何获得这样的工具。”

“我们总是在正确的时间做出正确的决策,来服务我们的客户。”这段话大概是能够表明台积电现阶段在high-NA EUV光刻机上的态度的,也表明了high-NA EUV光刻机现在可能的确成本偏高了。

不过我们倒是认为,半导体制造相关的技术,乃至电子科技或计算机领域的诸多技术,发端之初总面临成本过高的问题。除非技术方向完全选错,否则凭借人类的聪明才智,加上持续的经验积累和走量摊薄,总能找到一些方法慢慢让成本降下来。

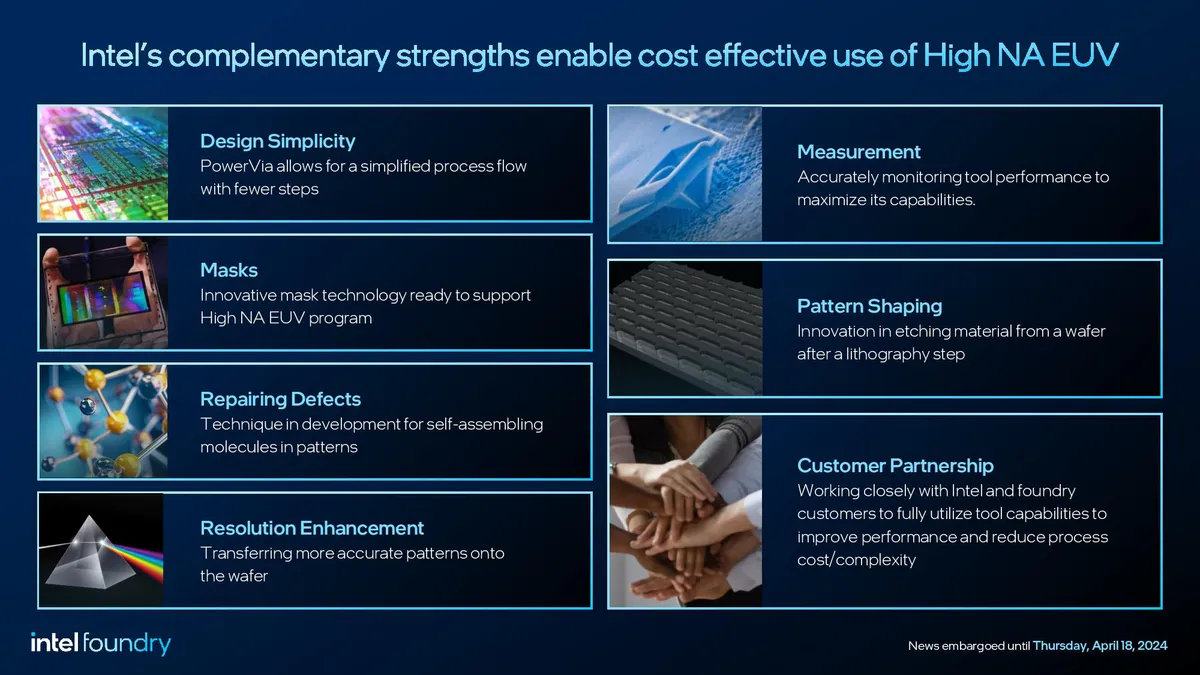

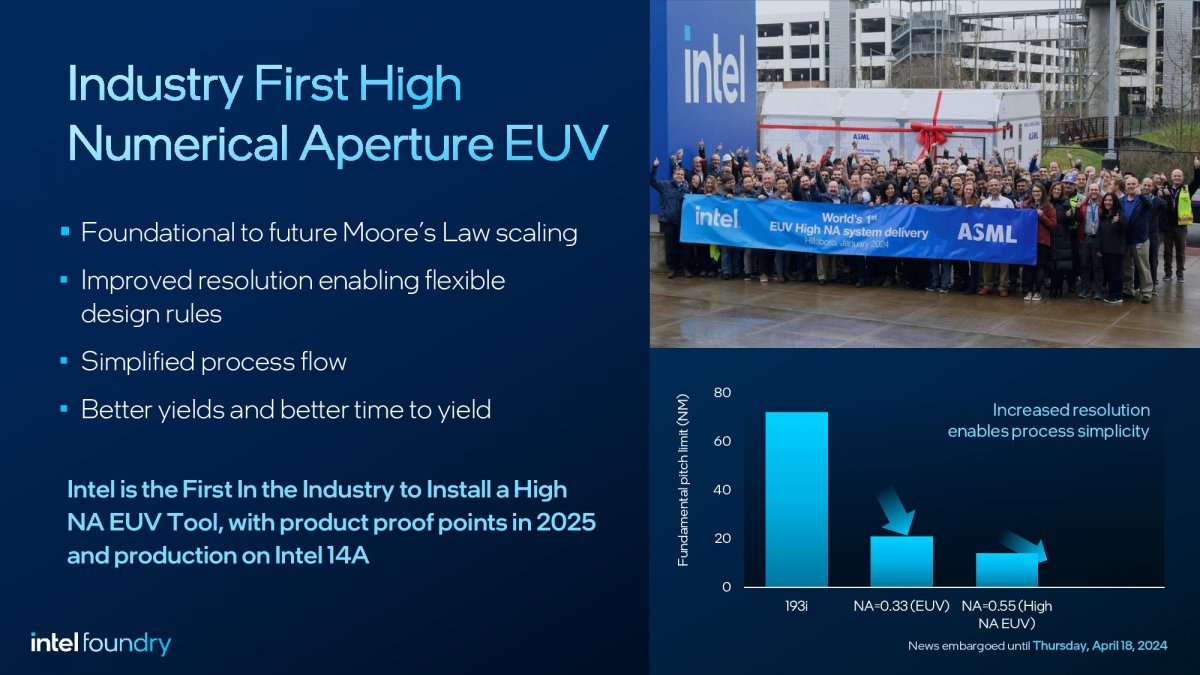

比如说Intel在SPIE Advanced Lithography + Patterning(国际光学工程学会先进微影成形技术会议)上提到的DSA(direct-self assembly)技术。据说DSA会成为Intel接下来大幅降低光刻成本的关键方案。

不管企业组织层面Intel Foundry剥离与否,预计Intel后续的High-NA EUV就会用上DSA技术,上图中的“repairing defects”项目中就已经提到了,那么Intel 14A就极有可能成为应用DSA技术的工艺节点。那这DSA究竟是个什么技术呢?

DSA对于芯片制造而言,有什么用

SemiWiki上有关DSA的技术文章,早在2012年就有了。实际上这种技术的存在历史的确也不短了。早在10-15年前,EUV尚未准备就绪之际,DSA就曾经作为延续DUV寿命的候选技术存在了。

当时DUV多重曝光、更短的波长(157nm)、DSA都在其中。当然现在我们知道,最终多重曝光胜出,往后EUV也大规模量产了。DSA技术随后就限定在一些容错率更高的niche应用领域,不再出现在尖端制造工艺的技术列表内。典型的像是图像传感器,索尼过去几年就一直在用DSA技术。

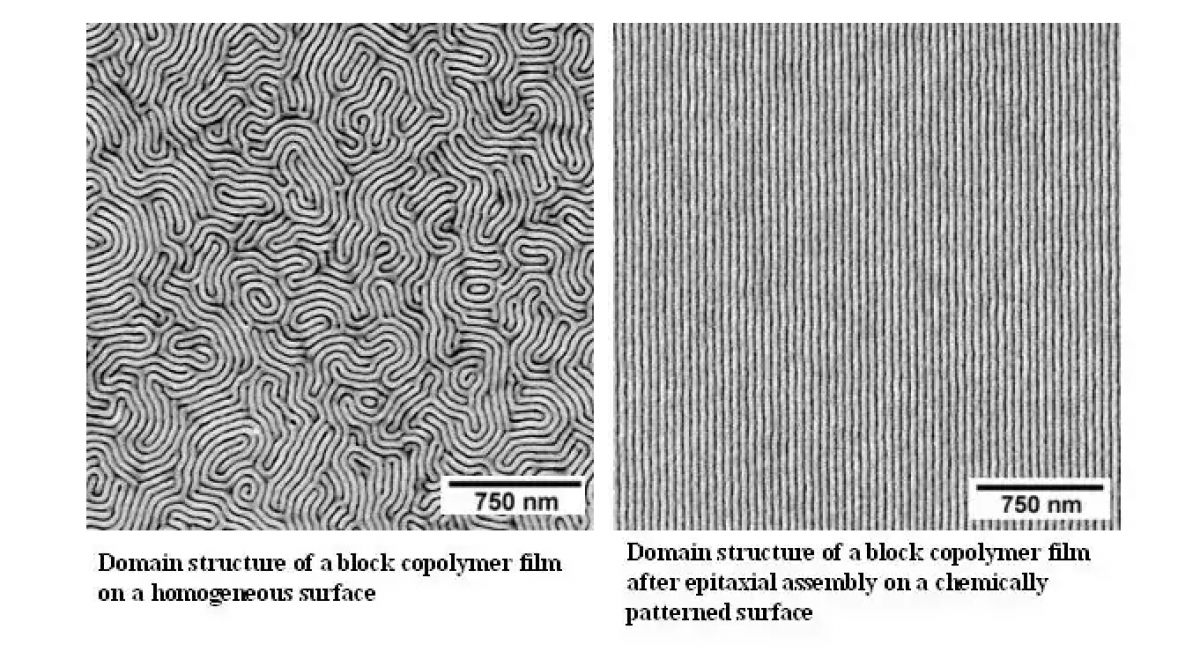

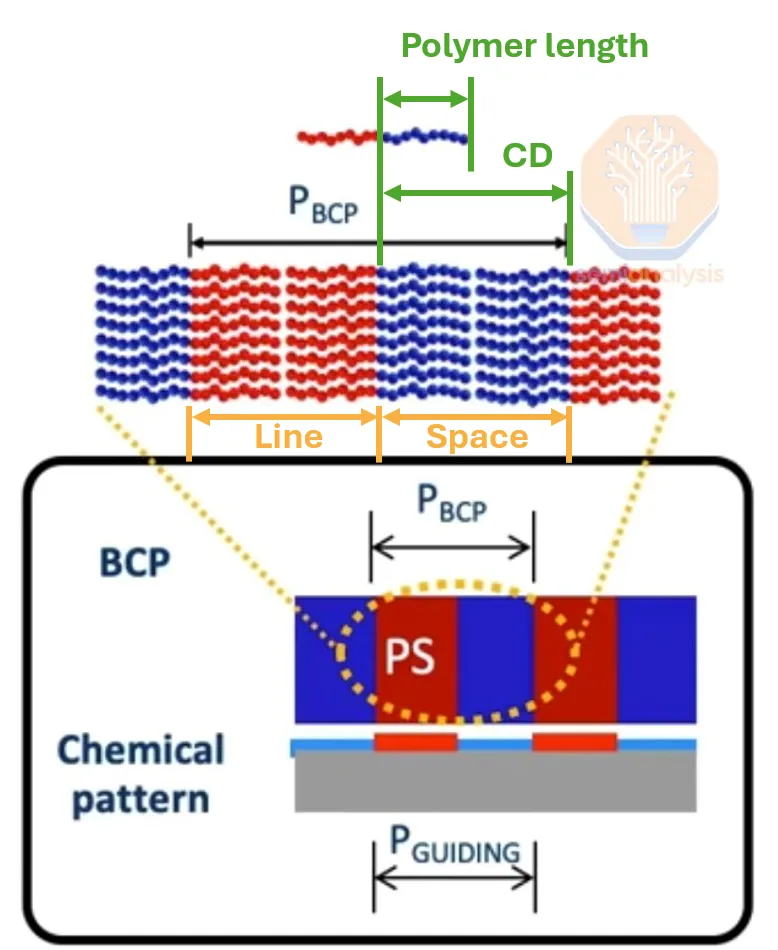

Semiconductor Engineering对于DSA的解释是这样的:DSA是一种光刻的补充技术。与pre-pattern(预成形)——自动引导嵌段共聚物(block copolymers)方向的技术联用,DSA能够缩减最终结构的间距(pitch)。采用193nm光刻,DSA就可以将图形结构的间距缩减到12.5nm。

这段话不仅看不懂,而且也仍然无法让我们搞清楚,DSA是如何让high-NA达成降本的。那我们就先从high-NA为什么存在生产成本高的问题说起。

抛开high-NA EUV光刻机本来就售价高昂不谈,high-NA制造的高成本包含的因素有关键尺寸(CD)、曝光量(exposure dose),两者的关系及对生产吞吐造成的影响,以及最终落到每片晶圆的成本。

CD关键尺寸,也就是光刻机可达成的最小线宽线距——这个值越小、且在保证出色图案质量的情况下,也就需要更高的曝光量。

由于光源的功率限制,要提供更大的曝光量,也就意味着整个光刻机运行得更慢,或者说更久的曝光时间,也就是要求足够的光子抵达曝光区域。而跑得越慢,也就是指光刻机单位时间内可处理的晶圆更少,则意味着生产成本的增加。

更少的曝光剂量倒是可以让光刻机跑得更快,但曝光图案的质量会很差——了解摄影的读者,应该很清楚在曝光时间较短的情况下,传感器接收到的光子少,则散粒噪声会显著影响画质。

这个时候DSA就能派上用场了。SemiAnalysis形容DSA是一种纳米成形技术(nanopatterning technique),基于嵌段共聚物(block copolymers)的自组(self-organizing)特性,藉由预成形的模板引导完成。简单来说DSA可以大幅降低光刻机工作过程中曝光所需的剂量,提升最终成像的质量。

所以DSA究竟是什么?

DSA这个词里面的“self-assembly”(自紫装)本身就是在描述一种将随机排列重新组合成规则的、有用的结构的过程。根本上应当是化学属性使然,即前文多次提到的嵌段共聚物(BCP)。Copilot对于BCP的解释是,某种类型的共聚物,是两个或更多高分子聚合物段(块)通过化学键结合在一起。组合后的BCP具备个体聚合物段所不具备的物理和化学特性。

两个仅纳米级长度的polymer聚合物,由共价键链接,形成BCP。目前最先进的方案是PS-b-PMMA(Polystyrene-block-poly,似乎完整翻译叫苯乙烯-甲基丙烯酸甲酯的两嵌段共聚物)。总之就是PS和PMMA,就像水和油一样——它们会天然地分层,PS-b-PMMA天然地形成规则的、有序成形的层。为之增加热能,会让分子更快地达成这种天然平衡。

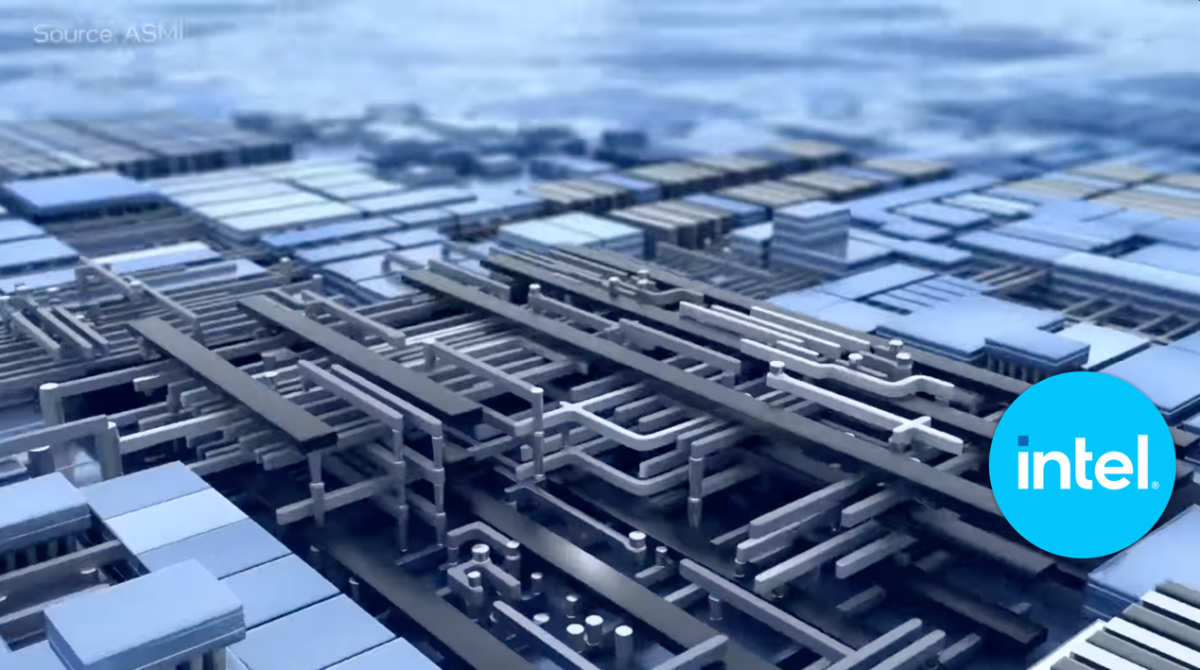

那么晶圆表面用上一层PS-b-PMMA,再加热不到一小时,就会形成PS与PMMA交错行的规则结构,每行宽大约20nm。听起来,这对于形成芯片所需的超薄金属线,也就是晶体管上方的互联层、金属堆栈相当有价值,甚至是先进工艺所需的M0层。

但实际情况肯定就要比这复杂很多了,因为这些所谓“交错行”的方向、结构实际上仍然是相对随机的,仍然需要引导才能真正辅助光刻。

EUV曝光就能用于做引导成形(guide pattern),从而明确自组装self-assembly过程的方向和位置。这个过程本身和常规的EUV光刻很像,只不过对于DSA而言,图案是从光刻胶转移到为DSA特制的衬层。这种衬层针对BCP嵌段共聚物的其中一种聚合物,具备了所谓的化学亲和力(chemical affinity)。

来源:SemiWiki

那么有了特定图案的衬层,共聚物因为自身特性完成self-assmebly,同时又能依照衬层的引导来完成图案对齐,则最终形成的图案就是芯片设计所需的。

Intel在SPIE技术会议之上给出的说法是,CD关键尺寸(尤指线宽、线距)由每个聚合物链的长度决定,也就可以根据需要来制造。据说目前DSA材料较为领先的制造商已经展示了达成9nm CD关键尺寸的可能性,对于匹配high-NA EUV显然是有价值的。

Chemical “magic” of DSA: block copolymer self-assembles in lines, aligned with a guide pattern underneath, Source: (Han, E. et al. "DSA materials and processes development for ≤ P24 EUV resist L/S pattern rectification," Proc. SPIE 12956 (2024)) & SemiAnalysis

而真正的关键在于,针对EUV做引导图案,可以少得多的曝光剂量来进行生产。基于前面的解释,不管EUV达成的引导图案质量如何,DSA可以实现很低的LER(Line Edge Roughness),也就是更为清晰和锐利的图案。DSA所用的共聚物会与引导图案的平均值对齐。也就是EUV曝光的LER不行,DSA则进行了“修复”。

具体到量级数据,SemiAnalysis在报道中给出的是这能够让EUV曝光剂量减少50%或更多。

进展情况和存在的问题

Intel给出的数据似乎还要再乐观一些,基于某种衬层,可直接以EUV曝光成形,而不需要将图案从光刻胶上转移过去,实现了曝光量3-4倍缩减(80 mJ/cm² → 25 mJ/cm²)。如果这一成果可用于量产,则成本节约还可更进一步。

另外值得一提的是,PS-b-PMMA可以进行选择性蚀刻(etch)。将PMMA移除,让PS成为线,原来PMMA的位置也就成为了间隔。则这么做颇有点像光刻胶的用途了,后显影流程也就可以应用了...

总的来说,Intel在SPIE技术会议上给出的结果是,采用DSA来“矫正”图案时,基于自对准EUV LELE(litho-etch-litho-etch)方案可达成相当出色的良率水平。

不过一项技术既然十几年前就有了,到现在却并未大规模应用到尖端制造工艺,一定是有原因的。比如说有一些存在但可解决的问题,像是芯片制造过程中不同的特定间距需求,也就需要不同长度的BCP。那就需要不同的方案和结构。据说EMD Electronics已经能够将长度容差控制在0.5nm上下。

DSA流程的线与间距图案之类的是一维的,对于设计规则而言单层可能要限定某个pitch数字。而诸如对齐标记(alignment marks)就是二维的,很难完全满足这样的要求。只不过该问题也可以通过multi-patterning多重曝光这样的方案来解决。总之DSA就是相当适用于造contant触点、via和金属层。

而真正最大的问题似乎还是在于BCP的缺陷率。达成高纯度BCP嵌段共聚物的合成具备相当的挑战性。前文已经提到了聚合物链的长度决定了CD关键尺寸,那么任何化学相关的不均一就会导致缺陷。

也就是杂质会带来问题。先进工艺制造极低的宽容度自然对纯度提出了相当高的要求。SemiAnalysis特别在分析文章中提到有机杂质更是不可接受的,因为它很难被检测,更不要说将杂质过滤出来。

可以说过去这些年DSA未能大规模量产,最主要的原因就是杂质和缺陷率问题。而现在被提上日程,一般应该是某些工程技术取得了突破性进展。EMD Electronics就在2022年提到过纯度方面的突破,而且是有数量级的提升。这可能会成为DSA技术、BCP量产的关键。

最后值得一提的是,DSA的应用范围并不止于high-NA EUV的某一层,而是很多层,尤其低层级的金属层和via通孔。而且作为很早就被提上日程的一种技术方案,它也能用在并不需要high-NA的生产制造上,比如说DRAM的电容阵列,还有直接用在SADP/SAQP多重曝光之上。

说到底DSA就是一种图像修正、提高效率、缩减成本方案。至于它所惠及的市场参与者,实际上直接的并不在于Intel这样的foundry厂,而在于EMD Electronics, 应用材料, ASML, Lam Research这样的材料与设备供应商。

而且Intel也并不是唯一一个在DSA技术上做投入的foundry厂,台积电也已经在这项技术上做了据说有超过10年的投入。只不过既然Intel率先做出有关DSA的技术宣传,则这项技术大概率对Intel未来的先进工艺是至关重要的。