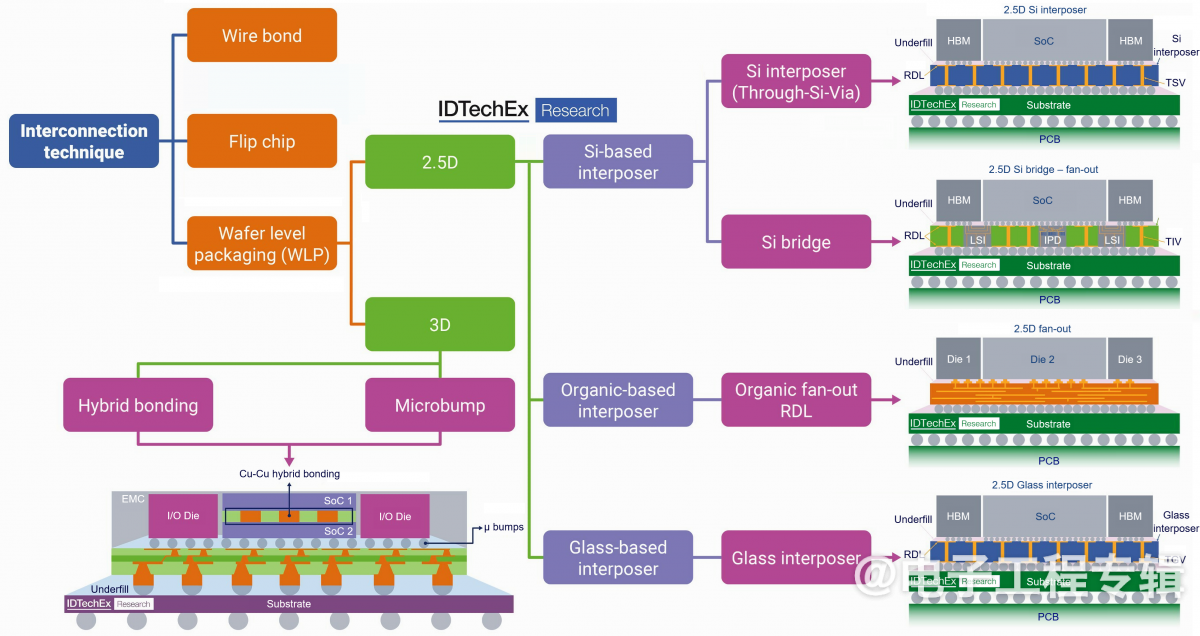

先进封装技术继2023年成为突出亮点之后,今年继续掀起波澜,并与半导体行业新星——芯粒(chiplet)的命运密切相连。IDTechEx公司的新报告“Advanced Semiconductor Packaging 2024-2034: Forecasts, Technologies, Applications”(2024-2034年先进半导体封装:预测、技术和应用)探讨了先进封装的现状,同时详细介绍了2.5D和3D封装等新兴技术(图1)。

图1:2.5D和3D封装有助于为AI、数据中心和5G等应用提供更高的芯片互连密度。(来源:IDTechEx)

晶圆厂通过各种先进工艺在硅晶圆上制造芯片后,封装厂从晶圆厂接收完成的晶圆,将其切割成单个芯片,组装或“封装”成最终产品,并测试其性能和质量。然后,这些封装好的芯片被运往原始设备制造商(OEM)。

这是传统半导体制造价值链的一部分,工程师在硅晶圆上构建片上系统(SoC),然后将其转入传统封装工艺。而芯粒则是在晶圆上以独立芯片或芯粒的形式制造单个系统模式,然后通过先进封装将这些独立功能集成到一个系统中。

这一前提将先进封装带入了半导体制造创新的前沿。事实上,芯粒的未来与先进封装的进步息息相关,2.5D和3D技术正在迅速成型,以促进芯粒的商业实现。

2.5D和3D封装

虽然1D和2D半导体封装技术在许多应用中仍占主导地位,但未来的发展与2.5D和3D封装有关,以实现超越摩尔的半导体境界。这些技术利用晶圆级集成实现元器件微型化,从而提高互连密度(图2)。

图2:2.5D和3D等先进封装技术通过提高I/O布线密度和减小I/O凸块尺寸来提高系统带宽和能效。(来源:西门子EDA)

2.5D技术有利于扩大封装面积,但必须从硅中介层转向硅桥或其他替代方案,例如高密度扇出技术。但是,将不同材料的元器件封装在一起也会带来许多挑战。IDTechEx的报告指出,找到合适的材料和制造技术是采用2.5D封装的关键。

其次,3D封装带来了新的结构。这包括将一个有源芯片集成到另一个有源芯片之上,并缩小凸块间距。这种3D技术称为混合键合,可用于CMOS图像传感器、3D NAND闪存和高带宽内存(HBM)以及芯粒等应用。然而,与2.5D封装一样,3D封装也面临着制造和成本方面的挑战,因为混合键合等技术需要新的高质量工具和材料。

外包半导体组装和测试(OSAT)与EDA的牵引力

生态系统的发展往往能为先进封装等新兴技术的未来提供重要线索。尽管挑战重重,但半导体行业最近发布的消息预示着2.5D和3D时代IC封装能力的发展前景良好。

Amkor是一家大型OSAT服务提供商,它将投资约20亿美元在亚利桑那州皮奥里亚建造一个先进的封装测试工厂。这座占地55英亩的工厂将在几年后投入生产。

Silicon Box是一家先进的面板级封装代工厂,专注于芯粒集成、封装和测试。该公司在新加坡建立先进的封装工厂后,又在意大利北部建立了一个新工厂,以便更好地为欧洲的晶圆厂提供服务。

EDA工具制造商也在关注这个前景广阔的新领域。例如,西门子EDA正与韩国OSAT厂商nepes紧密合作,为3D IC时代拓展IC封装能力。西门子EDA正在为nepes提供工具,以应对与开发先进3D IC封装相关的各种复杂的热、机械和其他挑战。

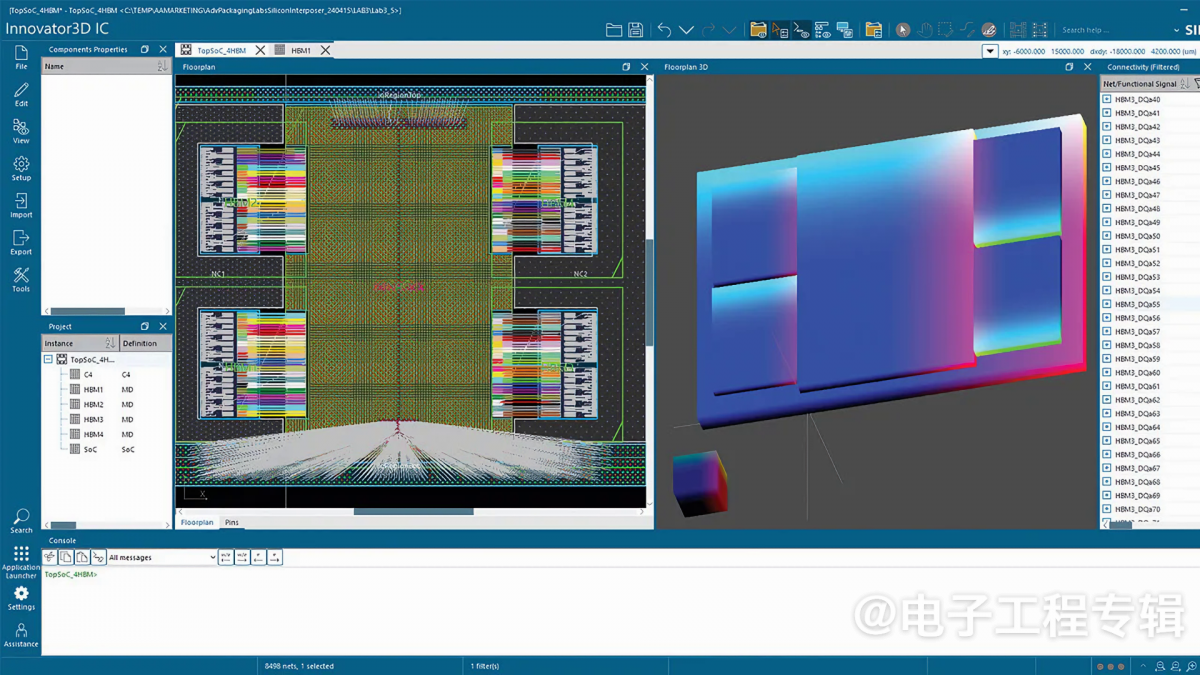

图3:Innovator3D IC软件为使用2.5D和3D封装技术的ASIC和芯粒的规划和异构集成提供了快速、可预测的途径。(来源:西门子EDA)

图3所示的西门子EDA Innovator3D IC工具集,采用分层器件规划方法来处理具有数百万个引脚的先进2.5D/3D集成设计的巨大复杂性。在这里,设计被表示为几何分割区域,其属性控制着详细设计和实现方法。这反过来又允许快速实施关键更新,同时将分析技术与特定区域相匹配,避免执行时间过长。

与此同时,新材料和制造工艺将继续得到开发,以应对2.5D和3D封装所面临的挑战。也许年底前的另一次更新将更加明确2024年及以后先进封装技术的发展方向。

(原文刊登于EE Times姊妹网站EDN,参考链接:Will 2024 be the year of advanced packaging?,由Franklin Zhao编译。)

本文为《电子工程专辑》2024年11月刊杂志文章,版权所有,禁止转载。免费杂志订阅申请点击这里。