在当今科技飞速发展的时代,材料的革新往往是推动技术进步的关键因素之一。碳化硅作为一种先进的新型材料,正逐渐在多个领域展现出其独特的优势和应用潜力。

在这场技术革命的前沿,安森美(onsemi)凭借其在碳化硅领域的深厚专业知识和创新解决方案,正引领着工业、汽车乃至航空领域的变革。

近日,安森美电源方案事业群的资深产品专家Dr.Mrinal Das接受了电子工程专辑分析师的采访,为我们揭开了碳化硅技术以及新平台EliteSiC M3e MOSFET背后的神秘面纱。

安森美电源方案事业群的资深产品专家Dr.Mrinal Das

用“棕地扩张”策略实现衬底供应自给自足

目前,碳化硅MOSFET的应用受到其高昂成本的限制。根据中国科学院的数据,同等级别的SiC MOSFET的价格是硅基IGBT的四倍。碳化硅衬底和外延层的成本分别占据了整个器件成本的47%和23%,合计大约70%,而后续的器件设计、制造和封装测试环节仅占30%。这与硅基器件的成本结构大相径庭,后者在晶圆制造上的成本约占50%(尽管碳化硅器件制造也包括晶圆制造,但其成本占比相对较低),而衬底成本仅占7%。

因此,降低碳化硅芯片的成本,成为该领域厂商的目标。降低成本的手段之一,则是通过采用更大尺寸的衬底,降低单位芯片的成本。

例如,当衬底尺寸从6英寸增加到8英寸时,可切割出的碳化硅芯片(面积为32mm²)数量预计将从448颗增加到845颗,增幅达到75%。

因此,国际上的领先企业正在将他们的碳化硅衬底生产从6英寸升级到8英寸。

据Mrinal Das 博士介绍,安森美目前已经建立了强大的生产线,特别是在6英寸晶圆的生产上,拥有高产量和整体产能能力。安森美也正根据市场需求,逐步从6英寸晶圆过渡到8英寸晶圆的生产。

Mrinal Das博士透露,安森美在降低成本、实现衬底供应自给自足方面的成功,部分归功于其“棕地扩张”策略,他表示:“对于安森美而言,我们在全球范围内拥有多家晶圆厂。这些晶圆厂仅需少量投资,便能实现碳化硅的生产能力,从而赋予我们灵活调配晶圆厂资源以适应市场需求的能力。然而,对于那些没有现成晶圆厂的企业,若他们希望进入碳化硅领域,就必须进行大规模的绿地投资,从零开始,自行筹备一切所需资源。这将导致资本投入显著增加。因此,像安森美这样的成熟企业,具备充分的能力灵活调整晶圆厂的运营,包括工艺和技术的优化组合。”

对晶胞结构进行创新,实现更低开关损耗

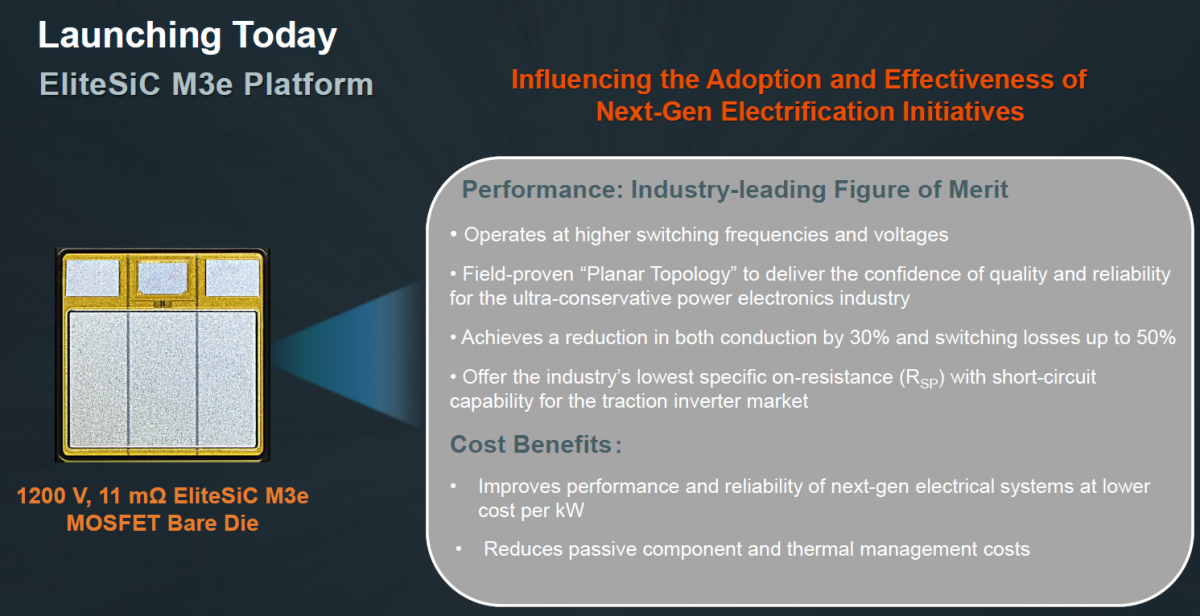

在全球电气化过渡的当下,面临低碳减排、高效能等需求,安森美于近期推出其最新一代碳化硅技术平台EliteSiC M3e MOSFET,据介绍,EliteSiC M3e MOSFET具有业界最低的导通电阻(RSP)和短路能力,与前几代产品相比,将导通损耗降低30%,关断损耗降低高达50%。

Mrinal Das博士强调了M3e业界最低的损耗主要归功于其独特的晶胞(Unit Cell)设计和内部创新。

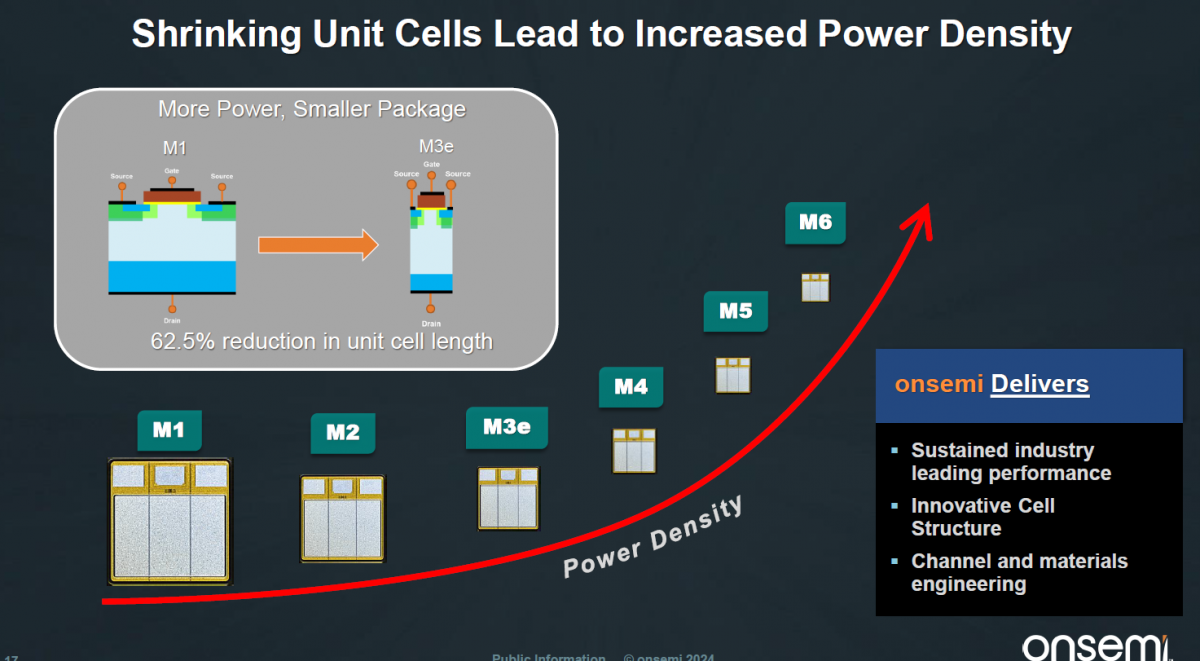

他解释说,晶胞在功率MOSFET设计中非常关键,它是整个芯片上不断复制的微型MOSFET的基本长度,包括两个导电通道。事实上,尽可能缩小晶胞就可以增加功率密度。晶胞体积越小,每个芯片上可以放置的MOSFET就越多,而这些MOSFET是并联的,所以整体的器件的电阻就会下降,晶胞本身的电阻也会下降。这两种效应组合起来,就能够进一步降低整个导通电阻,这是M3e导通损耗达到业界最低水平的主要原因。

具体来看,安森美的平面栅SiC MOSFET从最早的M1和M2已经迭代到M3S和M3e,主要的技术变化在于晶胞结构从四边形和六边形,变成了晶胞间距更小的条形结构,M3e的晶胞长度相比M1平台缩小了65%,并通过晶圆减薄工艺,实现了更大的功率和更小的封装,功率密度也在不断提升,从而降低了导通电阻。

另外,每个器件内部的开关损耗主要由电容决定,而主要的电容是栅极到漏极的电容。在M3e晶胞结构上进行的内部创新,使得栅极到漏极的电容更低,从而降低了整体的开关损耗。

此外,通过结合安森美最先进的分立和功率模块封装技术,在相同的牵引逆变器外壳中,M3e输出功率约提升20%,或者可以减少20%的SiC用量来达成同等功率水平,进而节省成本,并实现更小、更轻、更可靠的系统设计。

目前的沟槽MOSFET并未达到最佳性能

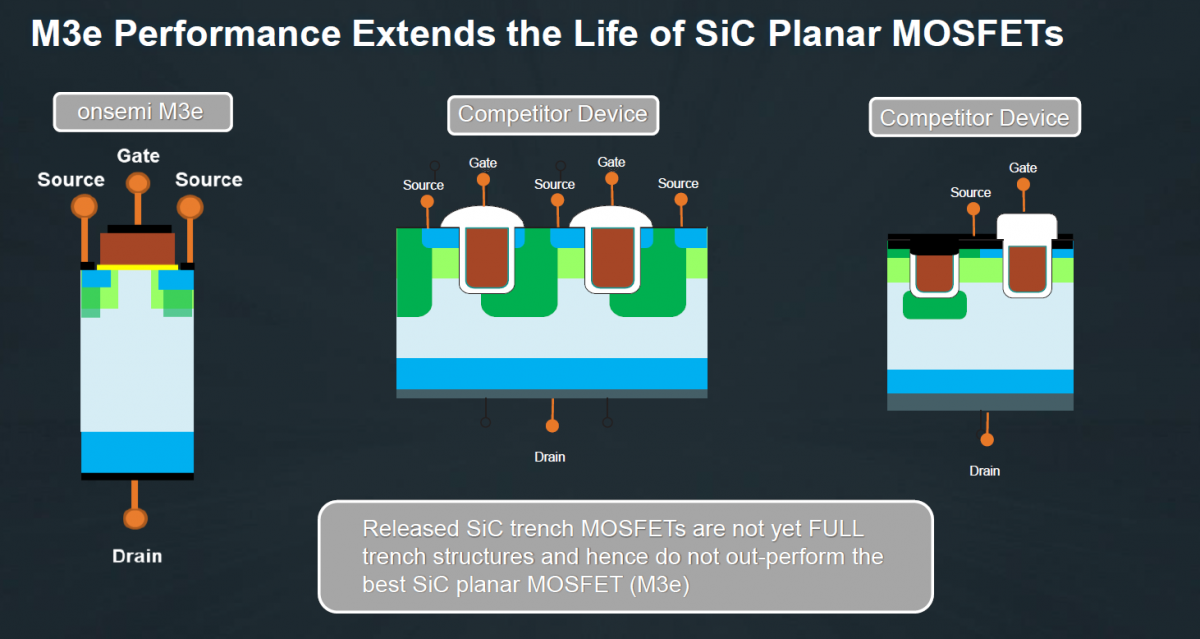

众所周知,目前碳化硅器件的技术路线主要有平面拓扑结构和沟槽拓扑结构两种。相较于传统的平面栅结构,沟槽型结构可实现性能的显著提升。槽栅结构通过减小栅极到漏极的电容(Cgd)和总体输出电容,能大幅降低开关过程中的能量损耗,加快开关速度,从而提高工作效率和频率响应。

但值得注意的是,M3e采用的并非沟槽拓扑,Mrinal Das博士介绍说,同样是平面结构,M3e采用了明显不同的结构,可以确保该平台的坚固性和稳定性,使其成为关键电气化应用的首选技术。

而针对平面拓扑与沟槽拓扑的争论,Mrinal Das博士认为,目前沟槽型碳化硅MOSFET还不是全沟槽结构,还难以体现沟槽结构的优势。其中一些结构采用多个源极和栅极,有的则只有一个源极和一个栅极,并没有达到最佳性能。

他介绍了硅与碳化硅材料在电场强度上的巨大差异,如硅材料的电场强度限于每厘米200-300千伏之间,而碳化硅则展现出惊人的电场承受能力,其峰值电场强度可达每厘米3000千伏,远超硅材料的10倍以上。他表示这种物理特性的不同,对沟槽器件的设计提出了更为严苛的要求,直接影响了器件设计特别是沟槽结构的应用。

平面结构中的栅极氧化层处于相对较低且更为安全的低电场区,而在沟槽结构中,栅极氧化层直接暴露于高电场环境下,必须采取特殊措施来保护其免受高电场的影响,以防止栅极氧化层失效,这种保护在碳化硅器件中尤为困难,因为碳化硅的栅极保护机制与硅不同,无法直接借鉴硅材料的经验。

Dr. Das 进一步分析了碳化硅沟槽技术与平面技术的差异。他解释说,虽然硅基平面结构的栅极氧化物形成过程与碳化硅平面结构相似,但碳化硅沟槽技术的实施则复杂得多。该技术要求在晶体表面精确控制硅与碳层的交替堆叠,以形成特定结构,随后再进行氧化处理。这一过程在沟槽侧壁上引入了碳元素,与平面结构的纯粹氧化物相比,产生了显著差异,这也成为了碳化硅沟槽技术推广道路上的重要障碍。

至于传统的平面设计方案,无论是M1、M2、M3还是最新的M3e,其氧化物制备工艺均基于长期验证的成熟技术,因此具有较高的稳定性和一致性。然而,当设计思路从平面转向沟槽时,氧化物的性质及制备工艺均需从头开始探索,涉及制造工艺、可靠性验证及现场表现等多个层面的全新挑战。

Mrinal Das博士表示,M3e这样的平面体结构MOSFET性能甚至优于当前的沟槽器件。而沟槽结构在碳化硅面积利用方面并未展现出显著优势,尚未超越平面拓扑结构。他说“只有当沟槽技术的产品性能能够全面超越平面拓扑结构时,我们才会考虑切换到沟槽技术。这表明我们在技术研发上持谨慎态度,注重产品的长期可靠性和性能表现。”

因此,安森美目前正全力以赴地应对新的挑战,解决新的栅极氧化物的保护问题,在2030年之前,他们还将以更快的速度将几款新的EliteSiC产品推向市场,预计从第四代开始全面转向沟槽栅SiC MOSFET。

构建更加可持续、电气化的未来社会

当前,业界普遍认识到提升效率和可持续性的重要性,但当可持续性路径伴随着高昂成本时,许多企业面临选择的困境。

Mrinal Das博士表示,在封装与裸片两个关键层面,不断降低成本是提升行业接纳度的关键。通过优化每千瓦的成本和技术创新,安森美实现了成本的显著降低,同时其封装技术也极具成本效益。这种双重优化确保了裸片层面的创新能够无缝转化为系统层面的优势,且不增加额外成本。

此外,安森美拥有强大的产品组合,不仅包括功率器件,还与合作伙伴紧密合作,不断迭代升级其系统和解决方案。不仅仅是组件的优化,而是对整个系统的全面升级,包括引入栅极驱动器、控制器等先进技术。

Mrinal Das博士表示:“安森美正在加速推动其解决方案在行业中的广泛应用,旨在构建一个更加可持续和电气化的未来社会。”