在2023年11月举行的北美RISC-V峰会上,Imperas公司(现已并入Synopsys公司)首席执行官Simon Davidmann发表了一场令人意想不到的主题演讲。他传达的信息是:尽管RISC-V代表着巨大的进步,但如果对其质量的关注不够,最终可能会限制其发展潜能。这是许多利益相关者的共同看法。

Davidmann接着解释说,Arm和英特尔等公司已经为整个半导体行业设定了质量期望。这些公司的处理器极少出现错误,用户依赖于这种质量水平,因为一个处理器错误就可能导致最终产品夭折。Davidmann指出,Arm每年在验证方面的投入超过1.5亿美元,每个内核的验证时钟周期达到惊人的1015个(超过一光年的里程数),并拥有30年的经验。由于保留了对指令集的完全控制,这一切变得更加容易。

RISC-V用户期望这种“Arm质量”水平,因为没有它,他们的设计就会失败。但是,RISC-V内核提供商如何才能达到这一质量目标,又如何予以证明呢?

RISC-V:新的处理器思维

在RISC-V问世之前,大多数处理器指令集架构(ISA)——用于驱动器件的基本代码规范——都是开发处理器的公司受保护的知识产权。这种保护对公司来说至关重要,因为它可以控制生态系统并阻止竞争,从而实现有利的商业模式。

随之而来的是RISC-V开放式ISA。所有公司都可以使用该指令集来实现其处理器、软件栈、工具和其他生态系统元素。商业模式不再受ISA版权的制约。此外,RISC-V ISA比其他ISA更加灵活,允许加入差异化的自定义指令。

半导体行业对此热情高涨。巧合的是,Arm不受欢迎的商业模式转变也促使各公司启动RISC-V计划,RISC-V因此获得了相当大的发展势头。据BCC Research公司估计,2021年RISC-V技术的市场规模为5亿美元,预计增长率为33%,到2027年将达到27亿美元。1如今,ISA管理机构(RISC-V International)报告称,该机构拥有来自70个国家/地区的3,950名成员,市场上有130亿个RISC-V IP核。

可以说,迄今为止RISC-V市场最重要的特点之一是,这130亿个处理器中的大多数都是相对较小的嵌入式器件。但是,我们现在看到的是复杂系统中更大型多核应用处理器的出现,由于处理器的复杂性要高得多,因此不可避免地会对验证解决方案产生影响。

为此,RISC-V国际基金会成立了一个认证委员会,以满足对RISC-V可证明质量基准的需求。

验证处理器

处理器验证是一项复杂的工作,涉及的方面太多,本文无法一一列举。但是,即使是简单的单核嵌入式器件,也可以通过大量指令的无限组合,使器件做出多种不同的反应。

智能随机指令生成器通常用于对架构进行更肤浅的检查。要根据应用的指令流检查处理器是否做了正确的事情,需要使用自检测试或RISC-V处理器的黄金模型进行比较,而这两种方法都很难实现。指令类型和组合非常重要。检查分支预测、验证指令权限级别和确保正确处理异常只是其中几个例子。

指令测试的另一个方面是确保符合官方ISA规范。目前有各种测试,但它们只能实现架构测试的部分要求。

指令级架构测试只是一个开始。高达80%的处理器执行由加载存储操作,这些操作必须高效。中断机制和许多其他接口要求也是如此。功能操作和性能相关问题必须一并检查,因为读写危险可能会导致难以调试的意外问题。这种协同工作需要进行深入的微架构测试,这反过来又需要结合不同测试集的测试综合,以剔除复杂、不可预测的极端情况。

还应在片上系统中对内核进行测试。根据内核(或多核)的复杂性,我们会发现一致性问题、安全漏洞和复杂的中断等等。

这是极端的验证,也是促使像Arm这样的处理器公司投入巨资的原因。指望一个小团队来构建这样的验证环境是不合理的。小团队要达到适当的验证水平,唯一的办法就是大量重复使用测试内容。

通用ISA的一个优势是,它可以让多个团队通过组合测试套件来联合起来。针对RISC-V的系统级验证知识产权组件(SystemVIP)就是这种通用可重用测试集的载体。采用这种方法,商业机构或其他组织可以利用规模经济建立通用测试集,将投资分摊到许多内核开发中。这正是商业验证公司以及包括谷歌在内的公司开源项目的目的。

当然,这种合作在商业竞争实体之间很难实现。然而,一个共同的组织可以推动这样的举措,RISC-V国际基金会正在这样做。

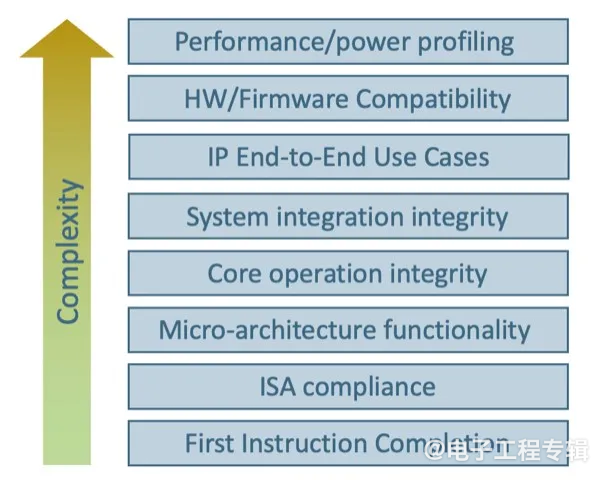

典型的RISC-V验证堆栈是一项复杂的工作,需要全面的测试计划。(来源:)

RISC-V认证

RISC-V国际基金会和其他组织已经实施了RISC-V ISA合规性测试套件。虽然该套件是一个有益的开端,但它还不够全面,不能完全依赖于它。RISC-V国际基金会的董事会认识到,有必要制定一项严格的认证计划,为处理器供应商提供对其器件性能的独立评估,从而提供客户可以信赖的信息。

其他行业标准也有认证计划,例如Wi-Fi、USB和PCIe。虽然这些接口协议需要大量的测试套件,但它们的验证比验证整个处理器内核简单。毫无疑问,Arm和英特尔为其新内核制定了内部签核流程,但这些流程都是专有的。因此,像处理器内核这样复杂、可应用于各种内核架构的器件,以前从未有过这种性质的公共认证计划,这是一项艰巨的挑战。

RISC-V董事会最近成立了RISC-V认证指导委员会(CSC),以完成这项任务。委员会成员包括RISC-V商业用户、处理器提供商、测试套件提供商以及该领域的其他专家。该委员会是新成立的,但正在积极制定具体计划,解决可能使用的测试、计划如何运行、测试在多大程度上检查整体架构以及其他定义问题。到今年年底,CSC应该有一个全面的计划,并将顺利实施。

RISC-V董事会完全希望CSC能够为最复杂的器件提供质量认证,从而为RISC-V处理器的全面部署扫除一个关键的潜在障碍,使其为整个半导体行业所接受。这绝非易事,需要广泛的专业知识才能达到以前在公共领域从未见过的验证水平。但是,我们必须使RISC-V内核达到与商用内核相同的质量要求。

RISC-V将变得更加可靠。

参考文献

1BCC Research (December 2022). “RISC-V Technology: Global Market Outlook.”

Dave Kelf是Breker Verification Systems公司的首席执行官,该公司的产品组合可应对大型复杂半导体功能验证过程中的各种挑战。Kelf拥有英国索尔福德大学电子计算机系统理学学士学位和布鲁内尔大学微电子学理学硕士学位,以及波士顿大学工商管理硕士学位。

(原文刊登于EE Times欧洲版,参考链接:Certifying RISC-V: Industry Moves to Achieve RISC-V Core Quality,由Franklin Zhao编译。)

本文为《电子工程专辑》2024年10月刊杂志文章,版权所有,禁止转载。免费杂志订阅申请点击这里。