MIPS公司目前正针对其特定应用数据移动内核开展人工智能(AI)应用,并在发展过程中审慎地关注自身优势。“MIPS必须做出选择,因为我们的大多数RISC-V竞争对手也在公开或不公开地大力转向AI。”MIPS公司首席执行官Sameer Wasson(图1)告诉笔者,“我们做出的选择是,着眼于别人没有很好解决的问题,并尝试将其与我们的强项相匹配。”

对于MIPS来说,这意味着数据移动——这是MIPS深厚的历史和专业知识,也是高性能AI芯片和系统的绝对关键。

“我们要解决的问题是打造最好的数据处理引擎。”Wasson指出,“相对而言,这项任务可能没有那么热闹(与AI IP相比),但坦率地说,我对此非常满意,因为它能让我们低调行事。”

MIPS公司首席执行官Sameer Wasson

长期以来,客户一直在为数据移动构建自己的专有内核,他补充说。MIPS希望取代这些专有内核。

“AI架构需要发展。”Wasson认为,“数据移动引擎将成为DPU,而从CPU或GPU卸载成为关键。这样,我们才能实现300Gb/s、3Tb/s或各种所需的速度。”

更高效的数据移动能够提高CPU、GPU和加速器的利用率,从而有助于解决数据中心的功耗问题,并通过提高数据移动效率来改善散热问题。

MIPS认为,其DPU内核在当今数据中心AI系统的多个地方都有用武之地。这包括从主机CPU卸载数据移动,使用并行性和多线程技术对网络数据进行内联处理,就像MIPS的一个智能网络接口卡(SmartNIC)客户所做的那样。数据移动的新兴应用包括AI内存和存储,以及GPU和定制AI加速器。

Wasson对新的内存技术——智能计算快速链路(CXL)架构或智能双列直插式存储模块(DIMM)——的潜力尤其感到兴奋,MIPS的多线程、PPA优化的RISC-V内核在这些领域发挥了很好的作用。

“到目前为止,我们一直在将数据引入控制端进行处理。”他表示,“如果我们将控制器转移到数据端会怎么样?这是近内存计算……总可用市场(TAM)是巨大的。”

我们的愿景是将小型计算内核嵌入内存,而不是相反。随着支持CXL的内存池成为现实,我们将有机会进行一些预处理,例如流量整形和优先级划分。

“从系统层面考虑流水线问题,”他说,“首先需要哪些数据?接下来需要哪些数据?即使每个事务只节省几微秒的时间,但考虑到事务的数量,这些微小的节省也会累积起来,从而提高CPU的利用率,减少所需的CPU数量,并最终降低整体功耗。”

Wasson表示,数据中心客户如今将内存视为资本支出(CapEx)和运营支出(OpEx)问题,当内存池闲置等待计算时,运营支出尤为糟糕,反之亦然。

“你不能把x86内核放到那里,因为那仍然是一个大内核。”他指出,“想想小型处理任务——面向数据的实时处理任务。这才是未来的发展方向。”

存储同样是高效AI数据移动的一大机遇,他认为。

GPU和AI加速器是一个新兴的机会。GPU中的处理分为标量、矢量和矩阵乘法。矩阵乘法加速得到了很多关注,但标量部分呢?

“从很多方面来看,标量是最无聊的部分,但从很多方面来看,它也是最困难的部分,因为只有三家公司在做。”Wasson指出,“如果你既能迎合定制加速器的新兴市场,又能使编程模型标准化,那你就能解决最大的问题,那就是软件,而不是硬件。”

数据移动

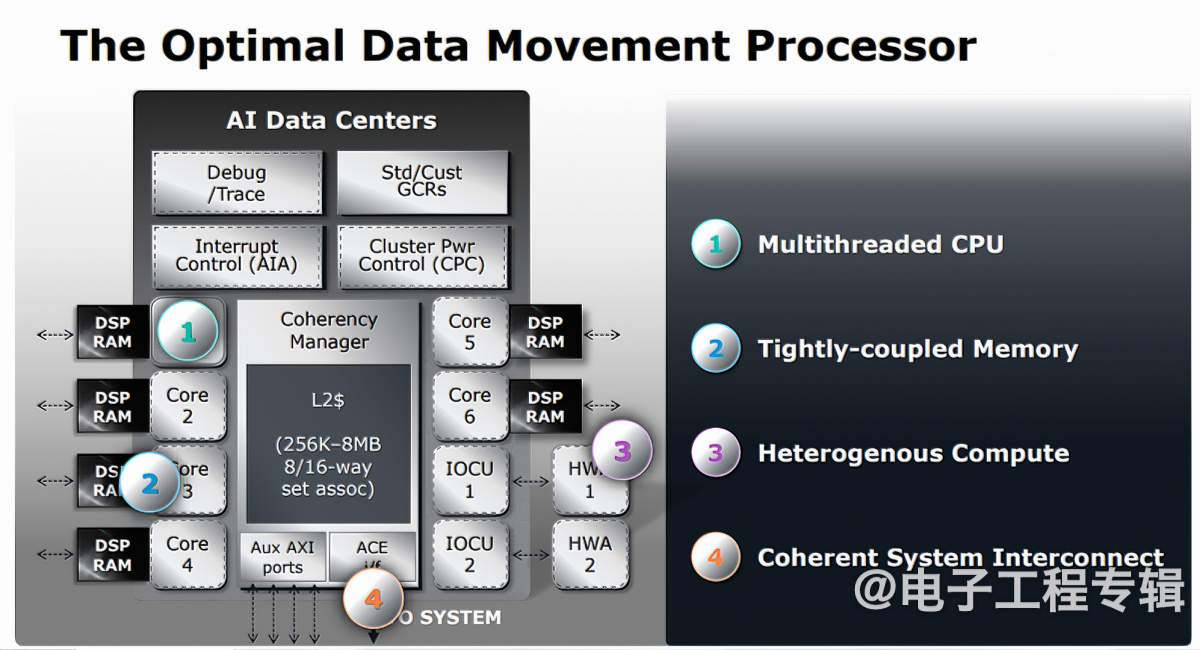

MIPS内核的主要特点包括硬件多线程功能和紧耦合内存,以及实现异构计算和一致系统互连的能力(图2)。这些特点共同构成了MIPS的特性,Wasson喜欢用“MIPSiness”这个词来形容。

“这基本上是MIPS的传统——MIPSiness发扬光大。”他表示。

图2:MIPS内核具有硬件多线程和紧耦合内存的特点。(来源:MIPS)

MIPS数据移动解决方案通常是一组内核,并且通常都是同一种内核(MIPS有P内核和I内核,前者是无序内核,后者是有序内核),再加上MIPS一致性管理器。

“大客户之所以喜欢MIPS,是因为我们允许他们以本机格式将自定义加速挂接到流水线中。”Wasson以自动驾驶汽车(AV)芯片制造商Mobileye为例说,“这意味着更好的性能和成本。”

紧密耦合的内存使自定义加速器、矢量引擎或DSP具有低延迟,而硬件多线程和硬件虚拟化等功能则增加了灵活性。

所有这些功能都是通过自定义指令实现的。MIPS正在继续投资其工具,以允许客户添加自己的指令。这种功能以前曾在MIPS ISA中广泛使用。

“我们的研发工作中有15%到20%是工具开发,但我们不是一家工具公司。”Wasson说道,“我们是一家计算和IP公司,我们为客户提供工具,使他们能编写自定义指令,但我们仍然负责提供性能。”

Wasson补充说,MIPS的客户参与模式是其IP的关键部分。

“这里有一条价值链,作为一家计算IP公司,我们必须清楚自己能带来什么价值。”他指出,“我们的价值不在于超越客户。我们是客户的使能力量,我希望确保这一点。”

转向RISC-V

MIPS于2018年从MIPS ISA转向RISC-V。Wasson表示,向RISC-V过渡有两种方式:一种是在ISA基础上构建翻译器,大约需要六个月;另一种是进行全面过渡,这可能需要六年的时间。MIPS选择了后者。

“过渡到RISC-V绝对是一个正确的决定。”Wasson说,“专有架构的存在是出于传统原因,也是因为硬件工程师掌控着半导体世界。但我们的客户是软件工程师。我们要迎合我们的客户群,就是这么简单。”

Wasson认为,RISC-V带来了标准化的好处,同时允许充分的差异化实现,从而使MIPS能够保持其MIPS特性。

他说:“由于RISC-V的市场推广方式,市场上缺乏教育。”他指出,大多数人认为RISC-V是潜在的Arm杀手。“这样的故事很能迎合媒体报道和投资者的口味,但我认为这种说法限制了它的潜力。如果能从系统的角度考虑RISC-V所能做的,它的潜力会大得多。”

RISC-V可以保持系统的异构性,同时提供同构的ISA,他指出。

“如果你想改变系统,让它偏重于数据处理,可以这样做。”他谈道,“如果你想让系统偏重于信号处理,或者让它偏重于自定义加速,也都可以。因此,从软件的角度来看,想象一下它所带来的简便性。”

如今的SoC可能包含Arm内核、DSP和自定义加速器,它们各自采用不同的ISA,这就给软件开发人员带来了使用多个编译器的挑战。Wasson指出,RISC-V能够降低这种复杂性,并最终降低成本。

“根据我们在客户方面观察到的情况,人们已经开始使用RISC-V来解决SoC上的几乎所有问题。”他指出,“这将推动下一轮创新,即简化软件堆栈并专注于实际问题,而非尝试管理多个堆栈。”

当然,Wasson认为Arm不会消失,但RISC-V最终将取代许多专有ISA,因为客户需要标准架构和标准工具。

现有的MIPS客户将需要为新的MIPS RISC-V内核重新编译,但Wasson表示,考虑到公司采取有目的的设计决策,过渡过程应该会很简单。

“软件是为机器定义的,具有多线程和缓存一致性等特点。”他指出,“当我们从MIPS ISA过渡到RISC-V ISA时,我们并没有过渡到通用内核,而是保持了MIPS特性。在某些情况下,甚至内存映射都是完全一样的……客户多年来编写和维护的应用代码或固件根本不需要做太多的改动。”

客户的痛点通常是围绕从Arm迁移到RISC-V而产生的,他指出。不过,他预计,从Arm迁移到RISC-V的长期(未来7至10年内)客户仅占其客户群的三分之一左右。剩下的将是解决新兴问题的客户。

应用重点

保持MIPS特色的一部分是保持公司对应用的强大关注。在AI数据移动方面,MIPS的重点是为数据中心的AI以及高级驾驶辅助系统(ADAS)和AV提供定制产品。

这些细分市场分为数据中心的DPU、内存、存储和新兴的GPU/加速器领域的数据移动。汽车应用包括软件定义汽车、电动汽车和ADAS等注重延迟的应用。

“了解这些面向应用的技术,将使我们能够与专有架构竞争,因为坦率地说,那里正是它们大显身手之处。”Wasson指出。

Wasson的计划是将MIPS的重点限制在几个关键应用上,并坚持做一家IP公司(没有成为硅片供应商的计划)。

“这就是作为一家IP公司的优势所在。”他说,“如果你专注于自己的优势和特定应用,你仍然会发现有许多人愿意构建这项技术,因为你将为许多SoC人员和许多系统人员提供服务。因此,你的TAM确实会扩大,因为你是一家IP公司。”

2018年,MIPS被首批AI芯片初创公司之一的Wave Computing收购,但后者最终破产。然而,在Wave内部一直被视为独立业务部门的MIPS却仍然蓬勃发展,并保留了Wave的IP。那么,Wasson近期是否有计划推出AI加速器IP核?

“一次只做一件事!”他笑着回答说。

(原文刊登于EE Times美国版,参考链接:Addressing AI While Keeping the MIPSiness In MIPS,由Franklin Zhao编译。)

本文为《电子工程专辑》2024年10月刊杂志文章,版权所有,禁止转载。免费杂志订阅申请点击这里。