随着人工智能技术的迅猛发展,对高性能计算的需求日益增加,高带宽存储器成为了AI芯片性能提升的关键要素之一。HBM是高带宽内存(High Bandwidth Memory)的缩写,是一种先进的DRAM芯片,对于AI的发展至关重要,因为它提供了比传统内存芯片更快的处理速度。

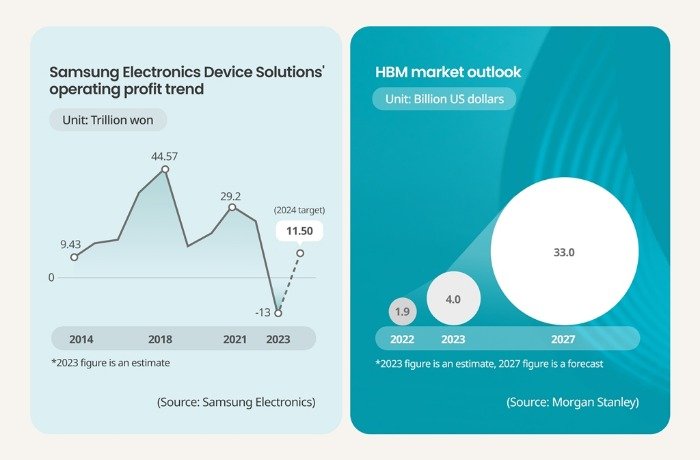

摩根斯坦利关于HBM市场的展望

而HBM4作为第六代HBM芯片,不仅在能效上较现有型号提升40%,延迟也降低了10%,成为各大芯片厂商竞相追逐的焦点。据韩媒《韩国经济日报》和《Business Korea》报道,三星电子与台积电这两家在代工领域是对手的半导体巨头,如今已达成合作,共同致力于开发下一代无缓冲(buffer-less)HBM4芯片。

这将是两家公司在AI芯片领域的首次合作,真可谓“没有永远的盟友,也没有永远的敌人”。

合作详情

三星电子内存业务负责人李正培在9月3日的CEO峰会上表示,为了最大限度地提高AI芯片的性能,定制化的HBM是最佳选择。“仅凭现有的内存工艺提升HBM性能存在局限性,我们将结合三星系统LSI和内存事业本部的设计、生产能力和代工厂的制造能力,将HBM性能发挥到极致”,他补充道,“我们正在与其他代工厂合作,准备20多种定制化解决方案”。

会后,李正培并未回答记者关于与哪些代工厂合作的问题。

9月5日,台积电生态系统和联盟管理负责人Dan Kochpatcharin在Semicon Taiwan 2024论坛上证实,三星与台积电正携手开发无缓冲的HBM4芯片。“随着内存制造过程变得越来越复杂,与合作伙伴的合作变得越来越重要。”

HBM4的制造方式大不同

无缓冲HBM4是一种消除了用于防止电气问题和管理电压分布的缓冲器的产品,相比传统HBM设计具有更高的集成度和更低的功耗,能够大幅提升AI应用的性能和效率。

据行业人士透露,这种新型芯片将特别适用于需要大规模并行处理和高速数据传输的AI场景,如深度学习、自动驾驶和超级计算等。HBM4的制造工艺与前几代产品有显著不同,使其作为一个芯片顺利运行的先进封装方法也将发生变化。

一种解决方案是使用逻辑工艺将 base die (基础芯片)外包给代工厂,然后通过硅通孔 (TSV) 技术将其与内存集成,以创建定制的 HBM。也就是说,今后作为HBM大脑的逻辑芯片将由代工厂而非内存公司制造。此外,之前GPU和HBM是水平排列的,但今后很有可能采用将HBM置于GPU上方的“3D-IC”方式。

三星电子的基本策略是提供“交钥匙解决方案”,从代工厂的DRAM生产到逻辑芯片量产和先进封装,一应俱全。同时保持灵活性,允许客户设计自己的base die,而不将生产限制在三星的代工厂。

紧咬海力士和美光

CoWoS封装与HBM的集成度提高进一步巩固了台积电作为CoWoS服务主要提供商的地位。双方此次合作,不仅是技术上的强强联合,也是对未来AI市场布局的重要一步。

对于AI芯片厂商而言,HBM4的量产将为他们提供更加强劲的计算能力支持,助力他们开发出更高性能、更低功耗的AI芯片产品。而对于终端用户而言,这将意味着更加智能、高效的AI应用体验。

此外,三星和SK海力士在论坛上分享了各自在HBM方面的不同策略。SK海力士目前是英伟达(Nvidia)HBM3 AI芯片的最大供应商,他们已于今年4月宣布与台积电合作生产HBM4芯片,台积电将使用其12nm工艺负责SK海力士base die的生产,计划在2026年量产。

市场研究公司TrendForce的数据显示,2023年,SK海力士和三星电子各占有HBM市场47.5%的份额,但是预计2024年三星的市占将会下降到42.4%,SK海力士上涨到52.5%,美光基本维持不变。尽管比 SK 海力士和美光晚了几个月,但据报道三星的 8 层 HBM3e 已开始向 英伟达发货,他们的目标是在 HBM4 方面与竞争对手取得竞争优势,并计划在 2025 年底前投入量产。

对于HBM4e代,TrendForce预计三星和美光都将更倾向于将基础芯片的生产外包给台积电。这种转变主要是由于需要提高芯片性能并支持定制设计,这使得进一步的工艺小型化变得更加关键。

据悉,三星对HBM市场持乐观态度,预计今年HBM市场将达到16亿Gb,是2016年至2023年总和的两倍,凸显HBM的爆炸式增长。