英特尔的嵌入式多裸片互连桥(EMIB)技术,旨在解决异构集成多芯片和多芯片(多芯粒)架构日益增长的复杂性,在今年加利福尼亚州旧金山举行的设计自动化大会(DAC)上掀起了波澜。它提供了先进的IC封装解决方案,包括规划、原型设计和签核,涵盖了2.5D和3D IC等广泛的集成技术。

在DAC大会上,英特尔展示了与主要EDA和IP合作伙伴的合作关系,以确保他们的异构设计工具、流程和方法以及可重复使用的IP模块能够完全支持EMIB组装技术并获得认证。

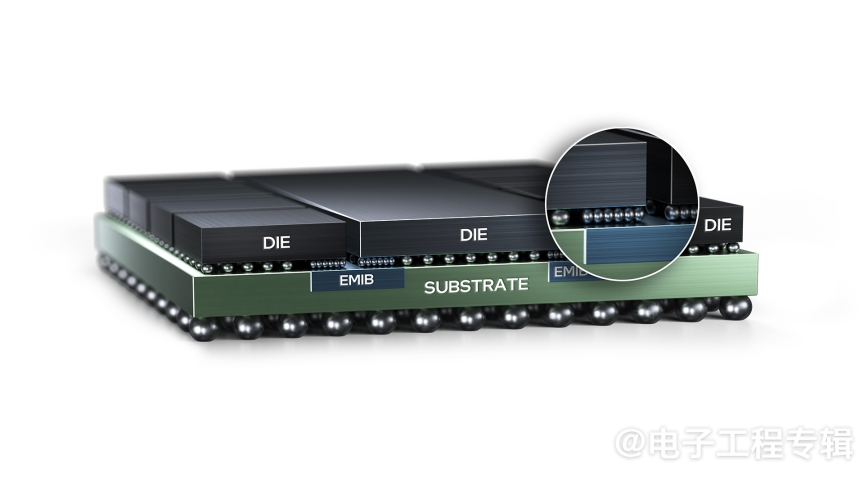

图1:封装内部嵌入硅桥,用于连接多个裸片。(来源:英特尔)

这些举措的核心是英特尔代工厂的封装组装设计套件(PADK),它使工程师能够创建基于EMIB的封装设计。英特尔的PADK包括设计指南、规则和堆栈,使芯片设计人员能够高效地完成和验证EMIB设计,旨在解决芯片设计的复杂性,促进EDA工具的支持。

PADK实现的参考流程支持所有主要EDA供应商的工具,以促进PADK驱动的组装验证。以下是英特尔代工厂最近与主要EDA供应商在EMIB支持方面的合作情况。

与EDA三巨头的合作

1.西门子EDA

在DAC 2024大会上,西门子EDA宣布了EMIB支持工具认证,用于设计高度复杂的IC和先进封装。这些认证包括Solido SPICE(Solido仿真套件软件的一部分),适用于代工厂的英特尔16和英特尔18A工艺节点。

此前,西门子EDA于2024年2月宣布推出EMIB参考流程,让设计工程师能够进行早期封装组装原型设计、分层器件布局规划、协同设计优化以及完整详细实现的验证。该参考流程围绕英特尔代工厂的PADK构建,使工程师能够完成成功设计和流片所需的所有关键任务。

图2:EMIB参考流程使设计工程师能够为异构芯片创建高密度互连。(来源:西门子EDA)

2.新思科技(Synopsys)

Synopsys还在DAC 2024大会现场展出了英特尔代工厂的多裸片参考流程。该参考流程由Synopsys.ai EDA套件提供支持,旨在利用EMIB组装技术为设计人员提供全面、可扩展的快速异构集成解决方案。

该参考流程由Synopsys 3DIC Compiler支持,提供统一的协同设计和分析解决方案,以加速从硅片到系统各个阶段的多裸片设计开发。此外,与Synopsys 3DIC Compiler原生集成的Synopsys 3DSO.ai还可实现信号、电源和热完整性的优化。

目前正在被Synopsys收购的电热工具供应商Ansys,也在为英特尔的2.5D芯片组装技术提供多物理场签核解决方案,该技术采用EMIB技术灵活连接裸片,无需硅通孔(TSV)。其RedHawk-SC电热EDA平台可对具有多个裸片的2.5D和3D IC进行多物理场分析。

3.楷登电子(Cadence)

EDA三巨头中的另一家公司Cadence也与英特尔代工厂联手认证了利用EMIB技术的集成先进封装流程,以应对异构集成多芯片(多芯粒)架构日益增长的复杂性。该EMIB流程使设计团队能够从早期的系统级规划、优化和分析无缝过渡到DRC感知实现和物理签核,而无需在不同格式之间转换数据。

EDA工具支持

英特尔几十年来一直引领着封装技术的发展,现在又推出了两种先进封装技术,通过在单个封装中连接多个裸片来缩小硅片面积。EMIB在一个封装中并排连接多个芯片,而Foveros则以3D方式将芯片堆叠在一起。

英特尔公司产品和设计生态系统支持副总裁兼总经理Rahul Goyal表示,与传统堆叠技术相比,EMIB技术体现了一种与众不同的多裸片组装方法。英特尔已在自己的芯片中采用了EMIB技术,包括GPU Max系列(代号为Ponte Vecchio)、第四代英特尔至强和至强6处理器以及英特尔Stratix 10 FPGA。

图3:英特尔代工厂开发的EMIB可在单个封装中连接多个裸片。(来源:英特尔)

然而,与其他先进封装技术一样,EMIB也对多裸片架构的设计和封装复杂性提出了新挑战。因此,将各种EDA工具整合到英特尔的PADK中是一个良好的开端。它将帮助芯片设计人员有效、高效地实施和验证EMIB设计。

(原文刊登于EE Times姊妹网站EDN,参考链接:Intel bolsters EMIB packaging with EDA tools enablement,由Franklin Zhao编译。)

本文为《电子工程专辑》2024年9月刊杂志文章,版权所有,禁止转载。免费杂志订阅申请点击这里。