对于大多数片上系统(SoC)设计而言,最关键的任务不是RTL编码,甚至不是创建芯片架构。如今,SoC主要是通过组装来自多个供应商的各种硅片知识产权(IP)模块来设计的。这使得管理硅片IP成为设计过程中的主要任务。

一般来说,在新的SoC设计中,只有不到十分之一是新编写的RTL代码。通常情况下,高级芯片架构决策会很明确:现有架构的变体或应用中主要数据流在标准总线或片上网络(NoC)结构上的分层反映。

但设计中的每个IP(可能有数十种类型和数百个实例)都需要管理。芯片设计人员必须确定需求,选择供应商和特定产品,进行任何必要的定制,设置配置参数,并将IP实例集成到可工作、可测试的系统中。在物理设计之前,这一过程将耗费大部分项目资源。

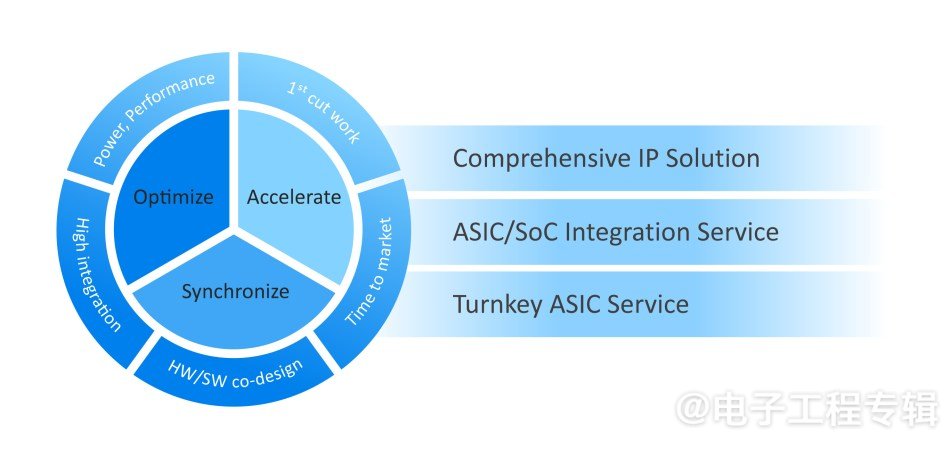

这一现实使得管理IP的专业知识成为SoC设计成功的重要因素(图1)。也许不那么明显的是,IP的获取,特别是获得大型、有影响力的IP供应商的关注、详细规格和文档、错误修复和定制支持的能力,成为一个关键问题。IP模块的复杂性不断增加,这只会使挑战更加严峻。

图1:IP管理是SoC设计成功的重要考虑因素。(来源:Faraday Technology)

重要的合作伙伴关系

这种情况为我们熟悉的设计合作伙伴关系增加了新的内容。许多SoC设计团队都利用设计服务公司来补充其团队的特定技能,例如进行物理设计。

在某些情况下,这种补充已扩大为一种全面的合作伙伴关系,设计合作伙伴承担了设计过程中的许多步骤。在极端情况下,客户在开始合作时可能只有SoC的功能描述或餐巾纸上的草图。

然而,随着IP成为关注的焦点,客户要求设计合作伙伴也承担起IP管理的责任。事实上,这对客户来说是一个强有力的杠杆。让我们来看看这种新的合作伙伴关系都包含什么,以及它对理想的设计合作伙伴意味着什么。

灵活参与

只有少数SoC设计合作关系是在一张潦草的餐巾纸上开始的。然而,在更多情况下,客户对某些主要IP模块只有概念上的了解。例如,客户可能知道他们需要一个用于物联网(IoT)芯片的低功耗人工智能(AI)加速器模块。但是,他们可能对这些复杂模块在不同模型下的性能或内部结构知之甚少。

或者,一个团队可能正在为其SoC中的新功能编写代码,但却不知道如何选择和配置RISC-V CPU内核,以便在时序和功耗限制内执行新代码。还有一个客户可能非常清楚其设计的UCIe接口要求,但却不知道如何配置任何可用的UCIe接口IP模块来满足这些要求。

这些差异使得灵活的参与至关重要。设计合作伙伴应该能够在所有级别(从概念到网表)加入项目,并与客户的设计团队顺利对接。最初的目标是与客户一起完善IP要求——从概念到功能规范,再到详细的接口、功耗/性能/面积和布局要求——这样合作伙伴才能为设计中的每个实例选择最佳IP。

IP选择

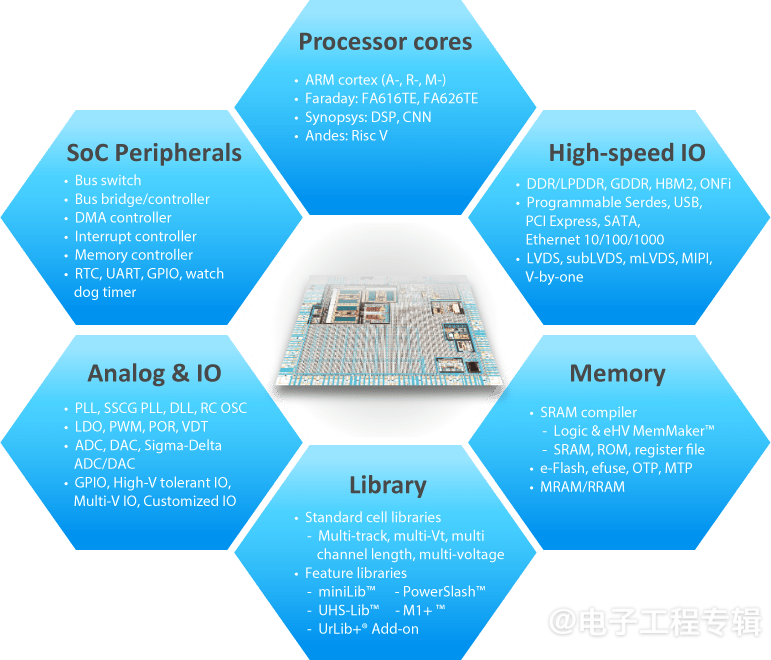

有了需求之后,客户和设计合作伙伴将选择要使用的IP(图2)。此时,合作伙伴的角色与传统意义上的雇佣一群优秀的设计人员不同。合作伙伴与IP供应商的深度关系变得至关重要。

图2:IP选择现已成为SoC设计项目的关键部分。(来源:Faraday Technology)

理想的情况是,合作伙伴在内部开发并维护其广泛的IP库。这样,合作伙伴就能迅速将需求与库存进行匹配。如果匹配结果接近但不完美,IP开发团队拥有文档、工具和资源,可根据客户的具体需求定制IP模块。

在选择、定制和授权IP方面,除了需要技术娴熟的设计工程师之外,合作伙伴还需要具备许多其他优势。在设计这些模块的团队支持下,一个广泛的内部硅片验证IP产品组合是一个巨大的优势。

在某些情况下,也会出现无法完全匹配的情况。这就需要IP外包团队,这是一个专门负责建立和维护第三方IP关系的工程团队。这样的团队拥有庞大的全球IP供应商网络,确保能够满足客户的要求。

与第三方IP供应商建立久经考验的IP授权和开发关系的全球网络,以及专门负责维护该网络的团队,是至关重要的。客户应特别调查潜在设计合作伙伴与Arm以及不断发展的RISC-V提供商生态系统的关系。

IP集成

设计合作伙伴还将深入参与IP集成。我们必须对IP实例正确配置,然后将其连接到芯片的底层总线或网络架构。必须验证组装后的SoC设计是否能正确运行。除了功能设计之外,还必须解决测试架构、电源管理和时钟架构等重要问题,最好是统一解决。

第一步是连接,首先要选择具有必要接口的IP模块。但是,某些模块可能需要定制才能完美满足接口要求。在其他情况下,集成团队可能需要在设计区域之间创建包装器、控制器或网关。拥有这种内部专业知识的大型IP设计团队可以节省大量时间。

验证同样是一项挑战。通常情况下,一个IP模块在组装后的SoC设计中的表现并不符合预期或描述。在这种情况下,内部IP设计团队就显得弥足珍贵。即使是外部IP,设计合作伙伴通常也能在引入第三方供应商的情况下解决问题。

详细了解IP模块的内部结构对于电源管理和测试设计也很有价值。在设计模块时,可能会对测试策略、内置自检(BIST)与外部访问之间的平衡、睡眠模式以及如何部署电源或时钟门控做出特定的假设。

这些选择必须在整个设计过程中协调一致,以便生产出测试时间最短、全芯片电源管理策略有效的SoC。做出这些选择可能需要设计人员深入到IP模块的内部。

寻找合作伙伴

我们已经谈到了需要有效的设计合作伙伴具备深厚的IP专业知识的几个问题。对于当今SoC设计而言,理想的合作伙伴应拥有丰富的内部IP产品组合和广泛的第三方供应商网络。

它应拥有支持这两个来源的独立工程团队。它还应拥有灵活的参与模式,根据客户的资源和专业知识,在客户和合作伙伴团队之间逐块分配任务。

IP在SoC设计中的主导地位改变了设计任务的性质,也改变了客户对设计合作伙伴的期望。

(原文刊登于EE Times姊妹网站EDN,参考链接:System-on-chip (SoC) design is all about IP management,由Franklin Zhao编译。)

本文为《电子工程专辑》2024年9月刊杂志文章,版权所有,禁止转载。免费杂志订阅申请点击这里。