生成式AI时代,几乎与芯片算力达到相同热度的话题显然是连接。因为当模型变得越来越大、MoE与多模态大模型成为主流时,大量处理器、加速器、存储器需要一起工作,跨芯片、跨系统、跨节点变得常见。那么它们之间的互联效率,自然就是关键中的关键——重要性完全不亚于AI芯片本身。

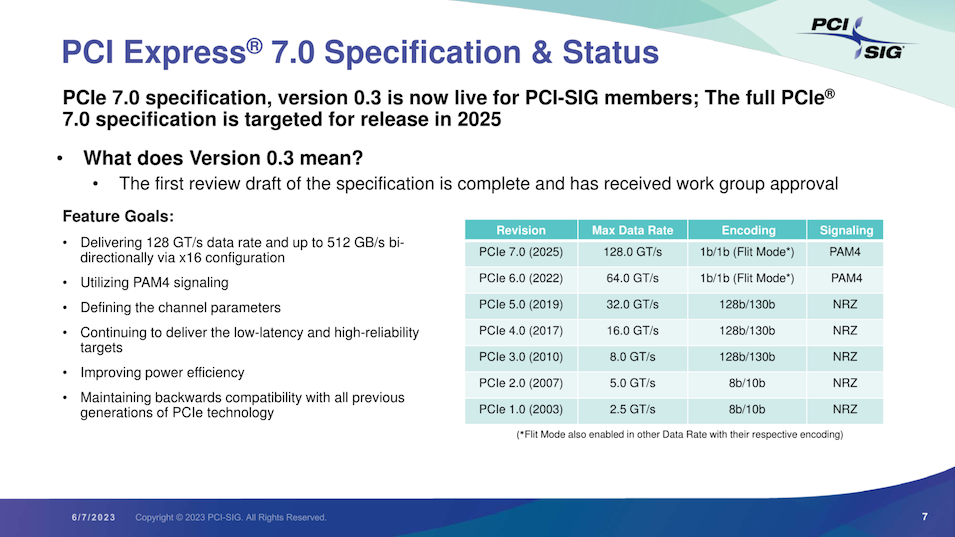

今年4月份,PCIe 7.0标准就也已经走到了Draft 0.5版。按照标准组织PCI-SIG往常的传统,Draft 0.5也就是标准的首个草案,后续还会有Draft 0.7、0.9,及1.0最终发行版。

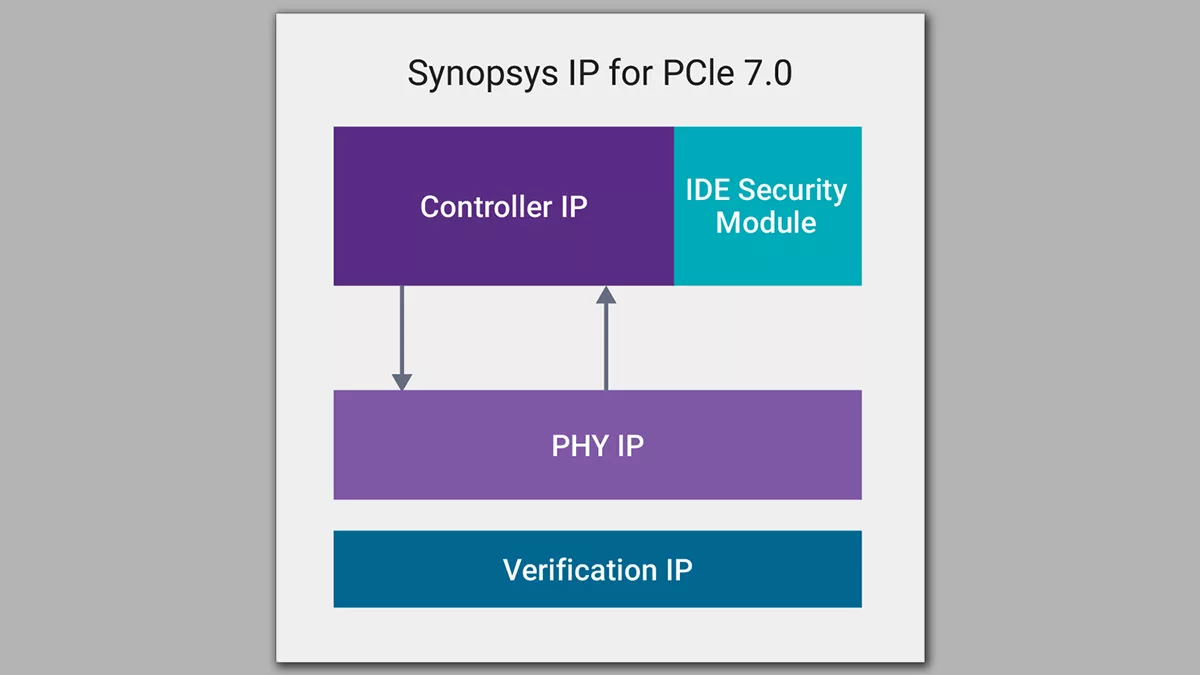

即便PCIe 7.0标准的最终敲定要等到2025年,PCIe生态内的参与者却都已经跃跃欲试了。比如新思科技6月份就宣布发布业界首个完整的PCIe 7.0 IP解决方案,涵盖控制器(Controller)、IDE(Integrity and Data Encryption)安全模块、PHY和验证IP;而且在6月中的PCI-SIG开发者大会上,还展示了据说是全球首个光信号传输PCIe 7.0 demo,步调不可谓不快。

借着这个机会,我们来提前展望一下PCIe 7.0未来能做到何种程度,对AI技术的发展又会有怎样的帮助。

PCIe 7.0带宽翻倍,对生成式AI很重要

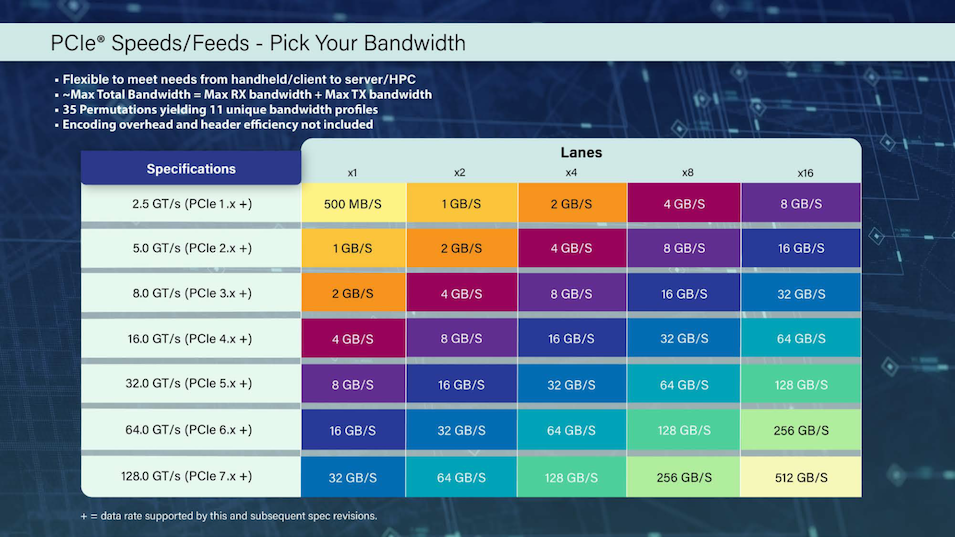

按照传统,这次PCIe 7.0标准打算再度将带宽翻番——单条lane可达成大约16GB/s的吞吐,且为全双工两个方向都可达到。那么很自然的,x16以后一个方向的最高吞吐大约在256GB/s的水平上——算双向带宽的话,可计为512GB/s。自PCIe 1.0到7.0的规格变化是这样的:

去年6月PCIe 7.0的0.3版——也就是首个草案问世,表明新一代的PCIe通信标准核心技术支撑确立,尤其是物理层总线频率加倍、明确PAM4调制。和上代标准一样,PCIe 7.0采用1b/1b FLIT(flow control unit)编码,FEC(forward error correction)技术,逻辑层开发应该会相对省事一些。

不过物理层30GHz频率,再加PAM4,相比PCIe 6.0实施更是困难模式,尤其在信号完整性的问题上——以往不少讨论文章都认为PCIe 7.0标准下要确保信号的完整性会是个比较大的挑战。另外PCI-SIG此前还强调PCIe 7.0会专注于加强通道参数,改善信号损耗问题,实现更出色的能效表现。

预计在不久之后的Draft 0.7版,即完整草案中,我们会看到更全面定义的PCIe 7.0。可能更多人关心的还是新标准的速率达成水平。

PCIe 7.0每pin达到128GT/s的数据传输速率,实现了相比于PCIe 6.0的翻倍,以及相较5.0的4倍。最终每个方向256GB/s带宽,目标市场明确为AI数据中心、HPC高性能计算应用显得顺理成章。

前不久我们参加德科技技术日,是德科技在谈到潜在市场驱动力时,将生成式AI列为其中关键。对是德科技而言,有关AI更确切的市场机会就在“高速数字电路”方向,PCIe是其中的核心组成部分。

当GPT-4达成万亿参数量,要移动海量数据集的时候,稳定、高带宽的互联显然是关键问题。因为一旦数据传输成为瓶颈,芯片算力再高也就显得没有意义。明确一下需求也就是:在确保一定能效表现的情况下,系统必须实时处理PB级别的数据量。

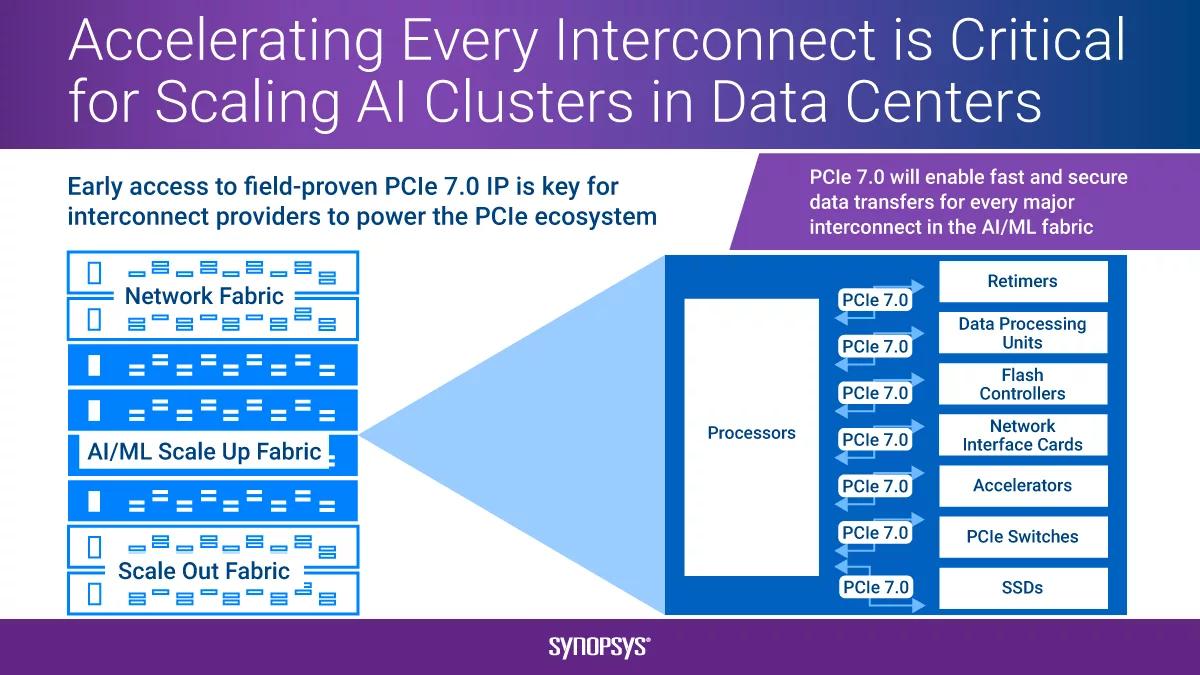

还有个关键点是,随着AI模型的日益复杂化,用于训练模型的数据中心基础设施也在发生变化。新思科技认为,当代AI负载要求多加速器配合中央处理器共通完成。“某些先进架构,在一个计算单位里,需要至多1024个加速器连接。”比如下面这张图中出现的DPU、NIC及各类加速器。加上闪存控制器、SSD、retimer(重定时器)等构成了完整的PCIe生态系统。

PCIe 7.0就是连接这些加速器,提供带宽和load-store结构需求的技术;对于AI而言也就意味着能够相对高效地、各部分协同地处理大型、复杂的机器学习模型。值得一提的是当互联需要在更大范围内、乃至跨节点进行时,NIC作为介质发挥作用,PCIe 7.0很自然地为处理器提供所需的以太网带宽。

完整的IP解决方案已经有了

前沿市场参与者普遍不想错过生成式AI发展的顺风车,所以各部分基础设施似乎都正以远快于过往标准与技术发展的速度推进,PCIe 7.0自然不例外。新思科技上个月就宣布推出业界首个完整PCIe 7.0的IP解决方案,其中包括有控制器、配合PCIe 7.0加强数据安全特性的IDE安全模块、PHY和验证IP。

新思科技在当时的新闻稿中提到,这套解决方案是在支持广泛的生态系统互操作性(interoperability)的基础上,面向AI负载,满足其传输大量数据的带宽和延迟需求;而且到目前为止,这也是行业内唯一的在x16 lane配置下,达成最高512GB/s双向速率安全数据传输的PCIe解决方案。

据说新方案的互联能效相比上个版本,提升了50%——而且是在确保数据完整性的基础上,以相同的芯片面积做到双倍的互联带宽。

具体来看,PCIe 7.0控制器IP是以完整的端点到根设备(root-complex)解决方案,实现低延迟、高带宽的连接;PCIe 7.0 PHY IP,则在达成PCIe 7.0最高速率要求的前提下,解决信号完整性问题——也是前文提到技术上的实践难点,并且和新思科技的CXL控制器IP解决方案进行融合;

其中的IDE安全IP则着眼于提供机密性、完整性,和针对硬件攻击的重发保护(replay protection)——IDE协议是PCIe 7.0支持的高级数据安全特性,尤其针对TLP(transaction layer packets)和FLIT做出数据安全支持;当然,全套解决方案还涵盖了验证IP和硬件辅助的验证解决方案,提供内嵌协议检查以及控制器和PHY的各种配置以加速验证和确认流程。

这套完整解决方案预计会在明年正式面向大众发布,新思科技表示其中针对PCIe 7.0的验证IP已经问世。搭配新思科技在HPC领域内的更多IP,如1.6T/800G Ethernet、CXL和HBM,以及SoC验证套件在内的常规工具,可预见PCIe 7.0用于HPC的生态成型会是个很快的过程。

前期参与方案与生态合作的企业已经不少,比如可与这套PCIe 7.0 IP搭配的来自Kandou的PCIe retimer,XConn的PCIe/CXL switch(交换器),还有更多系统解决方案、下游PCIe产品等。

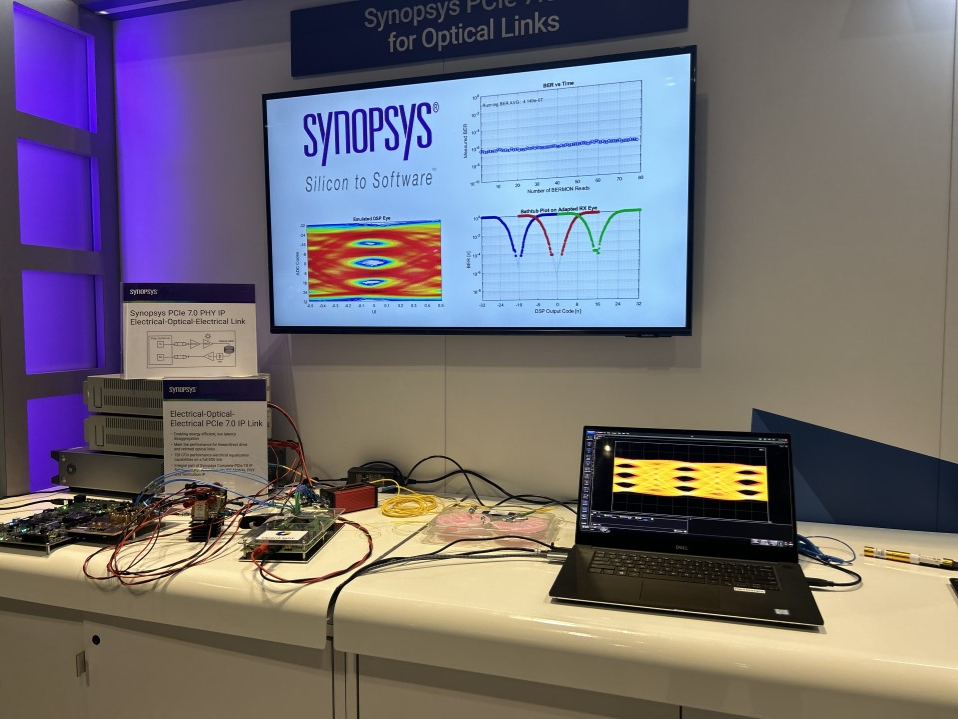

今年PCI-SIG开发者大会上,Synopsy展示了互操作性测试,将面板、线缆及不同IP结合的性能测试;现场展示互操作性的合作伙伴还包括是德科技、Samtec,Teledyne LeCroy等。

多走一步,用光连接的PCIe 7.0

同在这场大会上,新思科技展位上有个更具未来向的demo展示:全球首个电-光-电(E-O-E)PCIe 7.0 IP连接,将前述新思科技的PCIe 7.0 PHY IP与OpenLight的光芯片(Photonic IC)结合;也就是借助光通信或者叫光信号传输、通过线性驱动方法(linear drive)达到PCIe 7.0数据速率的演示。

依托光信号传输的PCIe实现,应该也是现在技术走向的大热门。甚至不单是PCIe,年初的英伟达GTC开发者大会上,行业中的公司就谈到借助铜介质的电传输发展快要走向瓶颈——无论是性能还是效率上,所以他们正研究芯片之间通过光信号来传输的波分复用技术。即便对应的技术短期内仍然不会大规模商用,但生成式AI时代,数据中心走向光连接几乎是板上钉钉的。

去年8月,PCI-SIG也特别组建了Optical Workgroup光学工作组,专注于光信号传输PCIe标准相关工作。包括新思科技在内的诸多行业巨头普遍认为,PCIe over Optics会是满足数据中心日益提升带宽需求的解决方案。前不久新思科技也在blog文章中细数了光信号传输的几大优势:

(1)相比于电传输更高的带宽密度,这一点无需赘言;(2)能够覆盖更长的传输距离,价值在于处理器或加速器数据访问可不局限于本地存储资源。因为当允许更远的传输距离时,算力单元也就能访问更远的存储单元,甚至跨服务器或机架,也就能够实现更理想的资源池化,或者更好地支持CXL之类的技术;

(3)更优的能效和成本效益。具体表现为相比于电连接,明显更低的损耗——换句话说相同传输距离下,所需的retimer和SCU(信号调理单元)更少;此外,光组件的设计制造进入成熟阶段之后,成本也会变得更加可控;加上光纤所占空间明显小于铜缆,也有机会提升数据中心的整体密度,实现系统成本的降低;还有线性驱动(linear/direct drive)光连接能够降低延迟和功耗。

现阶段阻碍PCIe完全转向光通信的因素可能还有不少,毕竟现有PCIe生态整体都构建于电信号传输这一基础之上。所以首先要考虑的是与电系统的兼容性问题,确保互操作性——新思科技与OpenLight的演示中就对应提供了可与光IP协作的电IP解决方案;其次是PCIe协议对于光传输技术的适配,比如Rx接收端检测、Electical Idle状态管理、旁带信号处理等。

或许PCI-SIG光学工作组的建立会逐步解决这些问题,新思科技也表示会积极参与构建“optical-friendly”的PCIe标准。

PCIe 7.0技术与产品普及大概还需要等一等。不过生态内的基础设施构建,典型如新思科技的PCIe 7.0完整IP解决方案准备就绪,以及PCIe 7.0标准很快也要走向终版;再加上此刻时代面临新的技术奇点:生成式AI,令PCIe相较以往承担着更重要的责任。PCIe 7.0或许会在AI HPC市场上得到快于过往的扩散和支持。