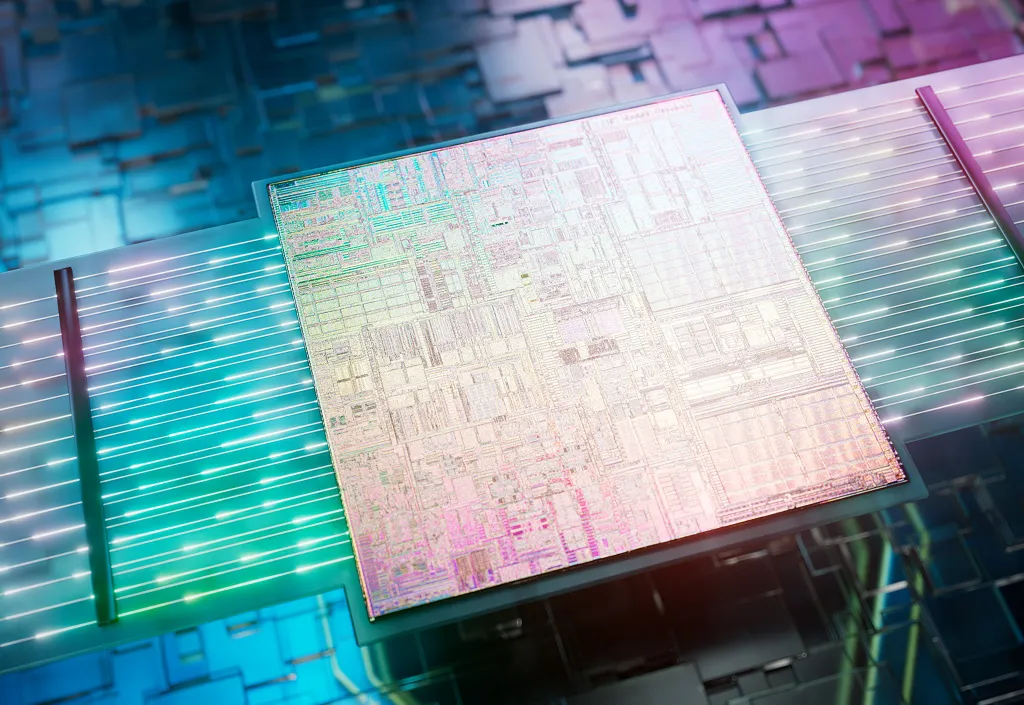

今年3月份的OFC(光纤通信大会)上,Intel展示了传说中的OCI(光计算互联)chiplet——这枚硅光芯片die和另一片CPU die封装在了一起,构成一个系统;演示的主要是两颗CPU借助光纤进行通信。

在此过程中,OCI chiplet将CPU的电信号转为光信号。Intel在博客文章中提到,基于Intel硅光子技术(Silicon Photonics technology)完全集成的OCI chiplet,达成4Tbps双向传输速率,在数十米距离内单向支持64个32Gbps数据通道,上层协议兼容PCIe Gen 5。

虽说这一技术尚未进入量产,但这则演示显然是给出了硅光集成技术未来发展的可能性的。而且不单是Intel,近半年开始探讨光通信技术的企业至少还包括了英伟达、Synopsys等上下游市场参与者。

他们探讨光通信的背景都在于生成式AI技术的发展:巨量参数规模的大模型训练和推理,都面临越来越严峻的存储和通信墙(或者叫IO墙)问题。因为生成式AI大模型计算,往往涉及到跨芯片、跨板卡,乃至跨节点的大规模集群,此时芯片和系统之间的通信就变得尤为紧要。

在最近的媒体采访中,宋继强(英特尔研究院副总裁、英特尔中国研究院院长)提到,数据中心“以前是读一次(数据),做几十、上百次计算”,到了AI大模型时代“存算比”甚至可能到1:1的程度,“对带宽要求很高”。

传统借助铜线的电信号I/O传输遭遇瓶颈始终是这两年的热议话题——尤其传输距离受限和带宽密度问题。今年GTC大会上,英伟达首席科学家Bill Dally还说长距离连接领域的电气信号传输方式快要发展到头了。

所以很自然的,光信号传输有了一席之地——尤其半导体行业内的从业者普遍认为随技术发展,硅光的系统成本,最终都能够比肩传统电气传输方案。本文尝试借助Intel的硅光技术研究,及最新的OCI chiplet原型演示,来谈谈当代硅光技术的发展现状。

硅光芯片做到了何种程度?

先谈谈OFC大会上Intel的这则demo。整片OCI光计算互联die,与CPU die封装在一起——两片die的具体封装方式Intel没有详述。

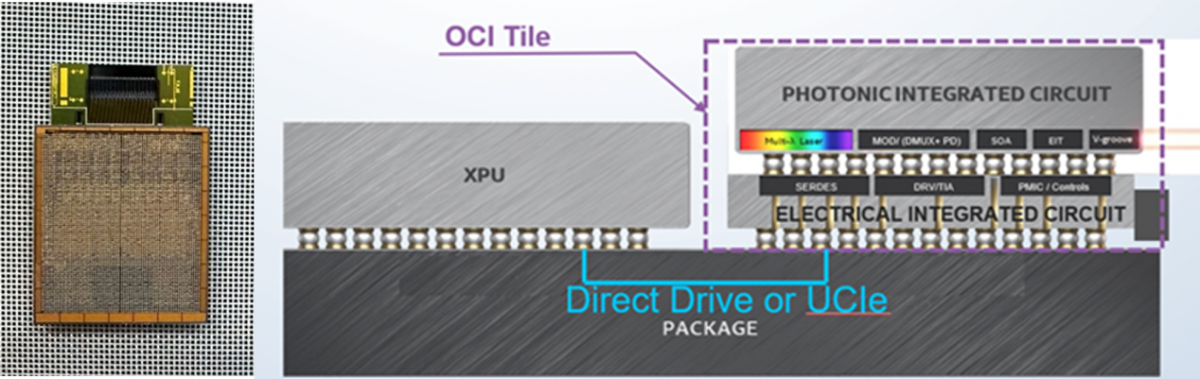

仔细看右边的这一片OCI die,其上包含有PIC(硅光子集成电路)——里面是完整的光学子系统,关键组成部分有片上激光器(laser)、光放大器(optical amplifiers,SOA)等;另外还有EIC(electrical IC,电气集成电路),“安装在带有集成微控制器、调制器驱动器和跨阻抗放大器的基板/封装上”。

从示意图来看,PIC与EIC这两片die是垂直堆叠在一起的;另外其上似乎还有个能够组合可分拆光连接器(detachable/re-usable optical connector)的路径。这样一片“光电共封”的chiplet,和CPU再封装到一起,满足高带宽、低功耗的要求。面向最终目标应用时,这里的CPU应当也可以换成其他包括GPU、IPU等在内的加速器。

“PIC(硅光子集成电路)更多在于解决光这部分的问题,进行信号调制、把信号发出去、稳定传输等;而EIC(电子集成电路)的功能更接近于具体的信号怎么使用,如何与CPU、GPU或者其他SoC对接。”宋继强谈到,“EIC很大程度上成为(上层)协议的转换适配层;PIC则是完成电介质和光介质之间的转换。”

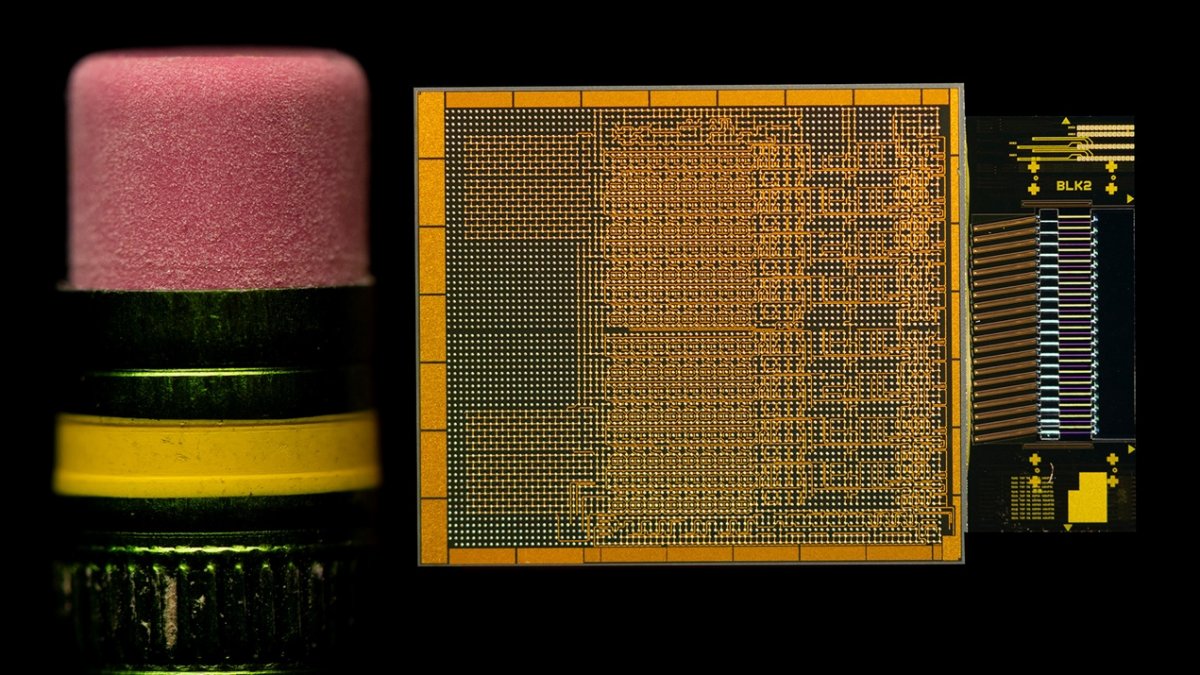

OCI chiplet的具体尺寸未知。不过Intel自己公布了OCI chiplet与标准2号铅笔末端橡皮擦的对比图,如下图。

如前所述,这一代OCI chiplet实现的双向数据传输速率为4Tbps,单向以64个32Gbps通道进行传输;物理层的具体实现方式是8个光纤对,每对承载8个DWDM(波分复用)的不同波长(每个波段频率间隔200GHz,总共占用1.6THz光谱),功耗5 pJ/bit——据说仅为传统可插拔光收发器模块(pluggable optical transceiver module)的1/3。

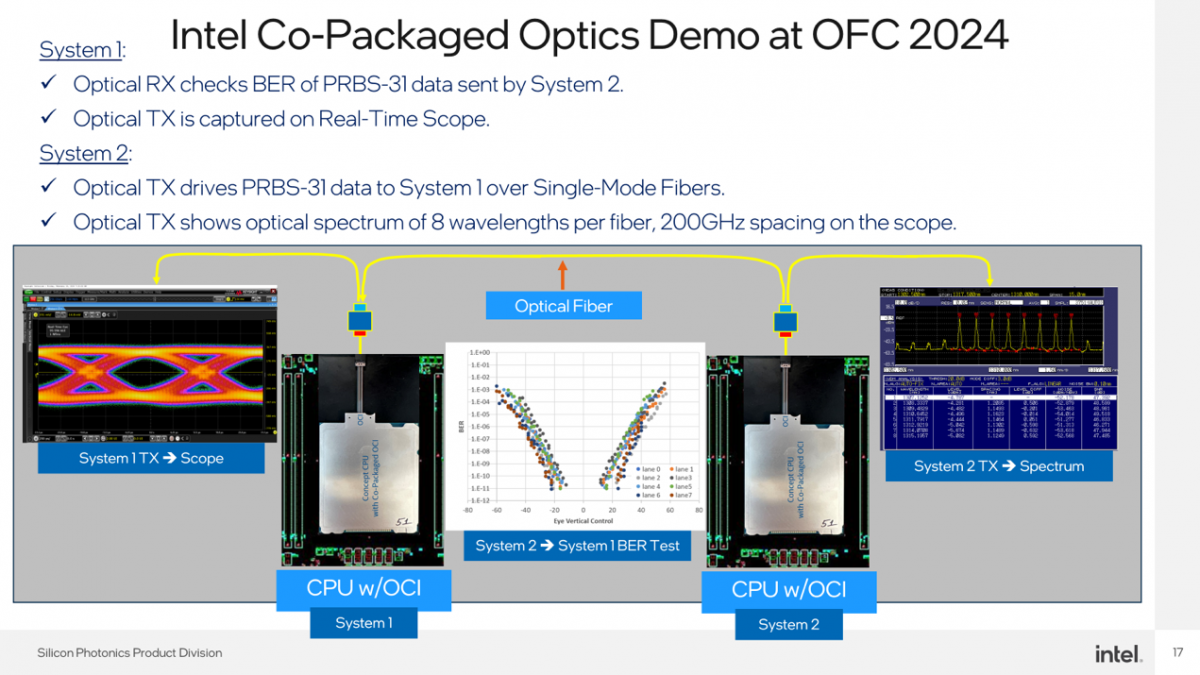

整个演示是借助OCI连接两颗CPU,简单拓扑及BER比特错误率等测试结果如下图:

两个CPU平台通过SMF(single-mode fiber)单模光纤连接,CPU生成并测量BER;Tx光谱8波长200MHz间隔;32Gbps Tx眼图展示比较出色的信号质量;

这套演示方案的亮点,除了实践了芯片间光通信,还在于激光发生器、光放大器做到了硅晶圆上,或者说光学子系统是基于半导体生产流程去制造的。

尤其考虑到“高集成度的激光器,用普通光纤传输信号就行”,“现在所有的外部激光器方案还需要专门的光纤——保持偏振光特性不变的光纤(Polarization Maintaining Fiber),不仅成本高,而且没有规模化部署的案例”。

“对于大规模集成电路而言,将非硅器件或其他电路形式进行大规模的基于硅片的集成,也是Intel能够做到的。”宋继强提到,本次展示的OCI chiplet,“将激光器和光放大器全部集成到一个晶圆上是我们的优势。这让(光学系统的)体积变得更小,功耗也更低。未来走向规模化,良率提升、成本也会下降。”

早在2020年Intel Labs Day的新闻稿中,Intel就提到集成光子原型产品,实现了“光子与CMOS技术的紧耦合,为未来计算芯片与光学子系统完全整合提供了PoC概念验证”。当时宣传的主体还是微型环状调制器(modulator)比传统方案小1000倍,“消除将硅光集成到计算封装内的关键阻碍”。

今年OFC大会上的演示显然是对这一理念的延续。

硅光集成技术的关键

尝试更近距离观察其中的光学子系统,更便于我们理解OCI和光信号传输的工作方式。当代光信号传输,更多考虑到原有电子工程与计算机科学的历史兼容性,系统的主体部分仍然是基于电的。

而光学子系统的主要工作是将计算得到的电信号转为光信号、再传出去,或者检测、接收到光信号以后再转回电信号。下面这张图展示了一对光纤传输不同波长的光信号,这是一种典型的波分复用方案。“在每个波段上,稳定地调制出要传输的信号,再通过光纤传输。”

这套系统内主要包含有激光发生器、接收器(receivers)、光波导(waveguides)、调制器(modulator)、复用/解复用器(mux/demuxer),以及其他相关集成电路和被动器件。

宋继强在答记者问时谈到了光学子系统采用半导体制造技术的难点。首先是激光器的晶圆级制造,“通常激光发生器基于III-V族化合物,比如常用磷化铟(InP)来制作半导体发光器件——用于做分立器件还是相对简单,要和硅基结合就有难度”,“需要将磷化铟晶圆与硅基晶圆键和在一起”。

“将不同种类的半导体进行晶圆层面的键和,然后再通过半导体制造工艺去打造控制电路,最终才实现了集成到晶圆上的激光器。”

“其次是如何用硅来放大、检测激光”,反映到Intel的解决方案上的关键是SOA光放大器。“以前市面上也有大的分立器件,通过板级集成。”宋继强谈到,“我们也在晶圆级制造过程中成功地实现了集成。”

配合其他器件,包括“直接在晶圆上刻出来”用于导光的光波导、环状的信号调制解调器——尺寸也非常小...加上其他组成部分,“总之,诸多器件都需要在半导体晶圆上做出来”。最后这样的PIC与EIC进行集成封装。

我们对光学子系统的制造工艺了解不多,宋继强在采访中提到通常PIC所用制造工艺会比EIC更为成熟,“EIC需要与CPU/GPU等主芯片接近和对齐”;当然“PIC也追求小型化”,但“首先需要保证足够的效率,因为光相关的器件需要一定的尺寸才能达到最好的效果”。

据说在硅光子工艺节点方面,Intel最新一代技术能够提升器件性能,达成更高的密度、更好的耦合和经济性;预计能够实现die尺寸40%的缩减和功耗15%的降低。若有机会,未来我们会针对这部分技术做更进一步的深入探讨。

Intel在PPT上总结目前硅光子技术进展,体现出Intel的优势包括:激光器和光放大器的集成,相较于外部光学系统方案在成本、功耗、噪声和可靠性方面都有优势——Intel提供的数据是,激光器的FIT(时基故障率)< 0.1;

其次是能够体现Intel的先进封装与工艺技术能力;而且据说其Silicon Photonics硅光集成平台已经准备好上量了;最后是Intel作为系统级代工厂(system foundry)技术能力的体现。

另外值得一提的是,Intel对于OCI硅光集成技术的目标应用场景在百米以内的系统间互联;超过100米时,光信号通信方式仍应考虑可插拔光收发器——因为其功率更大、系统可容纳的尺寸也更大。

未来走向和应用:可能很近了?

有关OCI光计算互联技术的产品化信息还无从得知,不过其上的PIC实际已经在可插拔光收发器模块上应用,并且部署到了大型数据中心网络,面向100, 200和400Gbps应用。Intel表示下一代支持800Gbps和1.6Tbps应用的200G/lane的PIC也在开发中。

到目前为止,已经有超过800万PIC出货(超过3200个集成的片上激光器),前文提到FIT小于0.1的数字应当是基于这一先行商用场景。

回到更小尺度的OCI chiplet,虽说这次的demo是“数十米”距离单向64个32Gbps通道传输,以及5 pJ/bit的能效。实际今年3月份Intel发布的博客文章提到,其首个解决方案是要实现PCIe Gen 6的4倍密度提升,<3.5 pJ/bit的能效,以及<10ns(+TOF)的时延,并且传输距离超过百米。

Intel对于在近未来实现这一目标似乎也很有信心,主要得益于英特尔研究院(Intel Labs)此前在硅光子领域研究了长达25年,以及Intel在半导体制造方面长久以来的经验。Intel的硅光集成未来路线图是这样的:

基于波分复用技术切分的波段数量,Intel的计划是临近2030年要走向16λ,单个波段则可再行扩展至64Gbps,得到16Tbps的速率;未来也会有进一步演进的余地。

我们说今年是硅光和光信号传输技术发展格外亮眼的一年,一方面在于很多头部企业都开始更积极地谈论光信号传输;另外上层标准也正伺机而动,去年8月,PCI-SIG特别组建了Optical Workgroup光学工作组,专注于光信号传输PCIe标准相关工作。

在今年6月份的PCI-SIG开发者大会上,Synopsys和Cadence都演示了PCIe 7.0光信号传输demo——不论是否达到了光电共封装、乃至异构集成硅光芯片的层面,PCIe over Optics都似乎已经是板上钉钉的未来了。

除了本文已经谈论过的光信号传输具备更高的带宽密度、覆盖更长的传输距离、更优的能效表现,以及大规模量产以后系统层面具备更好的成本效益,它对生成式AI时代下的智算中心也可能算得上是必选项。

不仅是效率比电信号传输更好:当传输距离更远时,算力单元能够更高效地访问更远的存储单元,甚至跨服务器或机架,也就有机会实现更理想的资源池化方案,这显然是CXL一类技术扩展实现的关键。

回到芯片和晶圆层面的硅光集成:率先布局相关技术,拿出经验证的OCI解决方案,并逐渐从封装和平台集成中获得关键经验,是Intel未来大批量应用OCI chiplet技术,乃至可能在AI基础设施领域占得先机的关键。

据说Intel已经在和部分客户探讨在SoC共封装OCI光通信解决方案方面的可行性。虽然我们不清楚该技术的商业化进展,但其原型产品的技术迭代及Intel的成果展示,都令这项技术看起来相当有发展潜力。