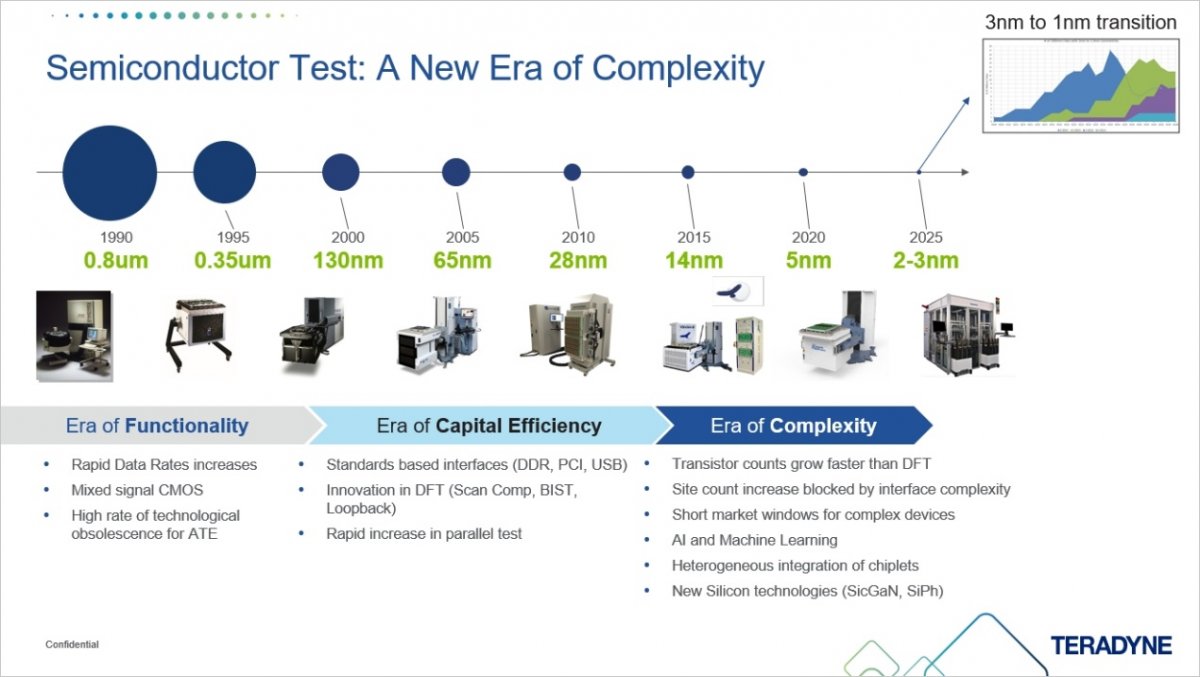

伴随着半导体芯片技术的发展和复杂度的不断提高,芯片测试的挑战也在不断提高。半导体制程从90年代的0.8μm到现在的3nm、2nm,未来向1nm制程的演进也带来更多的挑战,而不同的芯片设计,例如用CMOS制程制造出数字或“数字+混合信号+RF”,因为不同制程可能针对不同芯片的设计技术,未必会达到同样的良率。

芯片设计和制造复杂度的提高,对测试端提出了更高的要求。泰瑞达致力于为从设计开始的测试、芯片测试以及成品测试提供解决方案,聚焦量产测试方案的服务。

本文将探讨芯片测试业在成本、车规芯片和大数据等领域的最新发展。

有效管理重资本投入,降低芯片测试成本

测试产业是一个重资本投资的产业,怎样在重资本投资方面有好的回报?

泰瑞达亚太区销售副总裁Richard Hsieh 2000年加入泰瑞达,曾在泰瑞达子公司LitePoint担任全球销售副总裁,聚焦整个电子产业供应链20多年。

“泰瑞达从1990年到现在都推出了不同的机台。令人惊喜的是,有一些客户现在还在使用我们90年代推出的机台,如1995年推出的J750。厂家在做资本采购时,都会算固定折旧,折旧完毕后在资产上的直接成本就没有了,大部分都是间接成本。所以整个机台的设计怎样让它能够测得更多,让它的利用率更高,具备更高的资本效率,这是一个挑战,而且能够维持很长的产品生命周期也很重要。”Richard Hsieh分享到。

图:半导体测试复杂度不断提升

当芯片规模越来越大时,如AI芯片,又怎么降低测试成本?多挑战并存。

增加同测数是一个必选项,而增加同测数的同时,接口的设计就会变得更复杂。如何在复杂情况下让产品顺利推出,赢得比竞争对手更快的时间,把产品推出市场,获得前期的利润,这是一个挑战。涉及到高阶制程,会有很多测试数据,这些测试数据怎么去分析、去应用,帮助提升芯片的设计和量产良率,这也是一个挑战。异构集成,是将不同的芯片集成在一起,包括先进封装方式或chiplet方案,怎么结合在一起,这也是另外一个挑战。

当然,有很多新的材料技术,包括Sic、GaN和SiPh,都处在新的研发阶段。所以整个半导体产业,现在和未来都会蓬勃发展。半导体制程技术步入14nm、7nm、5nm,甚至3至1nm,在每个节点都有很多的应用,成熟制程或新的制程会让整个芯片产业发展更好,创造出更多的机会。

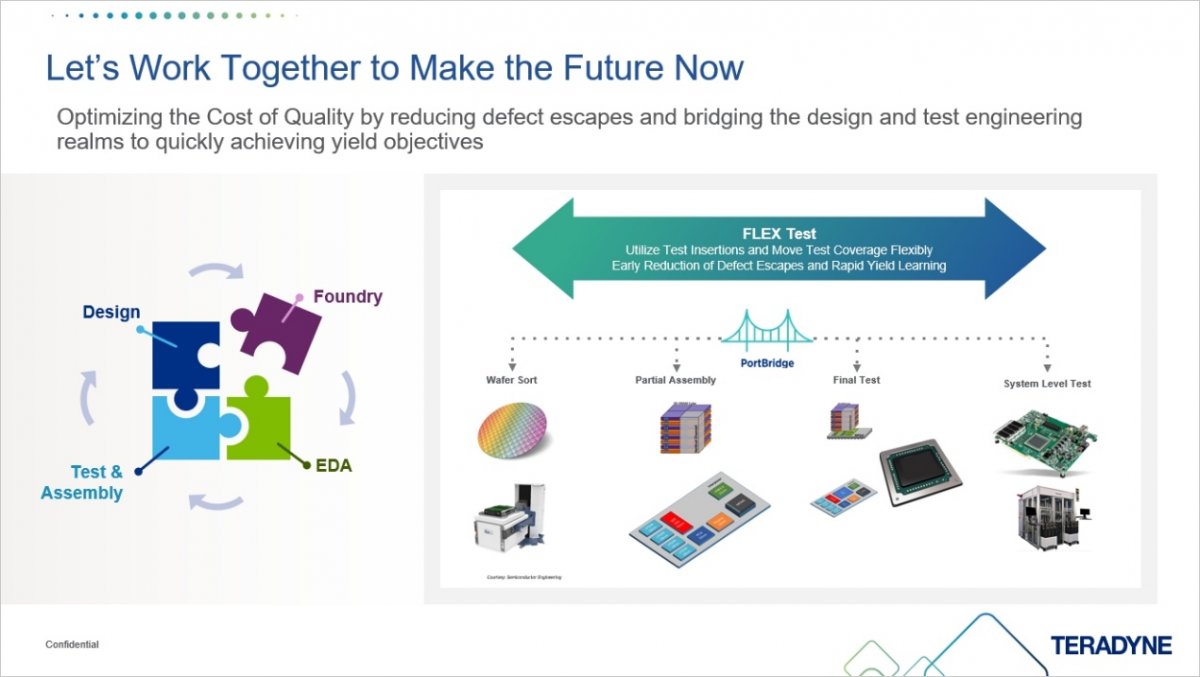

“芯片越来越复杂,怎样去缩短上市时间?如何从芯片设计开始就让芯片测试参与其中,直至系统端的测试?因为有一些高阶制程,ATE是没法覆盖的,或者成本太高,需要到最终端的系统端测试,我们称之为System Level Test(SLT)。为应对这些挑战,泰瑞达提供一个软件工具PortBridge,可以连接EDA工具和ATE测试机,设计人员通过PortBridge收集测试数据,将分析结果反馈给Fab,从早期阶段介入帮助Fab厂商提高良率。

图:PortBridge软件工具

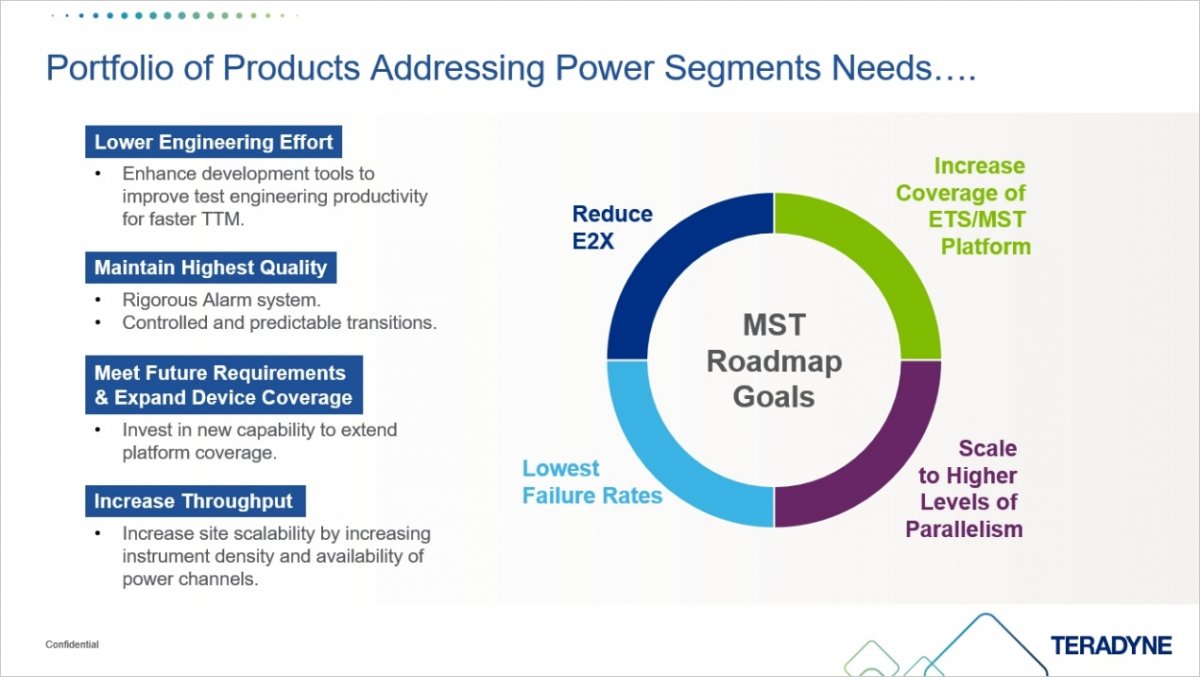

为功率器件检测提供一体化方案

在新能源汽车领域,中国处于领先的市场。新能源汽车会带动中国车用半导体快速的发展,尤其会造成全球车用半导体产业的供应链市场份额的变化。

“车用半导体或在太阳能、风电、ESG等领域,功率芯片来越重要,产品也越来越丰富。怎样在产品越来越多的情况下,能够缩短上市的时间,能够兼顾质量?一些PMIC芯片非常高的精度要求,尤其新能源汽车在安全方面不能出差错。测试覆盖率也很重要,而在量产方面最重要的还是怎样增加吞吐量。泰瑞达非常重视吞吐量,不是只有单位小时内所能够测试出来的产出,还包括在单位面积中能够创造出多少的产出,因为设施的成本越来越高,间接成本也越来越高。”Richard Hsieh表示,“另外,还有不同区域产能的转换。怎样去做产能的移动和转换,能够兼顾到单位产出的成长,能够把整个生产成本降低,这都是很大的挑战。我们都有很好的方案予以支持,这也是泰瑞达一直追求的目标所在。”

图:泰瑞达针对功率器件的测试策略

完整的测试机台

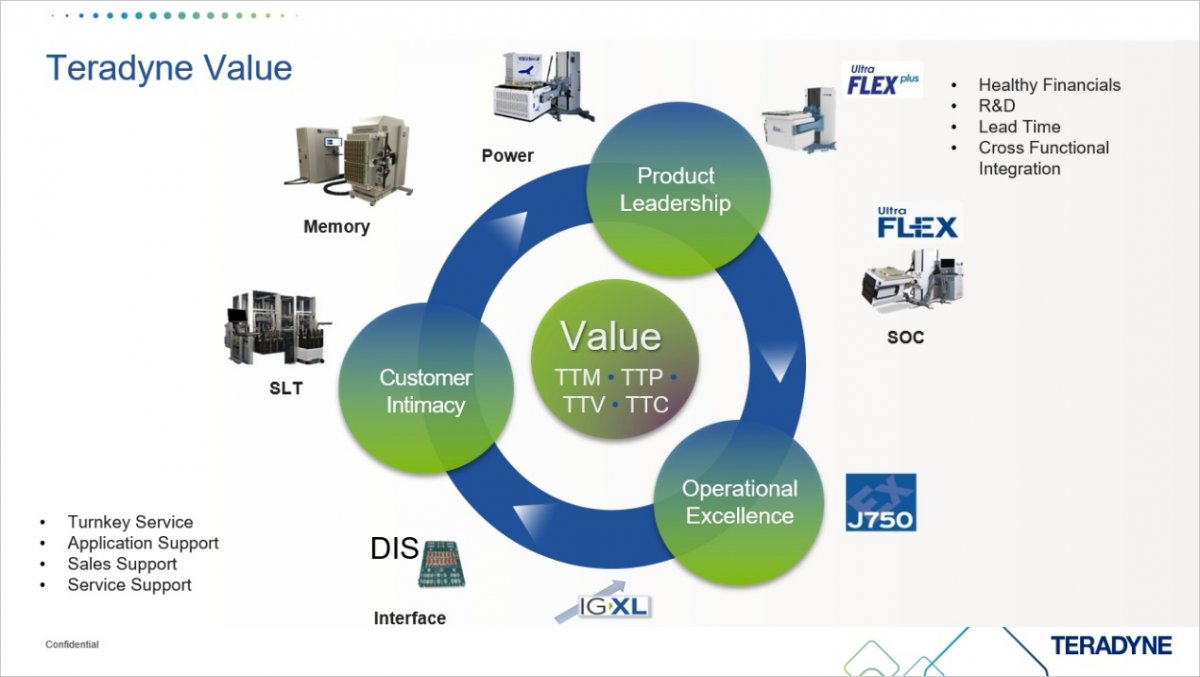

下图给出了泰瑞达目前所有的机台,包括Power类芯片测试平台ETS系列,混合信号测试平台J750, UltraFLEXplus系列,存储器测试平台Magnum,再到系统级测试机台。

图:泰瑞达测试机台系列

针对泰瑞达能够提供的价值,Richard Hsieh表示体现在4点:上市时间(Time to Market/TTM)、即时生产(Time-to-Production/TTP)、即时量产(Time-to-Volume/TTV)、以及即时回本(Time-to-cost/TTC)。

“过去60多年来,泰瑞达一直在片量产测试上做得很好,我们会持续往这个方向发展。无论是在产品还是在服务方面,都能够提供最好的解决方案给我们的客户。”Richard Hsieh总结到。

图:泰瑞达产品和价值观

先进节点下汽车芯片所面临的挑战与良策

众所周知,如今电动汽车市场如火如荼。无疑,在快速变革当中出现了针对电动汽车的诸多困难和挑战。

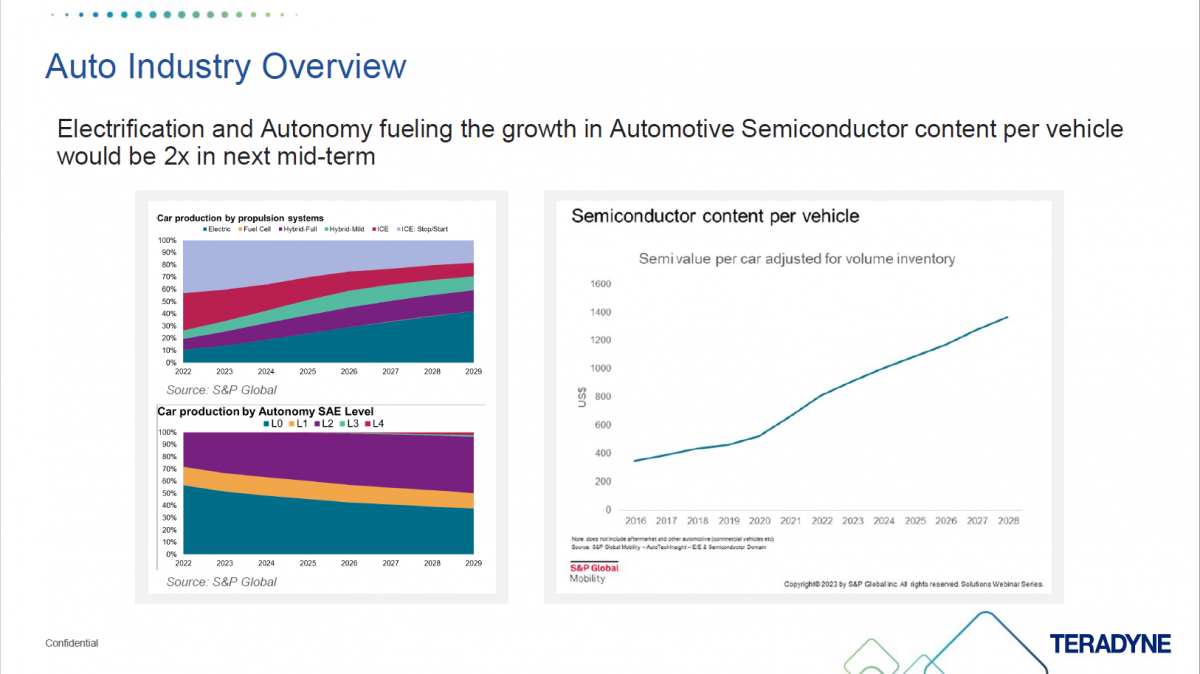

按照统计数据,电动汽车从2022年启动至2029年数量将不断增加,预估5年后其所占比重相对现在会实现翻番。就自动导航而论,L2层级占比也是逐年增加。这给汽车行业带来的最大变化就是在每一辆车中用到的半导体器件的数量也在翻倍增长:2023年大概在800—1000美元,后续5年可能会达到1500美元,同时,电动汽车与传统汽车相比半导体元器件的数量也在成倍增加。

图:汽车半导体需求持续增长

泰瑞达中国区总经理Felix Huang(黄飞鸿)曾在ATE行业不同的公司、不同的主流平台做技术支持,已耕耘20年。目前,他带领泰瑞达中国整个销售团队,负责在中国的技术服务和机台销售。

图:泰瑞达中国区总经理Felix Huang(黄飞鸿)

“几年前开始越来越多的车用芯片进入到车规时代。车规芯片追求零质量缺陷的目标,这个目标有专门的AECQ100、ISO16949等针对不同的环节的不同质量标准,芯片设计标准是AECQ100,ISO26262为安全功能要求,对于工厂要求则是ISO16949,目标是零质量缺陷。要完成这个零缺陷目标,任何一个环节都不能掉链子。”Felix Huang表示。

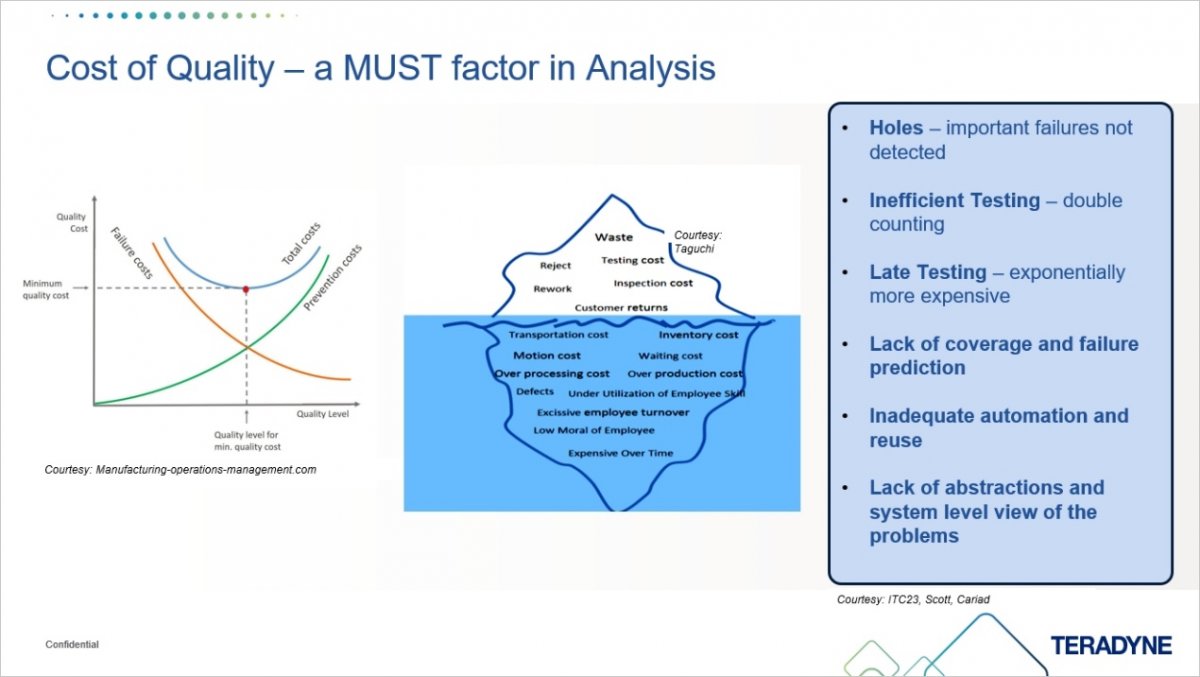

Felix Huang以下图分析了器件质量和成本的关系。“我们看红色这条线,质量等级越高,后面器件带来失效的成本就会降低。绿色这条线是为了追求高质量要做一些预防性的提前检测。为了追求高质量,额外也会带来很多的成本增加。蓝色这条曲线,类似‘浴盆曲线’,它的最低点即是达到最小质量成本前提下的甜蜜点(Honey point)。实际上每家都在看成本是多少,99%到99.99%会带来什么结果,所以不同的芯片虽然都用在车里,要求的标准和成本都是不一样的。”

图:器件质量和成本的关系

一辆汽车中的几大部件,如ADAS自动驾驶、智能驾舱、MCU控制、传感器等要求均不相同。例如,自动驾驶对质量要求一定会高很多,因为一但发生故障,就涉及到安全性问题。从另一个角度看,测试成本是显性成本,但是如果质量控制不好,隐性成本对社会的影响远远超过显性成本,包括库存成本、运输成本,甚至人员变动成本。

车规芯片追求零质量缺陷,即0 DPPM。

ADAS对于车厂和芯片的要求现在是10 DPPM,也就是说百万颗芯片中10颗缺陷。达到10 DPPM非常困难,需从前端到后端全链路覆盖,包含筛选、晶圆检测、封装检测、PCB板检测、芯片上系统板之后整个功能的检测等。

“要达到零质量缺陷,第一要考虑的是测试策略,第二是流程怎么做,最后需要什么样的工具来支撑。在策略性方面,在刚开始设计这颗芯片的时候,就要设定0 DPPM目标,规划从设计阶段到最终量产阶段每个环节是什么样的,怎样去保证。第二是流程,在实现这个流程的过程中,怎样多步骤协作、多人协作,怎样做到尽可能自动化,减少人为因素带来的问题。最后是需要可靠的工具,能够做实时性、可预测性、智能性的分析。因为从前到后,重要的事情说三遍,数据、数据、数据,从前到后背后流动的就是大数据,来支持达到0 DPPM目标。”Felix Huang表示。

图:车规芯片的测试要求

零质量缺陷测试的三个环节

Felix Huang详细阐述了三个测试阶段的细节和要求:

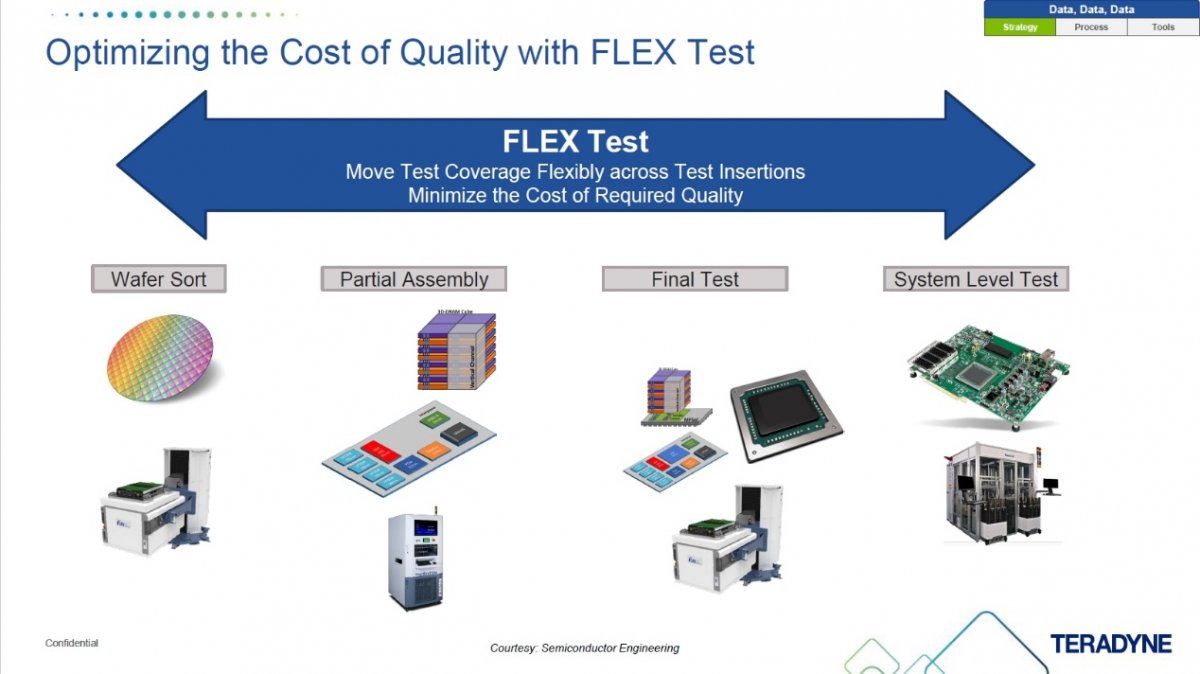

测试策略:首先,我们要通过一个比较灵活的测试流程来尽量优化质量成本。

Wafer Sort(晶圆测试)是在晶圆阶段通过测试机检测有没有坏的Die。第二个阶段会对PCB板装配进行检测。实际上,更平滑的流程应该是从晶圆测试到Final Test(成品测试)。对封装也会做检测,因为封装过程中也会带来一些芯片损伤。晶圆测试、成品测试完成后并不是结束,这两个阶段的测试项目不能做到100%覆盖,有很多场景的大规模运算是发生在系统级的,必须要把芯片安装到最终应用的系统板上,再做一个系统级测试。当然,每个阶段泰瑞达都有不同的机台覆盖这些方面的测试。

图:FLEX测试流程

什么是FLEX测试?上图有两个箭头,测试可以往左边移,也可以往右边移。如何移动?这里就要考虑成本了。芯片上的缺陷都希望尽早被发现,如果很多问题在晶圆测试阶段就能够检测出来,到了成品测试时就不需要再去检测,只要去看封装可能带来的Die与Die之间的互连带来的问题。一些可以在前面阶段解决的测试,就不要留到靠后的SLT,因为在一颗芯片售价中,其测试成本始终跟封装、工艺成本相比占比较小,发现问题越早越有利。从成本角度来说,能不能往前多移一点?当然从覆盖率的角度来看有些不能移,就只能在后面添加上去。这就要求一个机台本身要有非常好的稳定性、可重复性,也要求测试能力和覆盖率可以达到相应的要求,这样才可以实现一个FLEX测试。

“其实测试没有那么简单,不是通过和不通过的问题,需要在整个流程中不断分析数据,分析完数据后,才能知道哪些要前移。你必须考虑到底在哪个阶段测量什么样的测试项才能达到最优,这里没有一个固定的解答,一定是具体情况具体分析,不同公司不同的芯片,需要做不同的分析。零质量缺陷测试一定要从晶圆测试、成品测试和系统级测试三个方面来看。”Felix Huang介绍到。

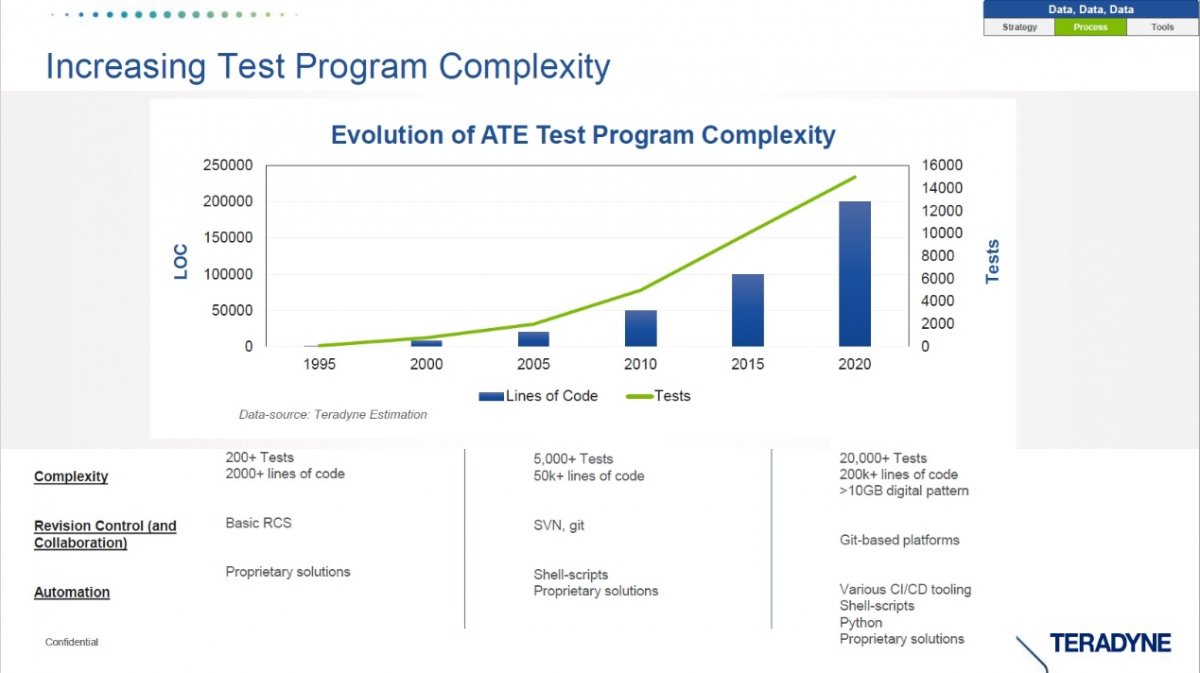

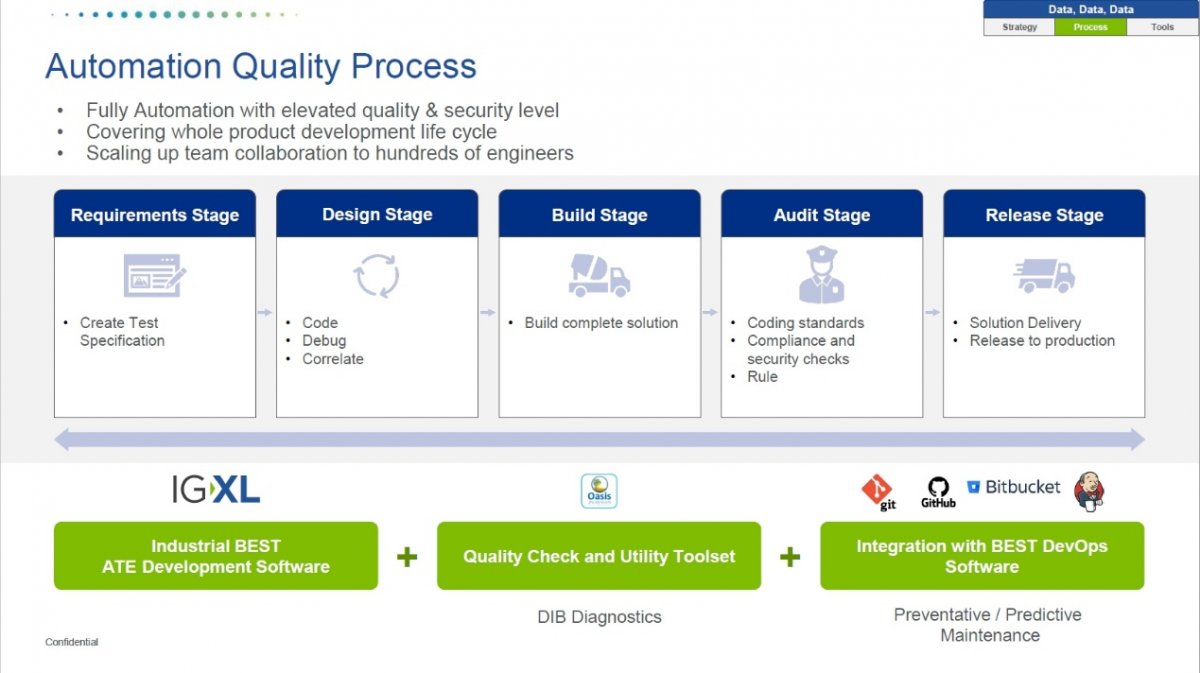

图:测试程序复杂度不断提高

过去几年测试程序的复杂度越来越高。从最早的测量一颗芯片约有200个测试项,代码量大概一两千行,发展到现在代码量达到几个到十几个Giga的水平。到2020年后,开发测试程序基本上都是一个团队,协同不同的地方的人协同开发,最后再整理调试,这就引发了对工具、自动化、智能化的要求。

图:ATE测试程序流程

按照Felix Huang的介绍,整个ATE测试程序的流程分成上图几个阶段。从左到右,开始时需与芯片设计工程师谈早期的测试需求、方案的设计。第二个阶段开始做设计,即测试程序的设计,包括代码、调试等。完成之后,每个工程师调的不同流程还要做一个整合,把它构建在一起,成为一个完整的解决方案。真正进入大规模量产之前还要对代码做标准化,去除冗余部分,然后做测试时间的优化。最终这个程序多快好省,质量达到要求,才能够发布生产。

“针对不同的机台,泰瑞达首先有不同的软件支持。IG-XL软件是ATE行业中有口皆碑的一个开发软件,我们整个测试程序开发都基于这个软件。”Felix Huang强调到,“基于IG-XL软件我们还有一个辅助工具Oasis。Oasis可以检测开发的代码质量。我们还有一个全流程管理工具DevOps,贯穿从开始到后面每个阶段要运行哪些东西、要在哪个阶段运行Oasis哪些插件,来保证某个阶段的质量,这是一个完全自动化的全流程管理软件。工程师开始开发一个测试程序的时候,从Offline阶段就会自动调用Oasis中的Offline检测工具,生成一个报告,将问题发到相关工程师的邮箱,直到把报告中的问题全部修复以后才会进入到下一个阶段。”

数据、数据、数据

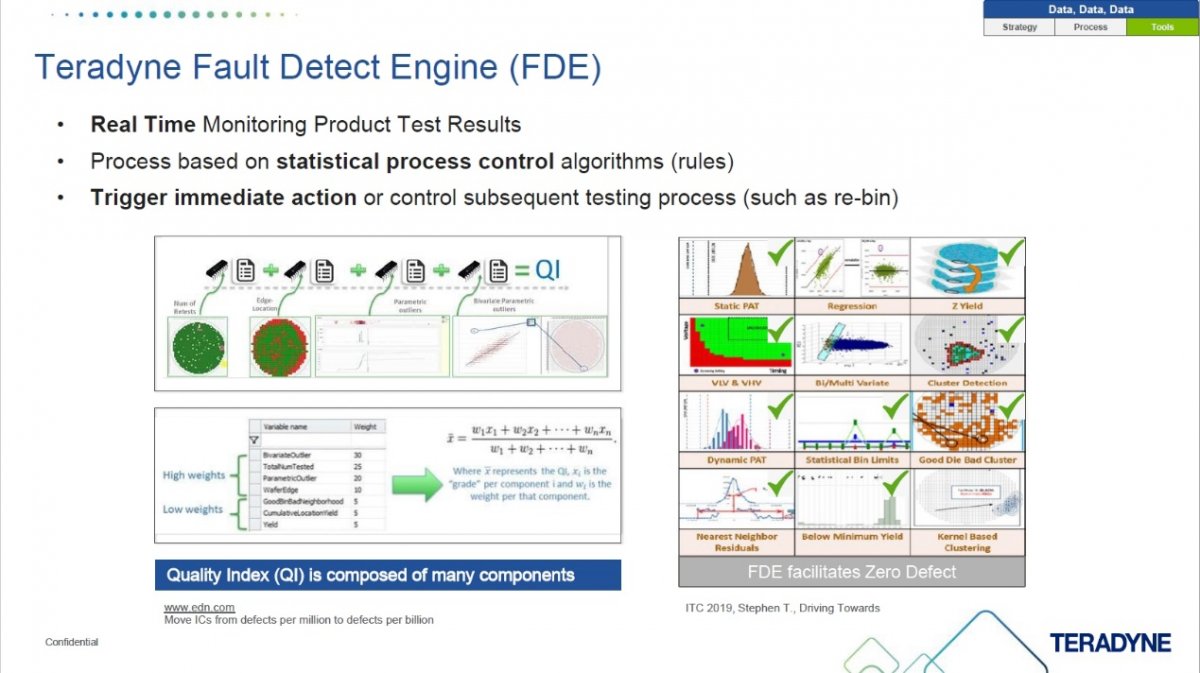

芯片测试会产生巨量数据。测试结果出来之后,泰瑞达有哪些工具可以进行数据分析和反馈?

图:数据分析工具

上图中间是一个刻蚀机,代表代工厂的工艺,有不同的控制按钮、不同的变量、不同的参数,制造出晶圆后用ATE机台测试,Fab可以根据实际测试数据反馈来调整工艺参数,优化工艺流程。在ATE测试晶圆时将大量数据传输给UltraEDGE服务器,在该服务器里会自建一些FDE(Fault Detect Engine)工具,做质量和数据统计,在其上也可以安装第三方数据分析软件,例OptimalPlus、PDF数据管理软件,进行加密和机器学习,对抓取到的原始数据进行分析,然后进行不同的统计分析,例如针对车规的更严格要求。之后形成晶圆图。在晶圆上的多个Die中,绿色表示通过,红色表示失效,蓝色可能存在一些边缘性的问题,把一些潜在的缺陷问题体现出来。同样,这个数据可以反馈给代工厂,这样就有两条不同的途径进行工艺的调整和改善。

图:FDE把测试结果反映到每颗Die上

车规芯片和非车规芯片在测试上有什么不同?“每颗芯片都会用不同的设计规则。你到代工厂去投片,同样是7nm,但有一条专门做车规制程,收费也完全不一样。这样设计、制造出来的芯片就是用在车上的,如ADAS芯片。对泰瑞达来说,设备都类似,唯一不一样的是后面的数据处理,如UltraEDGE、FD Engine的统计分析,主要还是因为芯片测试要求提高了,不再是通过或不通过或追求只看性能规格的测试,而是要看它的统计分布,还要看在每个晶圆上的物理分布,还有最低良率要求,每个温度下的要求。实际上就是通过统计分析排布后再去确定到底通过或不通过。后面其实是大数据分析。”Felix Huang解释到。

“为什么是数据、数据、数据?数据后面的分析最终是看质量指标,不是只看最早的测试结果,而是要将不同统计结果合在一起来判断。所以,涉及车规芯片要求,特别涉及到车身安全、行车安全,它的标准会更严格。我们的目标是0 DPPM。在整个过程中,数据和相关分析软件非常重要。”

“作为总结,测试的时候一定要定义好测试策略,包括用EDA软件做早期的器件调试,像我们的PortBridge工具;在整个开发和发布的流程中,我们要用IG-XL、Oasis保证测试程序质量的可靠;分析从前到后的数据,要有很强大的数据分析软件,才能实现测试零缺陷。”Felix Huang最后表示。