在过去几年的半导体行业下行周期里,存储芯片成为下滑幅度最多的细分芯片类别,一度进入了“历史性的寒冬期”。但从2023年开始,在AI技术以及相关应用的助推之下,存储芯片逐渐实现了恢复性增长,特别是高性能存储芯片的需求被激发,推动了存储行业周期性拐点的到来。

尽管目前大部分回升的存储芯片需求主要来自DRAM内存产品,尤其是被AI大模型带火的高带宽存储(HBM),但3D NAND因其更高的存储密度和更低的成本,也正受益于AI技术这一发展趋势。

不过,3D NAND技术虽具有诸多应用优势,但其制造过程复杂且资本投资高,其架构也存在一些瓶颈,限制了通过增加器件层数来提升架构密度,在良率提升和经济规模上面临着较大挑战。

最近几年,业界特别是存储原厂仍将层数之争作为3D NAND竞争的焦点,同时更是在1000层的3D NAND发展上进行了广泛探讨与技术验证。

值得一提的是,最近各大存储巨头在3D NAND技术创新方面动态频出,或宣布新的技术应用规划,或推出创新型集成解决方案。产业链厂商或研究机构也在创新制造工艺、新型材料等方面,为3D NAND存储密度和层数提供技术性的支撑,在一定程度上助推了这一场3D NAND的技术应用角逐战。

3D NAND层数之争愈演愈烈

当前,存储芯片领域需求最为紧张的仍然是HBM,但AI大模型客观上也推动了NAND需求,特别是AI手机、AI PC等端侧设备被业界和市场推崇,使3D NAND成为存储芯片领域相对较快走出行业下行周期的产品类别。因此,在一定程度上来说,NAND本身就处在AI生态链中,也将“享受”到AI时代下的应用机遇。

一方面,消费者对AI助手和端侧处理等增强功能的需求不断增加,推动了AI手机和AI PC市场的快速增长。另一方面,各大科技巨头纷纷布局AI PC和AI手机,比如微软、苹果等均在开发能够运行AI功能的移动终端,推动了AI技术的成熟应用,也进一步刺激了消费者对高效计算和辅助智能化的需求。

研究机构Counterpoint Research预测,2024年将成为全球AI手机时代的开端,到2027年底,内置AIGC功能的智能手机出货量预计将超过5亿部。Canalys也预测,2024年全球AI PC出货量将达到4800万台,占PC总出货量的18%,并在未来几年内加速渗透。

这些新增AI功能的移动终端无疑将对NAND的存储容量和性能提出更高的要求,毕竟一个330亿个参数的大型语言模型就需要33GB的存储空间。

当然,除了移动终端之外,企业级固态硬盘(SSD)、汽车、数据中心、服务器以及超融合基础设施(HCI)等也将带动大数据洪流,催生高性能、大容量的NAND存储的需求。据CFM闪存市场数据显示,2024年第一季度全球NAND Flash市场规模已环比增长24.2%至151.78亿美元。

同时,值得关注的是,除了市场需求增长之外,AI和大数据对存储器的性能需求与规格的变化,也在一定程度上改变了半导体存储的角色,从幕后走向台前,协助高性能运算,最终实现储存及运算一体的性能表现。而且,过去一年多来,通过3D堆叠工艺来提升NAND的存储密度、容量的策略,似乎正在不断优化和创新。

2023年8月,SK海力士发布了321层“4D NAND”样品,把3D NAND堆叠层数带入“300层时代”。

今年4月,三星宣布量产第九代V-NAND 1Tb TLC产品,层数达到290层,主要面向大型企业服务器以及人工智能和云设备。

同月,美光科技宣布其232层QLC NAND量产,并在部分Crucial英睿达固态硬盘(SSD)中出货。

6月,西部数据也在投资者活动上预览了其创新的BiCS 8 2Tb QLC NAND闪存芯片,采用了218层的堆叠技术,且自称是目前业界该类型最高密度的闪存产品。

实际上,自三星2013年设计出垂直堆叠单元技术后,各大存储厂商就在层数上暗自较劲,NAND Flash闪存堆叠层数不断被刷新,3XX与4XX等更高层数的存储技术路线图也被曝光。

不过,在层数竞争上,三星应该是最积极的存储大厂。早在2022年12月,三星就在其技术博客上宣布将开发3D NAND技术,目标到2030年达到1000层。然而,1000层的3D NAND的研发计划最近又被铠侠提及。

铠侠CTO柳茂知

关于3D NAND层数发展趋势,铠侠CTO柳茂知在2023中国闪存市场峰会(CFMS 2023)上曾接受《电子工程专辑》采访时表示:“从技术角度来看,存储芯片增加到400-500层仍然具有技术可行性,而且随着层数的增加,单位容量的成本也会下降,但500层之后则比较难预估。”从其表述上,可略微感受到他对这一发展趋势持谨慎保守的态度。

然而,最近铠侠在东京城市大学举行的第71届应用物理学会春季会议上却透露,计划在2031年前实现大规模生产超过1000层的3D NAND闪存,且就实现1000层以上3D NAND器件的技术挑战与解决方案进行了相关的阐述。

由此可见,在AI时代里,深度学习模型催生的快速处理和庞大数据集分析能力,对存储系统的数据读写提出了更高的要求,也进一步推动了各大存储大厂之间的3D NAND层数和存储密度的技术竞争,且不断有相关的技术创新和工艺改进来支持。这似乎预示着1000层的3D NAND已有技术可行性。

如何实现更高层数3D NAND?

尽管业界对3D NAND堆叠的层数越来越乐观,但不能忽视的是,随着垂直堆叠和向更小单元设计的扩展,工艺复杂性、成本和上市时间成为了影响制造量产和盈利能力的最大挑战。

单纯从技术来看,尽管3D NAND在一定程度减少了光刻缩微工艺的限制,但却增加了沉积和蚀刻的难度。随着堆叠的层数不断增加,3D NAND需要解决堆栈过程中的蚀刻问题,即必须蚀刻具有非常高纵横比(晶圆上形成图案的深度与宽度之比)的非常深的孔。这也使得一次性蚀刻更深的孔会具有更大的技术挑战,也无法提高蚀刻速度。

同时,除了蚀刻之外,还需要用非常薄的介电层上下均匀地填充这些孔,而沉积几纳米的层并不容易,仍然具有挑战性。

因此,在超过128层之后,很多存储厂商都将解决方案投向了多层堆叠工艺。比如,SK海力士的321层“4D NAND”就采用三重堆叠技术,涉及生产三组独立的3D NAND层,每组分别堆叠为120层、110层和91层,然后组合成一个芯片。这种方式的好处显而易见,更少的层数更容易进行刻蚀。

据悉,三星最近量产的290层的第九代V-NAND就采用了双层堆叠的方式,而计划于2025年推出的第10代NAND芯片,也将采用三重堆叠技术,达到430层。

不过,除了技术可行性,成本效率也是3D NAND需要考虑的重要因素。虽然多层堆叠能在一定程度上解决刻蚀的问题,但未来堆叠更高层数,比如1000层3D NAND,就需要考虑坍塌、弯曲、断裂等诸多稳定性问题,而且还需进一步降低成本。

过去数十年,CF基气体一直用于绝缘膜蚀刻。在CF基等离子体中,CF基聚合物厚厚地沉积在孔的侧壁上。虽然这种聚合物可以防止横向蚀刻(防止弯曲),但孔越深,到达孔底部的CF自由基就越少,孔的蚀刻速率就会急剧降低。而且,通过提高芯片温度等方法,虽在一定程度能加大CF基聚合物向孔底的输送,减少沉积在孔的侧壁而防止横向蚀刻,但能优化的程度有限。因此,几年前业界就在探索低温蚀刻技术,希望一步操作就可同时去除材料并在低温下钝化侧壁,也就是在单层非堆叠工艺下突破128层的工艺限制。

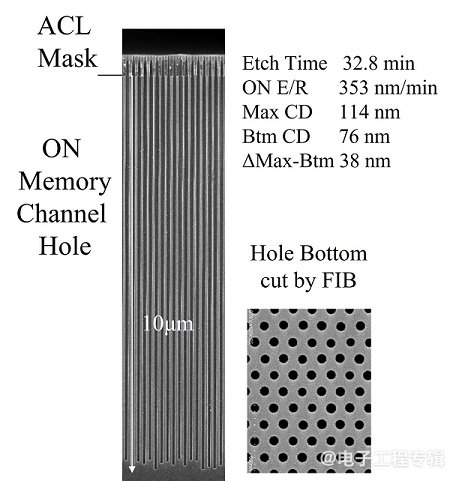

2023年,Tokyo Electron就开发了一种用于存储芯片的低温通孔蚀刻设备(图1)。该设备技术首次将电蚀刻应用带入到低温范围中,研制出了具有极高蚀刻速率的系统。该工艺技术可在短短33分钟内实现10μm深的高纵横比蚀刻,更适用于制造400层以上堆叠的3D NAND闪存芯片。

图1:通孔的横截面SEM图和孔底部的FIB切图。(来源:TEL)

具体原理是,通过HF+PF3的新气体系统与极低温度(公告中为-60℃)相结合,实现3D NAND内存孔的高速蚀刻,即在HF/PF3+Cryo的情况下,孔的侧壁上几乎没有沉积,反应物质HF被供应到孔的底部,进而实现高速、无横向蚀刻的工艺制造。

同时,在3D NAND中堆叠更多的Si3N4/SiO2层是提高其存储密度的关键。而对于SiO2,温度越低,蚀刻速率越高,添加PF3可以加快蚀刻速度。这也意味着进一步降低温度,可能刻蚀的速率更高。

这意味着利用低温刻蚀的技术可以一次实现更高层数3D NAND的高纵横比刻蚀,减少堆叠的次数,降低了工艺的复杂性和生产成本,也更易实现1000层3D NAND。

目前,三星、SK海力士已经在对TEL这款低温蚀刻设备进行测试,以生产更高层数的3D NAND。最近,铠侠也表示,计划于2026年量产第10代NAND,并决定采用低温蚀刻技术。

当然,更大层数的3D NAND还面临着其他的技术难题,比如单元间干扰、缩短层高以及扩大每层存储容量等挑战。因此,除了设备工艺之外,业界还需从材料的角度去探索相关的解决方案。

对此,最近有媒体报道,三星正与KAIST等研究机构合作,积极探索“铪基薄膜铁电(Hafnia Ferroelectrics)”作为下一代NAND闪存材料,希望这种新材料可以堆叠1000层以上的3D NAND。

还有哪些方式提升存储密度?

尽管3D堆叠目前是NAND容量扩展主流的技术路径,但不是唯一。与垂直缩放相比,虽然横向缩放受限于光刻工艺,带来的密度增益越来越小,但其确实可以在不增加WFE强度的情况下,实现线性成本的降低。在NAND扩展上,铠侠不像其他存储厂商那样热衷于通过堆叠层数来增加存储的容量,还会考虑平面密度的提升,以及成本的问题。

柳茂知就曾强调,“存储密度是王道,但3D NAND的层数并不等于密度。如果层度比较厚,那么整体密度也不会很高。如果存储器孔间距较长,则横向密度也不高。”他甚至指出,“通过放宽层厚和存储孔间距的选项,可以轻松实现更高的层数。但这不是铠侠的选择。”他仍然坚持通过垂直微缩以及横向微缩的高效布局,来提升存储密度,进而实现性能提升,以及更高的数据传输速率。

在CFMS 2024上,柳茂知再次分享了铠侠从四个方面来推进300层以上的NAND技术研发工作:一是横向缩放,即平面方向的微细化;二是纵向缩放,即层数;三是架构缩放,即CUA→CBA等;四是逻辑缩放,即TLC→QLC→PLC(图2)。

图2:NAND扩展存储容量的四种途径。(来源:Semianalysis)

对此,柳茂知也解释:“虽然层数的比拼能进一步提升单裸片容量密度,但并不是唯一途径,而且层数过高会带来Block增大的后果,给客户的系统级封装带来难度。”

在此,还需关注一下架构缩放,即通过把CMOS逻辑外围电路放置在NAND阵列的上方或下方来实现构建电路,节省芯片面积。不过,由于NAND阵列处理步骤非常严格,CMOS逻辑处理技术存在局限性。目前,很多储存厂商利用CMOS键合阵列(CBA),通过在单独的晶圆上制造逻辑,然后通过混合键合将逻辑键合到存储阵列晶圆上来解决此问题。

据悉,铠侠最新的BiCS 8采用的就是CBA晶圆键合技术,分别制造存储堆栈和CMOS控制电路,将CMOS直接混合键合在阵列之上。这种方法可在提升闪存读写性能的同时,有效提升闪存整体存储密度,降低运行功耗。

根据西部数据最新推出的BiCS 8 2Tb QLC NAND闪存芯片,BiCS 8颗粒在密度上比竞争对手高出15~19%,其中1Tb版本的TLC颗粒拥有与对手2xxL 1Tb QLC颗粒相媲美的存储密度。而在能效方面,BiCS 8闪存在编程能耗方面比竞争对手低13%。

实际上,从架构创新的角度,BiCS 8技术类似于长江存储Xtacking的CBA技术路线。这种架构创新方式还有一些其他的优势,比如,存储单元、外围电路分别在两片晶圆上并行加工,缩短生产周期;外围电路可以单独加工,与存储单元可以互相独立设计、生产,消除二者之间的设计、工艺牵制,实现更高性能。

但其实际意义还在于,外围电路面积与存储单元面积几乎相等,远超过现有主流3D NAND架构的外围电路面积。相对来说,外围电路晶体管密度可以比较低,可以使用成熟芯片工艺节点(比如28nm甚至更老的芯片工艺),无需先进工艺的光刻机。

值得一提的是,SK海力士的“4D NAND”则是将过去放置在存储单元旁侧的外围电路转移至存储阵列下方,减少了芯片占用空间,是3D NAND的另一种变体,被其命名“4D单元下外围(PUC)”。而美光科技针对这一架构设计,命名为“CMOS阵列下(CuA)”。可以说,以上几家存储厂商的架构扩展的思路基本一致。

至于逻辑缩放的方式,从未来技术发展与应用的角度,这应该是NAND扩展潜能最小的方式。

不过,整体来看,3D NAND可能会在技术和成本挑战中成为一场消耗战,需要综合考虑NAND扩展的最佳方式,而非单一技术路径的扩展。这也是铠侠一直坚持的NAND扩展的技术路径。

结语

如今,在生成式AI的推动下,数据量呈现爆炸式的增长,这使得如何找到创新的解决方案来存储海量数据成为一个重大挑战。随着AI终端搭载的NAND Flash容量翻倍成长,3D NAND将凭借低成本和大容量数据存储的性能优势提供硬件支持,其中QLC SSD的发展将是非常重要的一个方向。

从技术创新的角度,3D NAND未来的发展仍然聚焦在增加层数和提升密度两大方向,且呈齐头并进的发展态势,不断满足生成式AI大爆发时代对高性能存储的迫切需求。而当前存储厂商在3D NAND上的创新步伐,不仅打破了此前“3D NAND可能会在300层或接近300层时失去动力”的预判,而且似乎也让“千层NAND时代”越来越近。

本文为《电子工程专辑》2024年8月刊杂志文章,版权所有,禁止转载。免费杂志订阅申请点击这里。