许多人都听说过缓存一致性这个术语,但并不完全了解片上系统(SoC)器件,尤其是使用片上网络(NoC)的器件中的注意事项。要了解当前的问题,首先必须了解缓存在内存层次结构中的作用。

内存层次结构中的缓存

CPU内部有相对较少的速度极高的寄存器。CPU可以在一个时钟周期内访问这些寄存器。但是,它们的存储容量很小。相比之下,访问主内存以读取或写入数据需要耗费许多时钟周期。这往往会导致CPU大部分时间处于空闲状态。

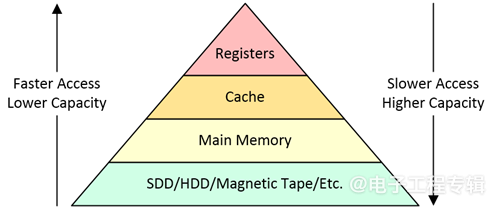

1965年,英国计算机科学家莫里斯·威尔克斯(Maurice Wilkes)提出了高速缓存和内存缓存的概念。这包括在CPU附近放置少量称为缓存的快速内存。“缓存”一词本身来自法语单词“cacher”,意为“隐藏”或“隐瞒”,其概念是利用缓存将主内存隐藏在CPU之外。涉及简单缓存的内存层次结构的高级视图如图1所示。

图1:显示缓存在内存层次结构中位置的高级视图。(来源:Arteris)

这一过程的运行基于两个关键点。首先,当CPU上运行的程序涉及主内存中的一个位置时,通常会对附近的几个位置执行操作。因此,当CPU请求从主内存中获得单个数据时,系统会从附近的位置引入数据。

这种方法可确保相关数据在需要时随时可用。其次,程序通常会对相同的数据集进行大量操作。因此,将常用数据存储在最靠近CPU的缓存中是有益的。这种接近性允许更快地访问数据和处理数据。

SoC环境中的缓存

在SoC中,缓存是在高速、高功耗、低容量的SRAM中的片上实现的。同时,主存储器是在印刷电路板(PCB)上的片外实现的,通常采用低速、低功耗、高容量DRAM的形式。

为了最大限度地减少延迟,设计人员在当今的许多SoC中添加了多级缓存。这些缓存通常包括两个级别:L1和L2。L1缓存最靠近CPU,容量最小,但访问速度最快,通常在1到2个时钟周期内。L2缓存距离CPU稍远,容量更大,但访问速度较慢,通常在4到10个时钟周期之间。

多级缓存可最大限度地提高性能,同时最大限度地减少对主存储器的片外访问。访问此主存储器可能会消耗数百个时钟周期。通过使用多级缓存,可以更快地从这些缓存而不是较慢的主存储器中检索数据,从而提高整体系统的效率。

当涉及多个CPU内核时,所有这一切的复杂性都会增加。考虑一个常见的场景,集群中有四个CPU内核,标记为内核0到3,每个内核都有自己专用的L1缓存。在某些实施方案中,每个内核还有自己专用的L2缓存。在其他设计中,内核0和1共享一个L2缓存。这些不同的配置会影响数据在不同缓存级别上的存储和访问方式。

通常,单个集群中的所有处理器内核都是同构的,即它们的类型相同。然而,拥有多个处理器内核集群的情况越来越普遍。在许多情况下,不同集群中的内核是异构的,或者说是不同类型的。例如,在Arm的big.LITTLE技术中,“big”内核旨在实现最高性能,但使用频率较低。

“LITTLE”内核则对能效进行了优化,使用频率更高,但性能较低。例如,在基于Arm的智能手机中,“big”内核可能会被激活用于Zoom通话等相对不频繁的任务。相比之下,“LITTLE”内核可以处理更常见、要求不高的任务,如播放音乐和发送短信。

维护缓存一致性

在有多个具有独立缓存的处理单元共享同一主内存的系统中,共享数据可能拥有多个副本。例如,主内存中可能有一个副本,而每个处理器的本地缓存中可能有更多副本。要维护缓存的一致性,就必须在所有副本中都反映出对一份数据副本的所有更改。这可以通过用新数据更新所有副本或标记其他副本无效来实现。

缓存一致性可以在软件控制下维护。但是,软件管理的一致性非常复杂,调试起来也很困难。尽管如此,通过缓存清理等技术仍可实现一致性,即把缓存中存储的修改数据标记为脏数据,这意味着必须将其写回主内存。缓存清理可以在整个缓存或特定地址上执行,但需要耗费大量CPU周期,而且必须在持有数据副本的所有CPU上执行。

维护缓存一致性的首选方法是使用专用硬件,在软件无法察觉的情况下管理缓存。例如,与处理器集群中的内核相关联的缓存,通常包括维护缓存一致性所需的所有硬件。

用还是不用

SoC由大量称为知识产权(IP)块的功能块组成。处理器集群就是这样一个IP块。连接IP块的常见方法是使用NoC。

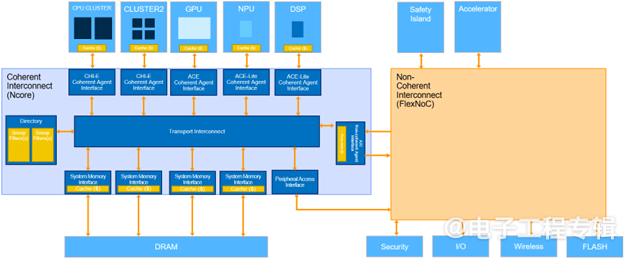

在许多SoC设计中,处理器集群外部不需要一致性,因此可以使用非一致性或IO一致性的AXI5或AXI5-Lite NoC,例如Arm的NI或Arteris的FlexNoC。但是,对于具有多个处理器集群、缺乏固有缓存一致性的SoC设计,或者在集成需要缓存一致性的第三方IP或自定义加速器IP时,则需要一致性NoC。这方面的例子包括使用AMBA CHI协议的Arm CMN或使用AMBA ACE和/或CHI的Arteris Ncore。

图2:在上述示例中,主系统采用了一致性NoC,而安全岛则采用了非一致性NoC。(来源:Arteris)

在整个芯片上普遍应用缓存一致性会耗费大量资源,而且对于特定组件而言也没有必要。因此,如图2所示,将缓存一致性隔离到CPU集群和特定加速器IP等芯片子集,可以更有效地利用资源并降低复杂性。一致性NoC(如Ncore)在需要严格同步的应用场景中表现出色。同时,非一致性互连(如FlexNoC)则在不需要严格同步的情况下非常理想。

设计人员可以从战略上平衡特定领域对数据一致性的需求,同时在不需要严格一致性的情况下从更精简的通信通道中受益。在当今复杂的异构SoC中,一致性和非一致性互连之间的协同作用已成为一种战略优势,可提高系统的整体效率和适应性。

Arteris公司产品管理和营销副总裁Andy Nightingale拥有超过36年的高科技行业经验,其中23年在Arm公司担任各种工程和产品管理职位。

(原文刊登于EE Times姊妹网站EDN,参考链接:SoC design: When a network-on-chip meets cache coherency,由Franklin Zhao编译。)

本文为《电子工程专辑》2024年8月刊杂志文章,版权所有,禁止转载。免费杂志订阅申请点击这里。