电子工程专辑讯 三星电子在晶圆代工领域屡屡碰壁,近期,台积电传出开始研究面板级封装(PLP)相关技术,包括扇出型面板级封装(Fan-Out -PLP,简称FO-PLP),《BUSINESS KOREA》报道称,三星电子在面板级封装 (PLP) 领域领先于台积电,此前,三星于 2019 年以 7850 亿韩元(约合 5.81 亿美元)从三星电机手中收购了 PLP 业务,这一战略举措为其当前的进步奠定了基础。

面板级封装(PLP)是一种从晶圆向更大尺寸面板级转换的方案。在应用和市场方面,许多封装技术可以被视为PLP,但由于FO-WLP的成功和市场认识,使得FO-PLP吸引到更多关注。

扇出型封装技术(Fan-Out Packaging Technology)目前存在两大技术分支,即扇出型晶圆级封装(FO-WLP)以及扇出型面板级封装(FO-PLP)。作为扇出型晶圆级封装 (FO-WLP) 的衍生产品,FO-PLP的重要性在于它能够容纳更多 I/O,通过允许将各种类型的设备封装在单个模块中来实现异构集成。

扇出型面板级封装 (FO-PLP) 代表了半导体行业先进封装技术的一次飞跃。

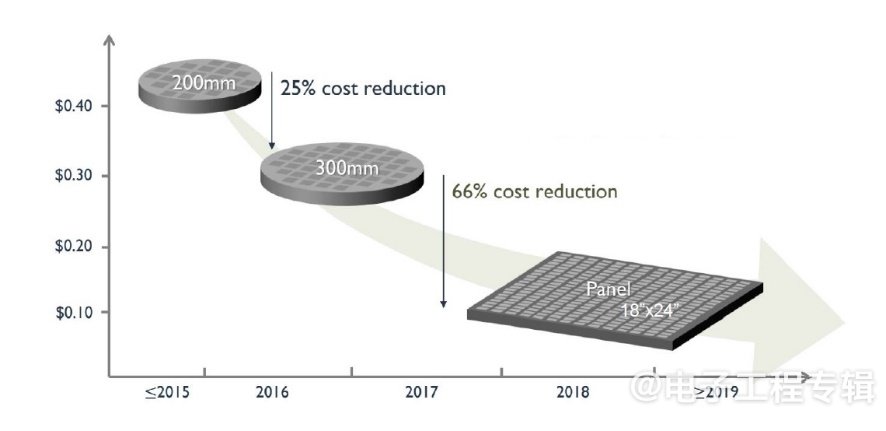

Yole 报告指出,FO-WLP技术面积使用率<85%,FO-PLP面积使用率>95%,可以放置更多的芯片数,成本也比FO-WLP便宜。具体推算从200mm过渡到300mm大约能节省25%的成本,从300mm过渡到板级,则能节约66%的成本。

这在更大程度上减少面积浪费并提高封装效率。

三星领先,PLP技术将缓解CoWos瓶颈难题

在 2024 年 3 月三星最近的股东大会上,三星电子半导体 (DS) 部门前负责人 Kyung Kye-hyun 详细阐述了 PLP 技术的必要性。他表示,AI 半导体芯片的尺寸通常为 600 毫米 x 600 毫米或 800 毫米 x 800 毫米,因此需要 PLP 这样的技术。"他还补充说:"三星电子也在开发并与客户合作。"

2015年,台积电凭借InFO-WLP(集成扇出型晶圆级封装)技术获得苹果A10全部订单。三星电子失利后,决定携手三星电机战略性开发出面板等级FO封装技术,于2019年收购三星电机的半导体扇出型面板级事业部,成为了第一家FO-PLP进入量产的厂商。

2016年,三星电机在韩国忠清南道天安投了2640亿韩元建立一个PLP项目,于2018年开始应用于自家智能手表Galaxy Watch的处理器封装中。在FO-PLP面板尺寸上,三星有使用过 510x415mm 尺寸的,也开发过高达 800x600mm 的面板。该技术在设计上,能提供灵活性,可以根据不同应用的需求定制封装方案。

台积电的先进封装技术有CoWos、3D SoIC,以及正在研发的PLP技术。

CoWoS(Chip On Wafer On Substrate)是一种晶圆基板的2.5D封装技术。CoWoS封装技术包括CoWoS-S、CoWoS-R和CoWoS-L,近年来台积电在CoWoS技术的重点放在大尺寸的AI芯片需求上。据悉,台积电涉足PLP研究的背后原因是对CoWoS 技术长期瓶颈问题的回应。

IDC 的报告指出,英伟达的AI芯片订单需要台积电CoWoS 产能的一半来完成,但目前仅能确保约三分之一的产能。当前,台积电的CoWoS月产能约为1.5万片,2024年底该产能将提升至2.6-2.8万片/每月。尽管台积电将产能提高了一倍以上,但仍要面对来自 AMD 和 Broadcom 等无晶圆厂公司对台积电 CoWoS 产能的竞争,使这一计划面临挑战。

台积电的技术研讨会指出,2022年到2026年,台积电CoWoS产能预计将超过60%的年复合增长率增长,到2026年底,每月的CoWoS晶圆产能将达到约6万片。

近期,台积电位于中国台湾西南部嘉义县太保镇的 CoWoS 封装厂因发现历史文物而停工,进一步加剧了台积电在CoWoS上面临的瓶颈问题。

英伟达正在规划将GB200提早导入扇出面板级封装(FO-PLP),起初计划是2026年,现提前到2025年,以缓解CoWoS先进封装产能吃紧问题。

包括 FO-PLP 在内的 PLP 技术,已成为台积电打破瓶颈的替代方案。

摩根士丹利的报告指出,台积电正在进行PLP封装技术的研究,但大规模量产还需要多年时间。

据《日经亚洲》报道,台积电正在探索510㎜ × 515㎜的矩形基板,其可用面积是12英寸晶圆的3倍多。

3D SoIC是台积电开发的先进封装技术,是业内第一个高密度3D chiplet堆叠技术,被视为“3D封装最前沿”的技术。3D SoIC设计的核心在于创造键合界面,使芯片可以直接堆叠在芯片上,从而实现更高的封装集成度和更小的凸点间距(最小可达6um) 。不过当前应用范围还比较小众,在AMD的Ryzen 3D和MI300 AI加速器中有采用。摩根士丹利指出,台积电预计在2025年将增加3D SoIC产能,预计每月的3D SoIC产能将达到大约12,000到14,000片晶圆;到2026年底,预计将增至每月20,000片晶圆。

未来几年,强劲的封装需求将成为台积电非晶圆收入快速增加的主要驱动力,摩根士丹利预计2023-2026年,台积电非晶圆收入的复合年增长率(CAGR)将达到31%;到2023年,非晶圆销售有望占到台积电总收入的13%。

向FO-PLP过渡面临的挑战

尽管 FO-PLP 前景广阔,但从晶圆到面板级加工的过渡仍面临着一些挑战。FO-PLP不会有边缘基板损耗问题,因为产量和材料利用率的提高,在效率和成本上都有进一步的优化。但是,面板级封装技术仍面临一些挑战。 譬如翘曲控制、芯片放置精度、检查和计量等。

翘曲控制:面板尺寸越大,翘曲程度越严重,影响光刻和层对齐。使用刚性载体和先进材料有助于缓解此问题。

芯片放置精度:芯片放置的高精度至关重要,因为未对准会导致封装缺陷。

检查和计量:面积越大,质量检查的复杂性和时间就越长。

要解决这些问题,还需要采取一些解决方案。譬如先进设备和自动化,通过开发强大的处理系统和利用自动化是保持精度和产量的关键;完善的 RDL 技术可提高互连分辨率,支持更细的间距和密集的封装配置。

此外,行业在指南和规范方面的合作确保了整个 FO-PLP 工艺的一致性和质量。

目前三星提供 I-Cube 2.5D 封装、X-Cube 3D IC 封装和 2D FOPKG 封装等先进封装技术,有报道称,三星计划将其 2.5D 封装技术 I-Cube 扩展到 PLP。与此同时,英特尔计划在2026年至2030年间量产使用玻璃基板的下一代先进封装解决方案。

起初,包括三星在内的FO-PLP技术主要应用在移动以及智能穿戴领域,2020年,5G、AI、自动驾驶以及服务器等需求对模块化和高速处理的需求急剧增加,FO-PLP的应用市场进一步拓展至射频芯片、电源芯片、芯片模组、高频芯片、物联网和人工智能芯片的先进封装应用。

三星推出FO-PLP 2.5D先进封装技术的主要目的是为了追赶台积电在AI芯片先进封装领域的领先地位。通过这项技术,三星希望能够吸引更多的客户,并在半导体封装行业中占据更大的市场份额。