得益于全球人工智能(AI)热潮下对先进制程芯片的需求持续飙升,2024年第一季度台积电结束了连续三个季度的降势,实现了自2022年以来最快的销售增长。在刚刚结束的台积电中国技术论坛上,台积电方面分享了其在工艺、封装、硅光子等领域的最新技术进展与路线图,《电子工程专辑》也对此进行了梳理,希望能帮助读者从中看到半导体产业未来的发展趋势。

深耕先进制程技术

期待未来几年内实现单芯片上超过2000亿个晶体管,并通过3D封装达到超过1万亿个晶体管,是台积电制定的雄心勃勃的技术突破计划。

作为第一家于2020年开始量产5纳米的晶圆厂,台积电通过推出N4、N4P、N4X 和 N5A等技术,持续强化其5纳米工艺家族,而最新推出的N4C技术以适用于更为广泛的应用。N4C延续了N4P技术,可将裸晶成本降低多达8.5%,且使用门槛低,计划将于2025年量产。N4C提供了面积效益更高的基础IP和设计规则,能够完全兼容已被广泛采用的N4P,因此客户可以轻松转移到N4C;该工艺还通过缩小裸晶尺寸提高良率,可为强调价值的产品迁移至台积电的下一代先进技术提供极具成本效益的选择。

而在移动和HPC应用驱动下,其3纳米工艺作为半导体产业中第一个实现高量产和高良率的工艺技术,也将快速、顺利地实现产能提升(ramping)。2024年和2025年,台积电将陆续推出N3P和N3X来提升工艺技术价值,在提供额外性能和面积优势的同时,保持了与N3E的设计规则兼容性,能够最大程度地实现IP复用。最新的消息显示,N3P已经完成认证,良率表现已接近N3E。

采用Nano Sheet技术的2nm节点预计2025年实现技术量产,预计将在2026年量产第二代N2P和A16(1.6nm)。与第一代N2工艺相较,N2P相同主频和晶体管数量的情况下,功耗可降低5%-10%,在相同功耗和晶体管数量的情况下,性能可提高5%-10%。表明晶体管架构已从平面FET演进至鳍片FET(FinFET),并将迎来再次变革,向纳米片发展。

除了纳米片之外,还有垂直堆叠的nFET和pFET,即CFET形态晶体管,它可能是晶体管升级的一个发展方向。台积公司一直在积极研究将CFET架构用于下一步技术升级,行业普遍认为这将是“Nano Sheet架构后下一代全新晶体管架构创新”。根据预测,考虑到布线和工艺的复杂性,CFET的密度增益可能在1.5-2倍之间。

除CFET外,台积公司在低维沟道材料领域也实现了突破,如WS2或WoS2等无机纳米管或纳米碳管,有助于进一步推动尺寸微缩和能耗降低。这也意味着台积电未来将CFET导入更先进埃米级制程外,也会持续推动更先进晶体管架构创新,实现让单一逻辑芯片容纳超2000亿颗晶体管的目标。

引入新的互连技术以提升互连性能,也是台积电为雄心勃勃计划的一部分,包括:在铜基互连领域引入一种新的通孔方案,将通孔电阻再降低25%;新的通孔蚀刻停止层,将耦合电容降低约6%;新的铜势垒,可以将铜线电阻降低约15%。除铜互连外,台积电还在研究一种可以将耦合电容降低约25%的含有气隙的新型金属材料,以及可显著缩短互连时延的插层石墨烯新材料。

先进封装技术加速前进

为了进一步发展微缩技术,以在单芯片片上系统(monolithic SoCs)中实现更小且更优异的晶体管,台积电开发了3DFabric技术,希望通过发挥异质整合的优势,将系统中的晶体管数量提高5倍,甚至更多。

目前,TSMC 3DFabric技术组合包含三大平台:TSMC-SoIC®、CoWoS®和InFO。其中,SoIC平台用于3D芯片堆叠,并提供SoIC-P和SoIC-X两种堆叠方案,从技术角度来看,SoIC芯片可以根据产品集成需求整合于CoWoS或InFO。

例如SoIC-P是一种基于凸块(Bumped)的堆叠方案,适用于对成本比较敏感的应用,如移动应用; SoIC-X是无凸块(Bumpless)堆叠方案,无论是现有的晶圆“正面对背面”堆叠方案的9微米键合间距,还是将于2027年上市的晶圆“正面对正面”堆叠方案的3微米键合间距,其裸晶到裸晶(die-to-die)互连密度均比40微米到18微米间距的微凸块F2F堆叠方案高出10倍以上。SoIC-X尤其适用于对性能要求极高的HPC应用,台积电方面预测预计到2026年底将会有30个客户流片。

CoWoS平台包括成熟度最高的基于硅中介层的CoWoS-S,以及基于有机中介层的CoWoS-L和CoWoS-R三种方案,通过将先进的SoC或SoIC芯片与HBM集成,可助力高规格的AI芯片上市——在台积电与英伟达合作推出的Blackwell AI加速器中,全球首款量产的CoWoS-L产品就将2个N5 SoC和8个HBM堆栈集成于一个模块;而AMD MI300A/MI300 X则是第一个采用CoWoS和SoIC-X技术的产品。

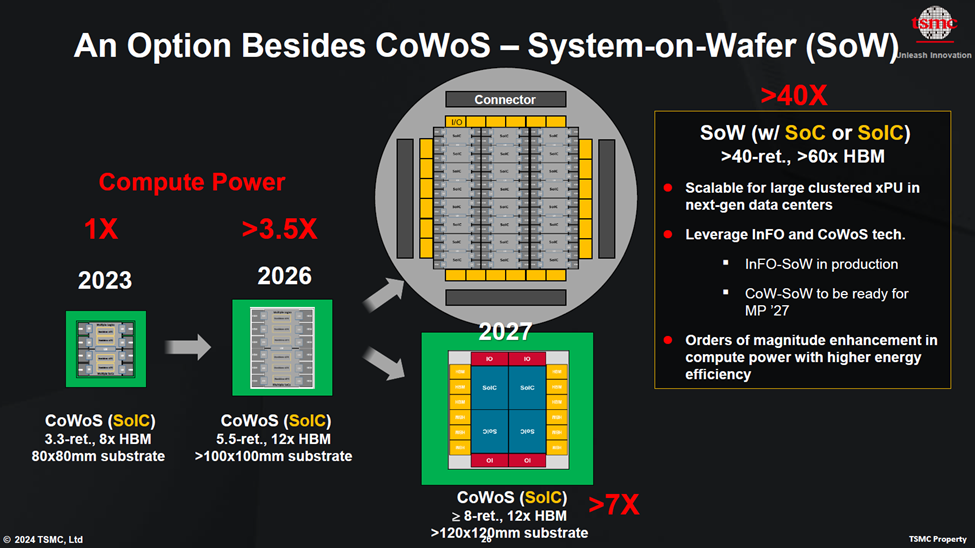

台积电已通过CoWoS-S生产线交付SoIC,并计划开发一种8倍光掩模大小的CoWoS,包含A16 SoIC芯片和12个HBM堆栈,支持更大的120mm x 120mm基板,算力将提高40倍,预计将于2027年量产。到今年年底,台积电将为超过25个客户实现150多个CoWoS产品流片。

InFO PoP和InFO-3D针对高端移动应用,InFO 2.5D针对HPC芯粒集成。此外,继2023年推出支持车用客户及早采用的N3AE制程之后,台积公司通过整合先进芯片与封装来持续满足车用客户对更高运算能力的需求,以符合行车的安全与质量要求。台积公司正在研发InFO-oS及CoWoS-R解决方案,支持先进驾驶辅助系统(ADAS)、车辆控制及中控计算机等应用,预计于2025年第四季完成AEC-Q100第二级验证。

系统级晶圆(System-on-Wafer, SoW)技术方面,台积电计划借助成熟的InFO和CoWoS技术来扩展新一代数据中心所需的算力,并计划在2027年推出基于CoWoS的SoW,它将集成先进的SoC或SoIC、HBM及其他元件。

特殊制程技术

特殊制程方面,就已公开的资料来看,今年的技术论坛没有像2023年那样围绕汽车、先进射频、超低功耗、MCU/嵌入式非挥发性存储器、CMOS影像感测等多个领域展开介绍,只是重点介绍了在硅光子领域的最新进展。

硅光子是共封装光学器件的最佳选择,因为它兼容半导体,并且可与EIC/PIC/交换机在封装层面高度集成,成为台积电的关注点并不令人感到意外。创新型COUPE(紧凑型通用光子引擎)解决方案通过最短路径的同质铜-铜接口将PIC和EIC集成起来,并可实现超高速射频(RF)信号(200G/λ),核心优点是占用面积最小,并含有光栅耦合器(GC)和边缘耦合器(EC),可满足客户的不同需求。

根据规划,台积电计划在2025年完成小型插拔式连接器的COUPE验证,然后在2026年将其集成于共封装光学器件的CoWoS封装基板,将功耗降低2倍而将时延缩短10倍。与此同时,台积电还在探索一种更为先进的共封装光学方案,将COUPE集成于CoWoS中介层,从而将功耗再降低5倍而将时延再缩短2倍。

全球范围内继续扩充产能

为了满足客户不断增长的需求,台积电加快拓展晶圆厂的脚步始终没有放缓的迹象。从2017年到2019 年,公司平均每年进行大约2期的晶圆厂建设工程;从2020年到2023年,台积电晶圆厂的平均建设进度大幅增加至每年约5期;到了2024年,在建的工厂数量达到了七座,包括三个晶圆厂、两个封装厂、以及两个海外晶圆厂。

布局方面,位于台湾新竹的Fab 20和高雄的Fab 22均为2nm晶圆厂,目前已开始装机,预计2025年量产。在美国亚利桑那州建造三期晶圆厂,目前第一期已经开始移入设备,预计明年量产4nm晶圆;正在兴建中的第二期预计2028年量产3nm晶圆;规划中的第三期预计2030年之前进入量产。在日本熊本兴建的第一座晶圆厂,预计在今年四季度提供16/28nm技术;第二晶圆厂预计2027年量产6/7nm制程。此外,台积电还计划在今年第四季度开工建设位于德国的16nm晶圆厂,预计可在2027年实现量产。

先进封装产能方面,根据规划,到2026年,台积电CoWoS生产线的年复合增长率将超过60%,年底产能将是2023年的4倍;SoIC产能将比2023年增长8倍,年复合增长率高达100%。

不容小觑的成本压力

无论是先进工艺,还是先进封装,各种“先进”背后的投入也不是不计代价的,在高昂的成本压力面前,即便是台积电这样的大厂也得想方设法节约资本支出,降低成本。

成本压力一方面当然来自先进的技术。相关分析机构的数据显示,与3nm处理器相比,2nm芯片成本将增长约50%。以一个产能约为每月50000片2nm晶圆产线为例,其成本约为280亿美元,相比之下同产能的3nm产线的成本约为200亿美元,EUV光刻设备数量的增加被视作成本增加的主要原因之一。即便有苹果、英伟达、高通、AMD下单,台积电肯定也要在成本控制上下点功夫。

所以,台积电发力先进封装也是可以理解的。毕竟相对于传统封装,3D封装技术搭配先进制程是降低总体成本的有效手段,这对AI服务器处理器来说尤为关键——台积电与英伟达合作推出Blackwell AI加速器,与AMD合作推出 MI300A/MI300 X都是如此。

总裁魏哲家预测,未来五年AI服务器处理器将以50%的年复合增速增长,到2028年占台积电整体营收比例将超过20%。现阶段大多数AI加速器采用台积电4/5nm制程,且考虑到先进制程带来的节能表现,客户对3nm乃至2nm的采用意愿相当高,越来越多的客户希望能够使用2nm制程。为此2年之后,台积电很有可能就将从3纳米走向2纳米。

另一方面,根据台积电2024年Q1财报,其3nm、5nm和7nm工艺的出货量分别占总收入的9%、37%和19%,三者相加达到了销售金额的65%,低于上一季度的67%,主要是3nm工艺出货量下降,拉低了产品均价。同时,这一季度内,台积电单片晶圆(等效12英寸)收入约为6228美元,环比下降407美元。

魏哲家指出,与去年第四季度相比,部分产业复苏速度低于预期,因此将对今年全球半导体市场(不包括存储芯片)增幅从此前预计的20%下调至10%,台积电本身则维持同比增长21-26%的增速。而在定价策略上,魏哲家表示,海外厂成本高,且有通胀影响,预期客户会分担更高成本,台积电将通过策略性定价、与当地政府保持密切合作确保支持等手段保持长期毛利率。

还有一点也很关键,就是发力先进制程和先进封装的还有三星和英特尔两大巨头。比如三星除在进行3nm GAA工艺大规模量产之外,也在同步研发2nm工艺节点,预计将在2024年第二季度完成其2nm(SF2)工艺的开发,大规模量产预计将于2025年下半年开始;英特尔“四年五个制程节点”的目标(2nm、1.8nm和Intel 20A和Intel 18A)推进也比较顺利,High NA光刻机以及PowerVia背面供电技术的加持,让英特尔对在2025年重夺制程领先性保持乐观。

先进封装领域,英特尔宣布其首个3D封装技术Foveros已实现大规模量产;三星除了已有的2.5D芯片封装技术FO-PLP外,其3D封装技术X-Cube预计将在今年量产,为AI芯片开发的最新3D封装技术SAINT已有部分通过了验证测试,如果再考虑他们布局已久的玻璃基板领域,头部企业之间的在技术、成本、市占率等领域的较量将会更加激烈和胶着。