随着人工智能的蓬勃发展,对高算力、高存储需求的增长,HBM正展现出广阔的发展前景,但同时也面临技术难题、产能不足等挑战。近日,SK海力士负责良率的副总裁Kwon Jae-soon在接受英国《金融时报》采访时表示,“我们已成功将HBM3E芯片量产所需的时间缩短了50%。这些芯片的良率已几乎达到80%的目标。”

这是SK海力士首次公开披露HBM3E的产量信息。此前,业界预计SK海力士的HBM3E良率在60%-70%之间。

目前,全球HBM市场被三大原厂占据,其中SK海力士技术领先,占据市场主导地位。SK海力士是英伟达HBM3内存唯一供应商,并于3月份开始量产最新一代HBM3E。

目前,美光科技和三星等竞争供应商正在开发自己的HBM产品,以争夺SK海力士主导的HBM市场。但美光科技在HBM市场上处于劣势,市场份额仅为10%。三星电子在HBM领域也面临挑战,其HBM3良率低于20%,最近也未通过英伟达的产品认证。

Kwon Jae-soon还强调:“我们今年的目标是专注于生产8层HBM3E。在人工智能时代,提高产量对于保持领先地位变得更加重要。”

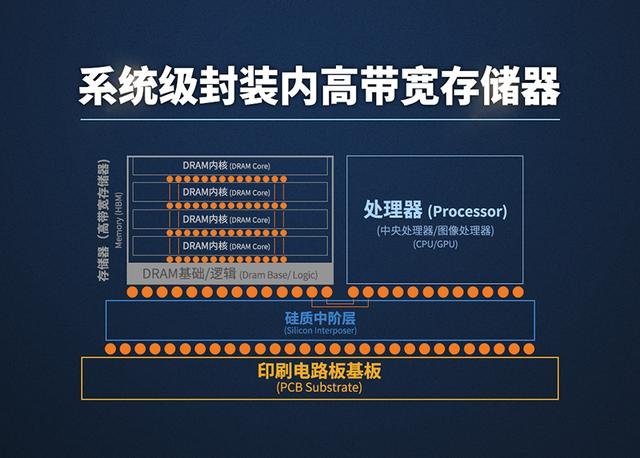

HBM内存结构示意图。图源:SK海力士

不过,由于HBM制造需要垂直堆叠多个DRAM,因此工艺复杂度比标准DRAM更高,尤其是HBM3E的关键部件硅通孔(TSV)良率一直很低,仅为40%至60%。具体而言,HBM3E技术难度大的原因主要包括以下几点:

一是高层堆叠设计:HBM3E采用了12层的垂直堆叠设计,这种设计在制造过程中需要极高的精度和复杂的工艺技术。每增加一层,都会对制造工艺提出更高的要求,尤其是在保持良品率方面。

二是硅通孔(TSV)技术:HBM3E使用了硅通孔技术来连接不同层之间的DRAM,这种技术需要非常精确的设备和技术支持,以确保信号传输的稳定性和速度。TSV工艺的难度较大,对生产设备和技术人员的要求也很高。

三是混合键合技术的应用:虽然对于未来的HBM4内存,SK海力士表示混合键合技术的应用将被推迟,但这表明即使是当前的HBM3E,在开发过程中也面临着如何有效地将不同的材料和组件结合起来的问题。这不仅涉及到材料科学的挑战,还可能影响到产能和产品质量。

据悉,SK海力士计划于今年第三季度供应12层HBM3E产品。12层HBM4(第六代)计划于2025年下半年推出,16层版本预计将于2026年投入生产。SK海力士预测,到2028年,主要用于AI应用的HBM和高容量DRAM模块产品将占据整个内存市场61%的市场份额。