这两年电子工程专辑谈先进封装、chiplet的文章算是很多了——现在聊先进封装、chiplet,已经不会有人再质疑其发展潜力。随着很多大算力先进封装芯片的问世和量产,大家在谈的话题普遍已经更加具体和确切了。

苹果用于Mac Studio的M1/M2 Ultra、英伟达刚刚发布的Blackwell GPU、Intel Sapphire Rapids等等都已经不单是将存储die与计算die基于先进封装做整合;Ponte Vecchio和Meteor Lake甚至都不是相同die的“复制粘贴”,已经在追求不同模块的协同互联。可见先进封装、chiplet已经进入到了高速发展期。

最近Aspencore举办的IIC Shanghai同期进行的“Chiplet与先进封装技术研讨会”上,中茵微电子援引来自Market.us的数据,2023年chiplet市场规模31亿美元,今年预计会达到44亿美元,2033年则会增长至1070亿美元,2024-2033的CAGR是42.5%——这个值是绝大部分半导体门类都很难达成的。

Chiplet生态链仍然是涉及EDA, IP, 前道fab厂, 以及后道传统OSAT的。这场“Chiplet与先进封装技术研讨会”也算是很难得的聚集了EDA, IP, OSAT,甚至上游材料企业参与对话。让我们有机会看到生态链上不同的角色对于chiplet和先进封装的看法。

虽然记录方式会比较流水账,而且受限于技术披露要求,本文不对任何演讲嘉宾展示的PPT材料做展示——相对的也就没有那么直观,不过我们认为这些内容仍有技术导览价值。若有错误,欢迎指正。

EDA:要解决的挑战不少

黄晓波博士(芯和半导体技术市场总监)说,2030年monolithic单die晶体管数量极限大约是2000亿,而基于先进封装的3DIC异构集成的芯片,晶体管数量会达到10000亿——这也是前年Intel提出的目标。

“在AI需求的驱动下,未来10年的算力需求会提升10万倍。”这就比前两年我们听Synopsys说达成千倍性能提升更为激进的预测,当时生成式AI的确还没有全面爆发。而万亿量级参数的AI模型,及传言中Sam Altman的7万亿美元AI芯片计划,Sora文生视频开启新的可能性,都令10万倍性能提升需求看起来的确像那么回事——即便这10万倍未必都来自先进封装。

从高抽象级角度来看,chiplet和先进封装其实就是把原本的一颗超大die,decompose切分成小die,再将这些小die“缝合”到一起。这样一来既绕过了潜在的reticle limit光罩尺寸限制,增大了芯片规模,而且也从系统角度提升了芯片制造的良率,并且可以基于不同die的需求采用不同的制造工艺,达成更高的成本和架构灵活性。

但这么做显然是要付出代价的——刘德启(中茵微电子副总裁、IP事业部总经理)举例说英伟达这一代GPU的研发预算达到了百亿美元,和国内芯片IC设计公司的研发投入完全不在一个量级。这是最直观的代价。不过我们认为这个数字,其实也和Blackwell的规模,及其构成的系统有关;而不单是chiplet与先进封装的关系。

如果要说得更具体些,我们去年的封面故事《谈谈chiplet的坏》大致提过chiplet和先进封装当前遭遇的挑战。黄晓波以AMD MI300为例,谈到了先进封装存在的难点。首先是复杂功能分解模块化,映射到大模块chiplet的问题;其次是很多采用chiplet的企业目前还在做封闭生态,“自家芯片开发,基于自家标准”,故而多chiplet并行体系结构和互联接口标准是个挑战;

随后是千亿晶体管芯片的仿真问题、万瓦功耗芯片散热和供电问题、高速连接信号完整性分析,以及热-应力-电耦合仿真的问题......“物理实现在chiplet这块就有变化,因为是基于多芯片3D布局布线,3D先进封装;另外还需要分析,按照传统2D布局,很多热、应力之类的问题,现在的技术就能控制;而2.5D/3D封装,层与层之间就没那么简单了。”这些都“需要新的流程,新的EDA平台”,“系统性”“一站式”解决问题。

“新的集成流程,架构、物理实现、分析、验证都需要重新考虑,而不再是传统的SoC设计理念与思维。”黄晓波说。架构方面,包括系统级连接、堆栈管理、层次化设计;物理实现则相关协同设计环境、跨领域工程变更、多芯片3D布局规划和布线、统一数据库;分析涉及到片上、封装电磁分析,芯片封装联合仿真,多物理分析,与布局布线工具无缝集成;验证涵盖了芯片工艺约束、封装制造设计规则、芯片3D组装约束、芯片数据通信协议等...

从EDA的角度来看,“现在EDA有很多瓶颈。”像MI300这样的设计,要求“系统级分析流程”“大容量仿真规模”和“高精度高效求解”。这里的系统级分析流程,具体是指目前很多EDA工具是以“单点”的方式去解决个别的问题,“解决电问题用一个点工具,解决热问题是另一个......”“要知道很多东西跨平台、跨软件工具以后,就会带来信息失真,无法获得统一可靠的结果”。要求“用于chiplet-interposer-package的整体流程”,“需要多物理场耦合分析和完善的数据后处理功能”成为必须。

与此同时,“像MI300那样Tx与Rx之间上千上万根走线,需要大容量规模仿真。”黄晓波谈到。另外跨不同尺寸的大模型仿真,才能全面收集电磁干扰、热、应力等信息。最后,高精度高效求解更无需赘言,“算得不准,算的时间过长都是不行的”。

据说芯和早在2015年就开始着手解决这些问题。“碰巧遇到了这样的风口,2019年就做了整体EDA平台的发布”。从设计角度来看,芯和提供“从架构探索到签核”的全流程覆盖2.5D/3D设计分析平台,“这个平台能够满足上千亿晶体管规模的chiplet集成”。

物理场仿真方面,自然是强调“跨尺度多物理场仿真”,“多物理场仿真”解决的是前面提到的chiplet本身的诸多挑战;这里的“跨尺度”应该是指die、interposer、基板、PCB等不同间距尺寸,实现“跨尺度仿真”。这一点非常重要,也是“系统级”实现的主要组成部分,技术上是芯和的核心竞争力。另外还有AI驱动的网格剖分技术,云计算加载的分布式并行计算能力等...

有关信号完整性问题,“2.5D/3D封装要考虑串扰、电磁辐射、链路损耗等问题”,芯和的平台工具做“电磁仿真+参数提取+信号链路分析”,“集成了业界2.5D/3D chiplet典型工艺”,“建模不需要手动去画模型,参数化模板调用模型,大大提升了效率”。

另外,黄晓波还提到大容量跨尺度引擎在仿真速度、精度、资源占用方面的优势;DC/AC仿真也能够满足大算力芯片真实应用场景;电热、应力仿真融合多物理量,“全方位考量物理量要素”;产品也匹配了主要foundry厂的工艺,对不同平台、标准做出支持。

现场还有一家EDA厂商Cadence虽然谈的主题并不以围绕chiplet为核心,但针对系统级分析挑战,利用AI技术的Optimality工具(Optimality Intelligent System Explorer),应用案例中提到112G Serdes、3DIC的PDN(供电网络)等,多少还是与chiplet发展大趋势相关的。

而且与EDA发展大趋势更有关联的是,Optimality是典型应用了AI技术的工具。从介绍来看,这是个系统级分析优化工具,用于系统级SI/PI, 3D电磁仿真分析等。王辉(Cadence 资深技术支持总监)主要强调了它在AI方面的技术,是“AI驱动的in-design分析和优化”。

因为传统优化方案在设定好目标以后,再对设计做出优化,“有经验的工程师可能会知道怎么去改不同变量,但你并不能搞清楚结果是否为最优”,“AI能够帮助你解决这样的问题”。王辉对比传统DOE设计优化,以及借助能够做强化学习的Optimality,“AI快速收敛得到目标值”,据说生产力总体能够提升10倍。

举例详谈到的针对112G PAM4 SerDes,基于一定范围内的6个变量,经由AI优化100次以内的迭代得到快速收敛,将SNR做到5倍性能提升;还有包括天线优化、FPC差分对优化带来插损和回损收益等都和chiplet关系没那么大,这里就不做详述了。不过作为AI驱动的多物理场优化软件,基于AI技术对电子系统做分析优化,基于chiplet的系统必然是未来这类应用的主角。

材料挑战:键和、散热、中介层与基板

在封装层面的结构发生变化以后,某些材料必然也是要遭遇挑战的。Resonac电子业务总部执行总监Hidenori Abe提到Resonac眼中,2.xD/3D封装的技术挑战主要包括两个方面(Resonac将基于RDL interposer的封装称作2.3D封装;Si interposer则为2.5D封装,所以这里标注了2.xD)。

其一是装配与键和方面的,包括微焊球、铜bump凸点的成型,接合位置的精度,以及空隙填充、泄放控制与无空隙实现。其次是散热相关的热解决方案,要求较高的散热效率,以及需求高热传导材料。

而在追求更高性能的先进封装方面,也有一些新的趋势。比如有机interposer中介层方面,行业在追求更精细的RDL工艺、高铜柱、芯片嵌入成型,以及更低成本的panel level制造工艺等。与此同时,substrate基板部分,走向L/S(线宽线距) ≤ 2/2μm,表面的高度平坦,无翘曲,以及所谓的glass core玻璃基板技术。

所以Resonac提供了对应的产品,包括面向2.xD/3D封装的“新材料”。比如说PID(Photoimageable Dielectric)电介质,可用于RDL和钝化层,特点主要是高分辨率(φ2μm Via)和较好的厚度均一性。对于RDL的精细曝光,Resonac也有可实现L/S<2/2μm的感光胶膜(dry film resist)产品,达成比较出色的曝光成型。

对于2.xD以及扇出型(Fan-Out)封装而言,则有对应的EMC(环氧树脂膜封塑料)产品,相比于传统的EMC,主要是具备明显更低的翘曲、低热膨胀系数(CTE)等。另外,在2.xD封装应用方面,还需要CUF(capillary under fill)填充材料——有用于interposer之下的CUF,也有之上的CUF——Hidenori提到Resonac的这部分产品,用于interposer下面时,具备高可靠性;而用在上面,即与die接合的填充,则可实现较窄的间隙填充,以及低CTE和高延展性。

此外,还有面向下一代先进封装技术,用于substrate的超低CTE、高模量材料,确保封装的低翘曲;以及用于小型Via构成的新型SR(Solder Resist)锡焊材料,可达成更小的bump间距,以及更大的基板尺寸(基于高抗裂特性)。

在面向2.xD封装的热界面材料(TIM)方面,垂直方面的高热传导很重要——Renosac有个TC系列垂直方向据说有石墨填充(graphite filler),具备大片、出色弹性的特点,当然高稳定性也很重要。还有用于substrate的die键和胶EN系列等等...这里不再一一列举。

这部分也算是予我们开阔眼界吧,只是遗憾Resonac的这些PPT并不对外分享——其中的很多材料用途还是要看图才会显得更加直观。Hidenori说Resonac为了克服各种技术困难,会积极地与不同的客户、设备、化学、材料合作伙伴组建联合封装解决方案中心:不仅是尝试发现问题,了解客户对材料的需求,也是对新的封装材料做尝试,想必前述先进封装材料研究也是其中的重点。

IP供应商:高速接口是关键

作为IP供应商,中茵微电子总结“chiplet产品成功的核心要素”包括多die协同的后端和DFT设计技术、先进封装与测试体系及良率提升、高速互联的全栈IP设计能力、丰富的合作伙伴和die资源、完善的供应链体系。这些其实也可以视作中茵微电子眼中chiplet产品的挑战,即便商业企业总结的挑战多少有站在自有产品与技术的角度。

如果抽象共性,这次“Chiplet与先进封装技术研讨会”两家IP供应商都提到的技术重点,似乎很大程度集中在了chiplet之间互联的接口上。芯原作为另一家参会IP供应商,用以谈chiplet的篇幅不多。汪志伟(芯原高级副总裁、定制芯片平台事业部总经理)主要谈到的是汽车电子接口IP与chiplet解决方案。据说基于芯原的参考设计,有客户已经设计出比英伟达Orin规格更高的ADAS芯片,其上NPU达成数百TOPS算力,“能和下一代Thor对标”。

汪志伟说芯原在车规级SoC芯片设计上积累了3年以上的经验,也积累了相当多的IP,其中也包括安全措施、汽车功能安全设计,以及基于现有硬件平台去开发自动驾驶特性。

“我们之前在帮助客户设计智能驾驶芯片时,发现芯片尺寸超过了400mm²。而且以后自动驾驶平台的要求只会越来越高。”汪志伟谈到,“那就必须要考虑借助chiplet技术来构建下一代智能驾驶技术平台了。”

芯原展示的下一代自动驾驶平台中间是个SoC die,其上有CPU, GPU, ISP, VPU, NPU等模块,这片die藉由D2D接口再分别连接到NPU chiplet, AI+ISP chiplt, 以及GPGPU chiplet。汪志伟说算力扩展可以借助NPU chiplet,达成上千TOPS算力都有可能;其他各个chiplet也可做算力的弹性补充。

除了芯原拿手的不同处理器IP,相关chiplet最重要的应该就是接口了。“主要是要往可能成为事实标准的接口来靠”,所以芯原做的是UCIe/BoW Compatible PHY,“根据客户需要,将接口移植到不同的工艺节点”。

除了展示图像数据传输芯片MIPI A-PHY的例子,汪志伟也给出了几个芯原在做的die-to-die接口封装类型,涵盖BoW——X16 TX OR RX, 60μm bump间距;UCIe-Standard,X16 TX AND RX,110-130μm bump间距;以及UCIe-Advanced,X64 TX AND RX,25-55μm bump间距。

“我们和业界主要封装厂都有合作”。具体到封装方式,基于BoW接口的扇出型先进封装,也囊括了面板级(panel-level)方案支持,“芯片能做到4倍reticle size尺寸”;UCIe接口标准封装,是基于FCBGA有机封装衬底;UCIe接口先进封装,则是包括扇出与硅interposer的2.5D封装,涵盖FoCoS和CoWoS。

现场除了芯原之外,我们知道硬核IP与芯片设计服务提供商中茵微电子在高速SERDES方面也是相当知名的。刘德启在演讲中说中茵微电子(可能要加上其100%持股的博越微电子)从IP,到设计服务,到chiplet die都有涉足,是“全栈chiplet设计解决方案”。

IP方面,中茵微提供包括HBM2e/3,112G D2D,到UCIe, PCIe Gen 5/6, 32G/64G Serdes等高速IP——“高速互联需要的IP,我们都做出了一些成果”;而设计服务涵盖SoC, ASIC两大业务板块,“从netlist到GDS”;而chiplet die也属于设计和定制化服务,其中涵盖封装测试——这部分亦有IO chiplet与存储chiplet供给。

互联产品自然是这次论坛上中茵微提及的重点。刘德启说chiplet要真正在整个产业内实现互联,树立统一标准的互联,“还有很长的路要走”。所以“在这样die-to-die的战国时代,我们提供完整的解决方案给到客户。”“我们在提供PHY的同时,也提供controller”。他还提到3DIC的复杂性会令die与die之间的互联出现多种问题,“如何键和、走线,有SI/PI的问题、高速互联插损问题等等。”“相比于平面上做112G Serdes, 用于3DIC可能一半速度都跑不到。所以我们有专门支撑3DIC的解决方案。”

有关具体的SERDES IP与存储接口就不做详述了。不过刘德启特别提到中茵微已经在112G PAM4 Serdes与LPDDR5等接口上做到了4nm工艺支持。与此同时中茵微电子“在chiplet领域具备相当的量产经验,涵盖7nm先进工艺产品、超大规模芯片”;也建立起了几个平台:多核异构chiplet平台、2.5D AI芯片平台等。

Chiplet封测:落实到先进封装

郭一帆博士(易卜半导体常务副总)形容chiplet,是将大芯片切成小芯片,然后再封装在一起,相当于“切完了补回去”。其中的“主要挑战是高密度互联”,“如果互联带宽实现SoC内部相似的速度,系统性能也能达到相似的水平”,而且从总体来看“还节省了系统成本”。

而要解决die之间互联带宽的瓶颈,自然关乎互联的具体实施层面了。封测厂对chiplet与先进封装就要看得更具体。我们之前解析过,抛开更传统意义的MCM不谈,一般来说实现高密度互联的2.5D封装有两个大方向,其一是基于interposer中介层——典型如台积电的CoWoS-S,另外一种是硅桥——典型如Intel EMIB,台积电的InFO-LSI。

郭一帆解释说,硅桥“是partial的interposer”,“不是让interposer铺满整个芯片的底面积,而仅占用一部分面积”,成本相对更低。

易卜半导体的chiplet封装解决方案,从介绍来看,主要是RDL First Wafer Level Chiplet(L/S间距规格2/2μm)——RDL First应该是指先构建RDL层,再放芯片;以及RDL First Chiplet with Silicon Bridge——也就是硅桥。郭一帆提到,从成本的角度考虑,很多芯片设计企业还是更倾向于用硅桥的,易卜半导体因此在硅桥技术上花了不少功夫。

所以对于后者,易卜在硅桥+RDL First混合封装上,有自己的核心专利技术,这种封装技术名为COORS-V。据说易卜的这项技术在成本上极具优势。郭一帆也给我们展示了COORS封装的剖面图,以及μBump最小间距, μPad材料, RDL厚度等关键参数。因为数据并不对外分享,在此无法做出呈现。

现场还有一家从事chiplet封测制造的企业:锐杰微。方家恩(锐杰微科技董事长)说锐杰微2021年底就已经在做chiplet产品。所以他分享了好几个chiplet案例,比如说首个应用UCIe标准封装的方案,有10层、12层的不同参考技术方案,锐杰微做出设计优化,“从平行线长度、出线端间距、蛇形绕线增加距、信号之间隔地线、地过孔设计来优化串扰的影响”。

“我们也做了对比方案,基于不同工艺参数、布线方式。”方家恩展示仿真结果,显示“最优方案比常规方案的性能普遍提升”。“锐杰微目前已经成功交付了16X 16Gbps的UCIe IP验证芯片。目前同步在开发32X 24Gbps在2D方案中的实现。是目前已知行业内最早交付,同时能够满足UCIe Spec指标的方案。”

“另外我们也采用其他D2D IP。”方家恩分享了80x80mm尺寸,基板堆叠18层结构的案例,D2D 8Gbps*35bit;及对应的D2D仿真结果,都有比较理想的产出。总的来说,方家恩强调锐杰微“目前已完成数百项FcBGA+SiP\高端核心处理器项目,做到国内首家规模化高端封测一站式解决方案”,实现了“chiplet产品设计仿真全流程,工艺生产全流程”。

另外他还介绍锐杰微的郑州工厂能够完成2.5D工艺全流程,也涵盖设计全流程、设计仿真开发。目前锐杰微的苏州工厂处于在建状态,未来会提供更高的吞吐。

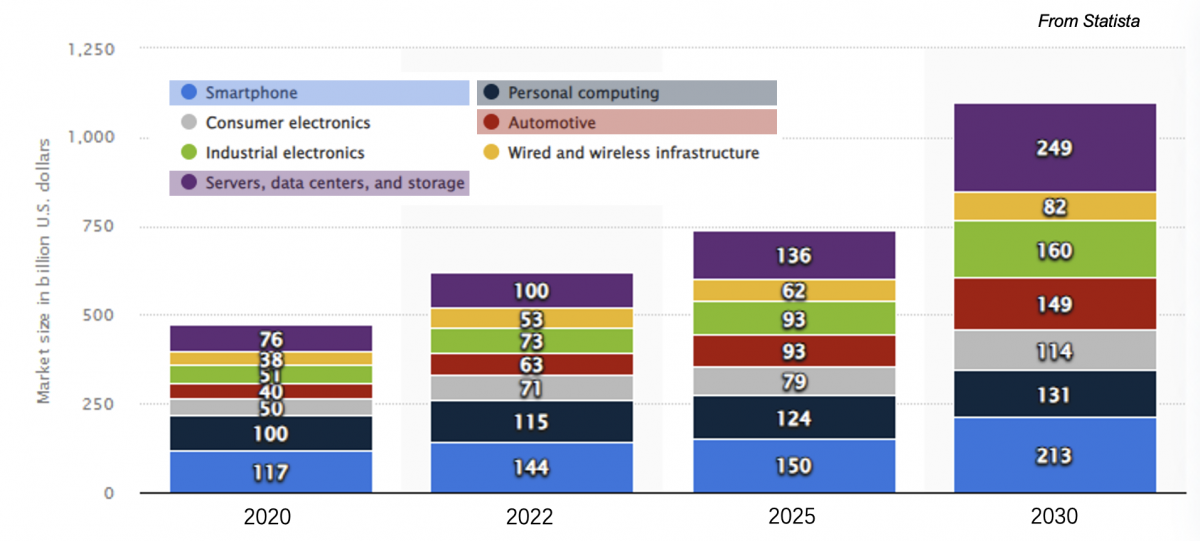

行业普遍认为,半导体产业突破万亿美元规模会在2030年达成。黄晓波在演讲中也援引了这组数据,来自Statista的预测数据是,服务器、数据中心与存储会成为其中的大头——实际上这应当也是chiplet与先进封装应用的主战场。其他几个价值份额占比较大的应用领域还包括手机、个人计算、汽车。似乎现阶段,除了手机以外,其他几个都已经开始用chiplet了。

从去年初生成式AI爆发以后,foundry厂们普遍预期半导体产业破万亿美元规模的估计太过保守。数据中心AI HPC芯片的需求会持续激增,带动周边其他芯片与器件发展,伴随生成式AI算力下沉到边缘和端侧,万亿规模的确是说少了。而这其中的绝大部分高算力芯片,都会是基于chiplet+先进封装。那么现在我们的chiplet探讨真的只是个开始。