EDA是半导体制造的核心基础工具,在大规模芯片设计中扮演着不可或缺的角色。随着半导体技术与应用不断迭代升级,提高IC设计的质量和可靠性至关重要。其中,IC验证已经成为IC设计的瓶颈,而且验证的成本也不断上涨。对此,英诺达(成都)电子科技有限公司副总经理熊文在2024中国IC领袖峰会上特别介绍了静态验证EDA工具在大规模芯片设计上的创新突破。

英诺达(成都)电子科技有限公司副总经理熊文

EDA国产化有挑战,也有机遇

熊文首先分享了EDA国产化存在的挑战与机遇。其中,在行业生态壁垒上,目前全球EDA市场主要面临国际厂商的垄断挑战,三大巨头Synopsys、Cadence、Siemens EDA(被西门子收购)占据75%以上的市场份额。三大巨头通过多年发展以及不断并购,构建了一个完整的产业生态链,对新进的EDA企业树立了非常高的技术壁垒。

在国产替代上,用户永远会选择最有价值的产品,而国产EDA企业需要帮助IC设计公司解决他们在设计中遇到新的问题,加快其产品设计。”这才是设计公司优先考虑的问题,而不是一定会用国产化EDA工具。“在这一点上,熊文强调创造价值才是国产EDA公司安身立命所在。

在行业互动上,国外领先的EDA企业设置的技术壁垒让国内很多设计公司没有太大意愿去尝试国产EDA工具。毕竟,在半导体技术快速迭代升级的背景下,很多设计企业也面临产品问世的时间压力,因而更倾向于采用比较成熟且经过多次验证的EDA工具。对于国产EDA公司来说,如何取得国内用户的信任,让用户使用国产EDA产品也是面临的挑战之一。

在投融资上,最近两年中国在半导体领域的投融资趋势有所放缓,股权投资市场结构正在重塑,使得一些EDA初创企业需要保证如何在艰难环境下不出现金流问题,同时又能获得投资人的青睐。

在同质化竞争上,熊文分享了此前的两组数据:一是全球大概有140家EDA企业,其中有80家在中国;二是全球EDA从业人员56000人,其中有8000人在中国。这不可避免造成了中国的EDA产业同质化竞争非常严重的状况。

不过,熊文也指出,在这些挑战的背后,国产EDA企业也正迎来一些发展机遇。尽管国际EDA巨头树立了很高的产业壁垒,但自从新冠疫情以来全球半导体产业链进入“重构”状态。而且,由于国外技术的限制,一些国内企业已经不能得到国外EDA技术巨头的支持。对很多初创企业而言,抓住这次半导体产业重塑的机会,就能实现快速成长。他也表示,资本永远不会停下脚步,永远会找好的标的。国产EDA企业只有为客户创造价值、为投资人创造价值,才会得到资本市场的青睐。

静态验证在IC设计验证上优势明显

熊文重点介绍了静态验证在IC设计当中的应用。目前EDA项目在IC验证中的成本随着IC制程工艺不断演进不断攀升,同时“2007年以来,单个IC设计项目上所需工程师的峰值增长了50%,然而对应的验证工程师的峰值增长了146%!”这说明IC验证已经成为IC设计的瓶颈。

目前数字IC验证有三种方法:动态仿真、形式化验证、静态验证。其中,动态仿真方法是最早验证方法,其核心是通过向设计提供激励信号并观察其输出响应来验证设计是否满足预期行为的方法。动态仿真可以对行为级/RTL级/门级电路进行仿真,实现电路逻辑功能的验证与调试,但存在两个严重的缺陷:一是软件难以满足越来越复杂的集成电路设计的要求,需要硬件仿真技术来解决;二是测试激励存在人为这一最不可靠的因素,不可能覆盖所有的内容,可能会对流片造成影响。

形式化验证出现弥补了这一缺陷,主要通过数学方程以及模型构建的方式验证整个芯片的功能是否与设计构想一致。尽管形式化验证是比较严谨的验证方式,但其也有两个比较大的缺陷,即由于模型验证存在状态爆炸问题,因此对于数据通路电路和规模较大的电路处理比较困难。

静态验证是三种验证方式中最晚出现的验证方式。熊文介绍,“这种验证方法实际上是基于经验,可以把静态验证看作设计的专家系统。它不是验证功能,而是验证设计里面的代码,相当于有一个专家告诉你写的代码是否符合语法规范,你的代码是否对后续所有的设计比较友好,会给你不断的建议。”

芯片设计规模越来越庞大,查漏补缺的难度越来越高。IBM统计在实现阶段修复一个漏洞或错误的成本是设计阶段的6.5倍,而到了测试阶段,这一成本更是激增至15倍。因此,静态验证是IC设计验证方法之一,是确保高质量设计输出的关键步骤。

相比其他的验证手段,静态验证在以下方面效果显著:一是早期错误检测,可以在开发周期的早期发现和修正错误,减少后期修改的成本和时间;二是成本效益,相比于仿真验证,静态验证通常更加经济,不需要额外的硬件或复杂的测试环境;三是全面性,能够系统地覆盖代码或设计的所有部分,包括在正常测试中可能不会执行到的路径;四是速度快,静态验证可应用在超大规模集成电路上,其并行处理能力可以显著提高验证的速度。

因此,对比三种验证方法,静态验证有其独有优势,比如对算力的要求不高、运行速度快、覆盖全等,但静态验证也存在验证结果噪声问题,需要有经验的工程师。

英诺达自研EDA产品布局

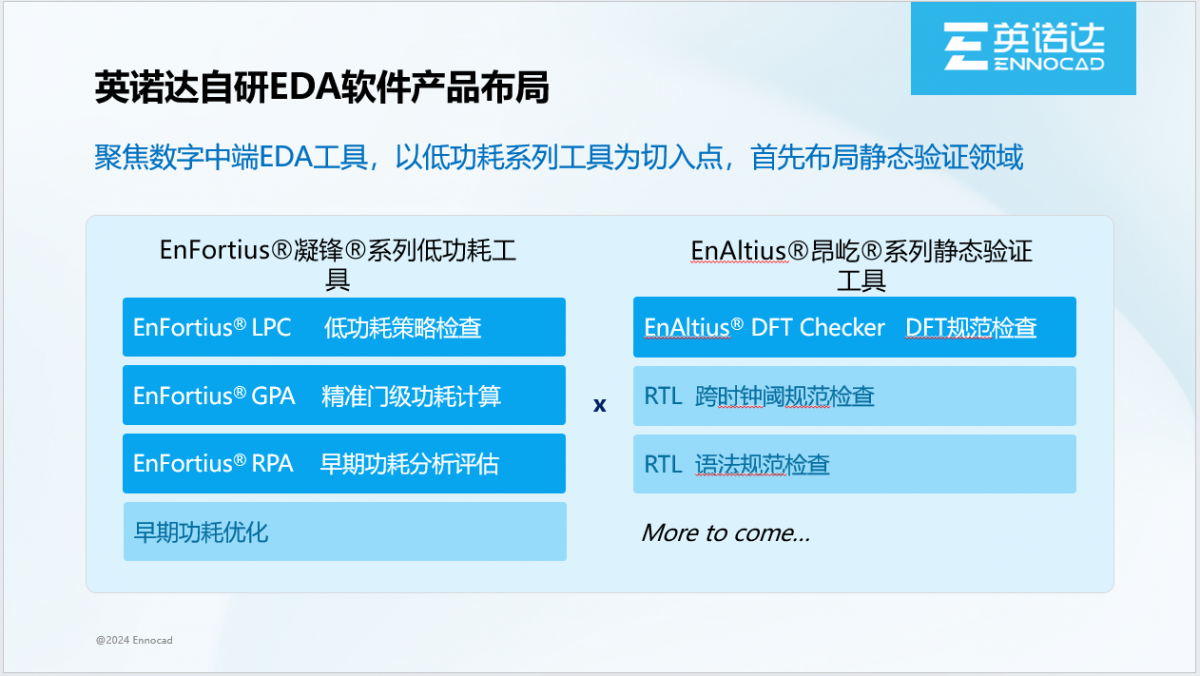

基于对国产EDA整个行业的认知,以及自身的优势,英诺达采取差异化战略布局,聚焦数字中端EDA软件,以低功耗的系列产品作为切入点,布局静态验证领域。目前英诺达也是国内首家静态验证全流程企业。在产品布局上,目前英诺达主要两大系列工具:EnFortius®凝锋®系列低功耗工具和EnAltius®昂屹®系列静态验证工具。

根据相关统计报告,导致流片失败的原因,除了功能性问题之外,时钟和功耗原因位居前列。“这也是为什么英诺达要聚集低功耗工具开发的原因之一。另外,英诺达的技术创始团队在低功耗领域都具有20年以上的经验。”熊文表示。

然而,低功耗设计存在较大的挑战,主要体现在以下几个方面:一是功耗会影响芯片的可靠性和寿命;二是从系统设计,到RTL设计,到物理实现,每一步都需要低功耗设计,但是每一步所采取的低功耗策略是不同的;三是设计需要电源管理技术,也需要更多的电源管理电子单元,比如Iso、level shifter等;四是UPF是描述电源管理意图的标准,但是自推出以来经历了4次大的更新,而不同版本之间的兼容性问题也使该标准成为EDA领域最难支持的标准之一。

那么,为什么要在设计早期就做低功耗的分析呢?熊文表示,IC设计流程早期发现并解决功耗问题是成功流片的重要保障,可以带来两大好处:一是越早介入,优化手段越多,收益越大,长期以来的实践已经证明,在高级抽象级别比在低抽象级别降低功耗更加有效;二是越早介入,能越早反馈,快速迭代,从而节省时间和成本。而英诺达推出的工具可以为RTL代码到最后整个布局布线完成提供很好的低功耗的策略。

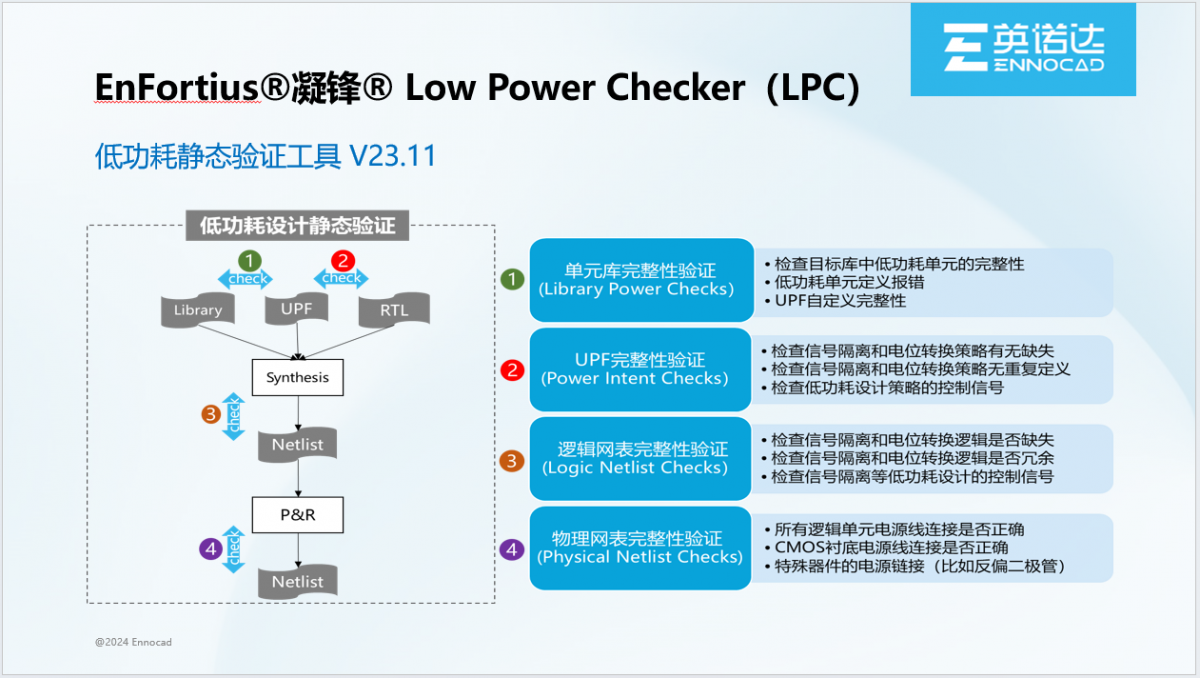

其中,EnFortius®凝锋® Low Power Checker是英诺达于2022年10月推出的一款软件,目前进入商用状态。熊文介绍,这款软件贯穿整个SOC设计流程,可以进行单元库完整性验证、UPF完整性验证、逻辑网表完整性验证、物理网表完整性验证。该软件在过去一年多时间已经在多个客户的真实项目中锤炼,整体性能完全可以对标国际主流厂商,部分性能指标上甚至超越了国际主流的软件。

熊文表示,EnFortius® LPC工具流程其实比较简单、实用、易学,“因为我们借助于软件工程的发展,整个软件开发基于比较先进的软件环境,采取了全Tcl软件环境语言编辑,客户很容易进行设置,同时支持标准的输入文档,全自动低功耗设计检查,还可以全面的分析报告及查错。”

总结起来,EnFortius® LPC技术优势主要体现在三大方面:一是速度快、容量大,150M门的物理网表,2小时完成SoC级检查,全流程不超过6小时;二是支持所有常用的最新UPF命令和语义及常用的UPF 1.0到UPF 3.0版本的命令和语义,满足客户根据自身低功耗设计的需要对UPF使用的要求;三是GUI界面方便用户进行debug。

熊文也特别介绍了英诺达最近几年的发展成绩,“英诺达基于丰富的实际EDA工具开发及管理经验,清晰的战略规划,重点在静态验证产业链进行布局,得到了客户的广泛认可。”英诺达连续3年业务成长,2021-2023营收复合增长率116%,累计客户近20家。