Aart de Geus(Synopsys执行主席兼创始人)在前不久Intel Foundry的活动上说,自1986年创立以来到现在,配合传统摩尔定律,Synopsys让生产力达成了1000万倍的提升。听起来像是自吹自擂吧…

不过他另外提到自1965年Intel创立至今令生产力提升了10亿倍。可能在很多人看来,1000万倍、10亿倍这两个数字是略显夸张的。但前年我们在回顾摩尔定律的文章里举过存储器的例子,很容易得到这么多年来bit成本下降1000万倍的结论——有兴趣的可以去看看。

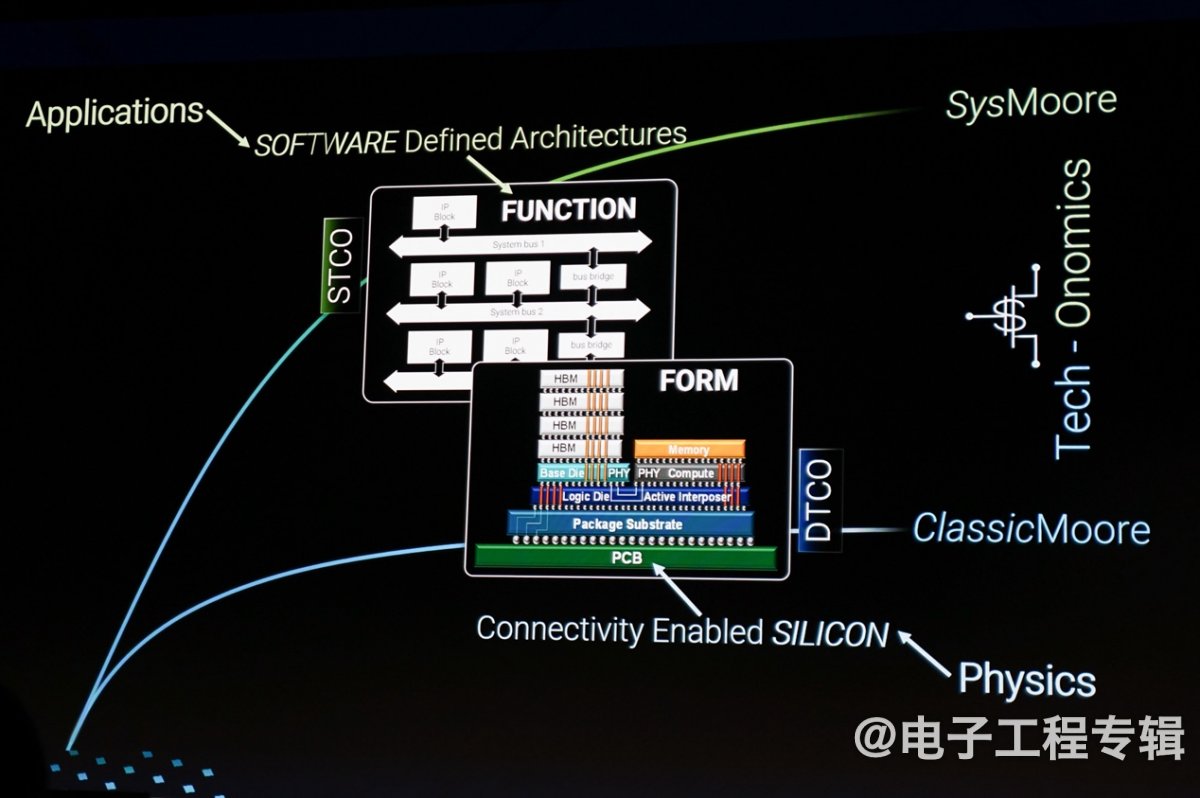

这两年,包括Synopsys在内的很多上游企业都在谈,接下来要驱动芯片性能1000倍提升。这在摩尔定律放缓成为共识的当下真的可能吗?我们总结这些企业预设1000倍性能提升的主要方法囊括3点:(1)应用导向,也就是先关注芯片将来具体用来做什么,并提供一定程度的应用优化;

(2)系统层级,不管是以新思SysMoore为代表的“系统”,还是Intel Foundry的“系统级foundry”的“系统”,都与过去传统的芯片设计不一样;这里的系统可以是指基于chiplet的异构、先进封装,也可以是涵盖更高层级存储、互联的“系统”;用西门子EDA的话来说是“软件定义的、硅赋能的系统设计”(3)AI驱动——主要是指借助AI技术来协助芯片设计。

Intel Foundry的这场活动上,EDA几大家都出动高层站台,多多少少都强调了这几点。这三个方向本来也是几家企业当前市场宣传的重点。本文期望基于这几家EDA企业的表达,来看看现如今的芯片设计走向,以及在Intel Foundry对外提供foundry业务时,其先进制造工艺在EDA工具层面准备程度如何。

3月28-29日,由Aspencore举办的国际集成电路展览会暨研讨会(IIC Shanghai)将在上海召开。作为当代芯片设计的重大热点,chiplet与先进封装是摩尔定律持续发展的关键,与IIC 2024同期举办的Chiplet与先进封装技术研讨会上,包括Cadence在内的EDA, IP, 制造与封测厂将齐聚一堂参与chiplet与先进封装技术的探讨,点击这里参考详情并报名参会。

Intel 18A的工具准备情况

无论如何从“系统”高度来谈芯片设计,最基础的仍然是半导体制造工艺推进。除了Intel在活动上发布的14A工艺,很快Intel Foundry对外提供、即将量产的先进制造工艺就是Intel 18A了。

Pat Gelsinger(Intel首席执行官)在活动上说Intel Foundry的客户现在已经可以开始基于18A做设计。Intel自己已经完成了基于该工艺的Clearwater Forest至强处理器的流片;与此同时微软也说准备基于该工艺设计芯片。

似乎Intel针对18A工艺开设了一场签署NDA协议的闭门会议,谈18A工艺的技术细节与性能表现。我们无缘得见,所以现在对此一无所知。现在所知相关18A工艺的仅有,其一晶体管结构是基于RibbonFET——也就是GAAFET,或者说基于nanosheet;其二供电网络结合了背面供电的PowerVia。这两项技术此前都撰文做过解读。

不过作为对外提供给客户的制造工艺,先期与EDA/IP厂商的配合是必须的。Aart说,Synopsys这边在18A工艺上与Intel合作时,既涉及下层物理相关的DTCO优化——RibbonFET与PowerVia自然是其中重点,也涉及上层软件及整个系统的STCO优化——真的应了“软件定义(software-defined)的、硅赋能(silicon-enabled)的系统设计”这句话。据说当前优化“进展非常好”。

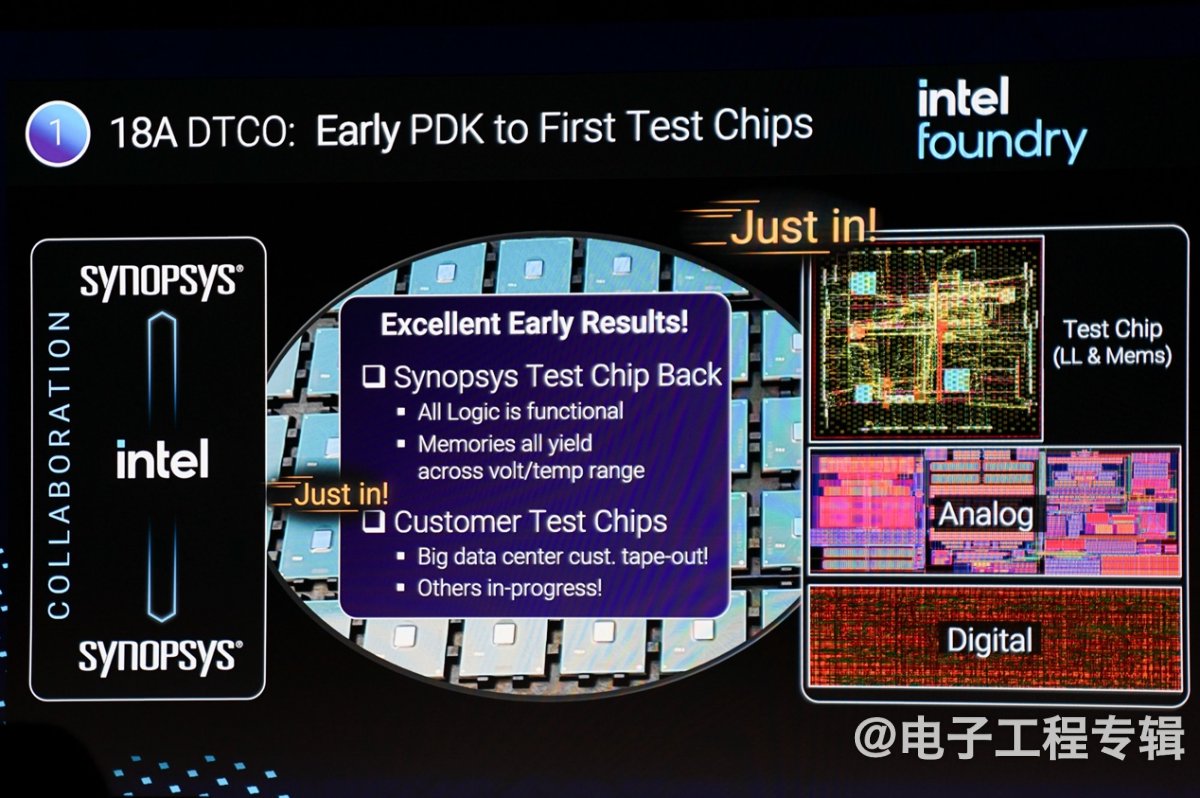

上面这张图给出了Synopsys基于18A的测试芯片情况,“逻辑部分完整功能实现,不同电压、温度范围内的存储部分也表现优秀(yield well)。”不过更值得一提的还是前不久有个据说是“大型数据中心客户”基于Synopsys“完整流程”的流片。

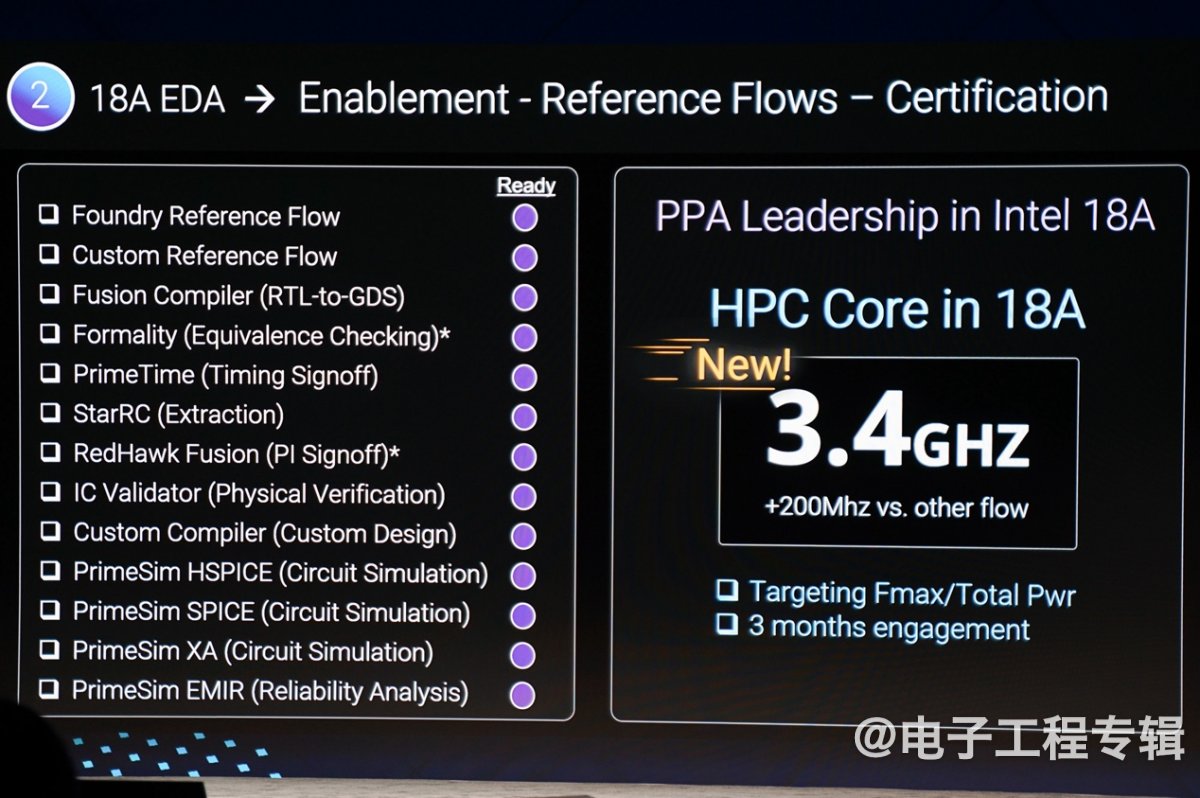

针对18A工艺的EDA三个步骤,enablement(启用), reference flows(参考流), certification(认证)在Synopsys的完成情况如下图。其中涵盖了“大量合作工作”,进展“极好”,“我们一起完成了基于18A工艺的高性能核心”,达成3.4GHz频率。“我认为我们在这项新技术上,正以非常快的速度进步。”

Cadence和西门子EDA也给出了18A工艺的支持配合情况,不过不像Synopsys这么具体,这里不做具体展示。

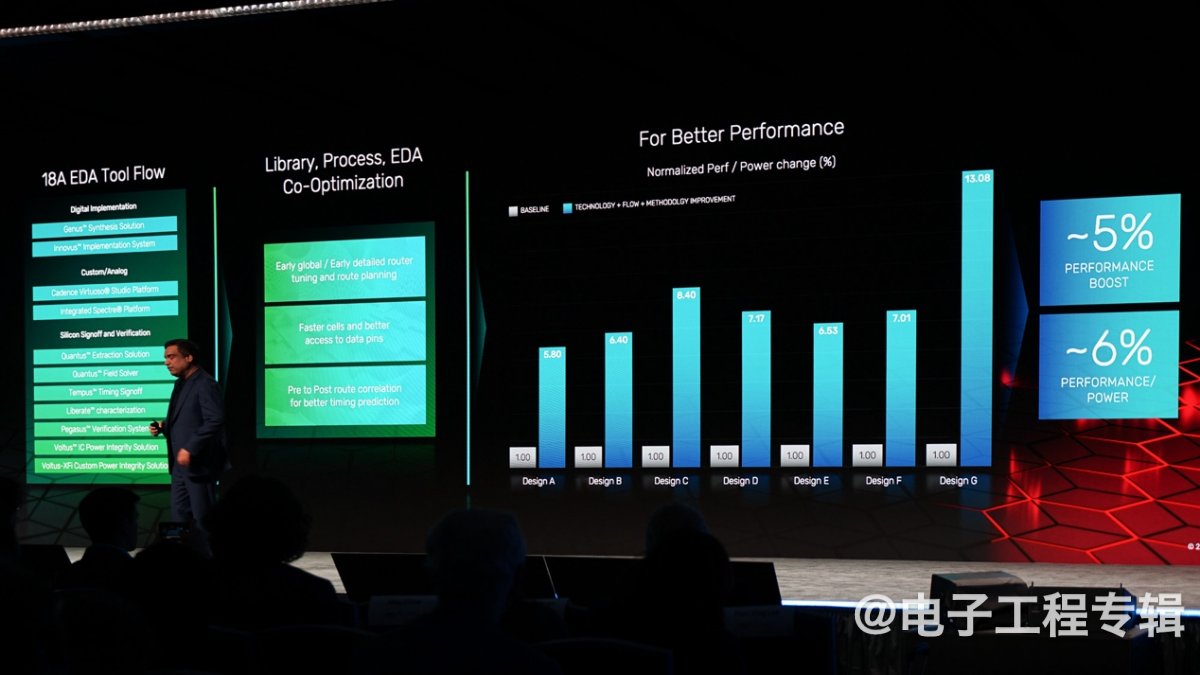

不过Anirudh Devgan(Cadence总裁兼CEO)提到基于Cadence与Intel Foundry在DTCO优化方面的合作,达成性能与能效方面5-6%的提升。“让所有流程可用,并且工具做了认证。而更重要的是协同优化——毕竟这些工具都相当复杂。”具体如下图。举例的系统优化包括布局优化、单元优化,以及时序预测等。

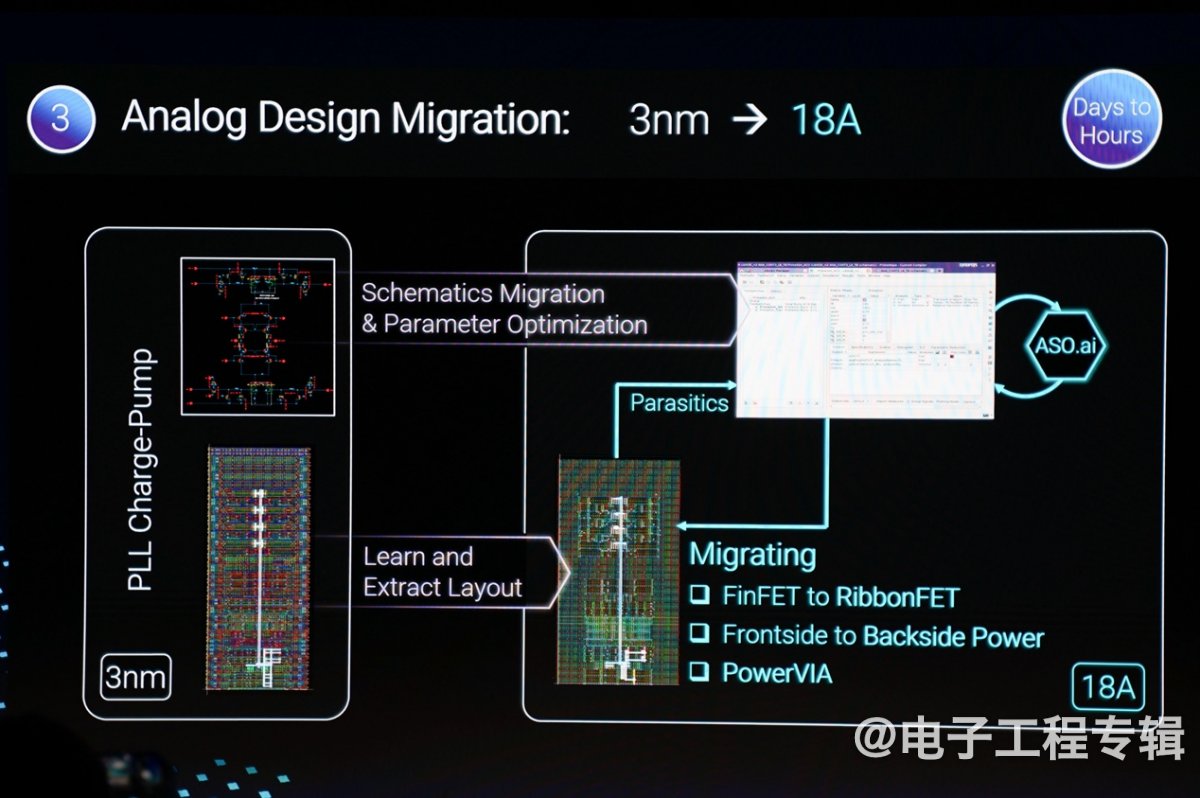

值得一提的是,Synopsys特别提到了设计在制造工艺间的迁移(retargeting),从其他工艺迁往Intel 18A(也可以是相同工艺的设计小改动)。Aart说4、5年前Synopsys就已经在用AI做DSO优化,另外也增加了ASO(analog space optimization)优化支持,“从原节点的原始设计进行学习,把学习所得应用到新工艺上。”

下面这两张图分别是移动处理器核心与模拟的节点迁移示例。其中移动处理器核心,手动方案做节点迁移需要团队数月时间,达成的功耗与性能也并不理想;而基于DSO.ai自动方案,据说可接近于预期结果。“学习的效果很不错,现在更少的尝试(减少10%)就能接近最佳结果。”

模拟节点迁移过程,也是先理解、学习原设计,然后构建数学模型,并进行优化的过程;最终得到ASO优化结果据说也很不错。全过程把时间从“以天计缩短为以小时计”。上面这张图列举的是3nm的PPL Charge-Pump,迁移到18A上;涵盖从FinFET结构器件迁往RibbonFET,以及背后供电的PowerVia等。

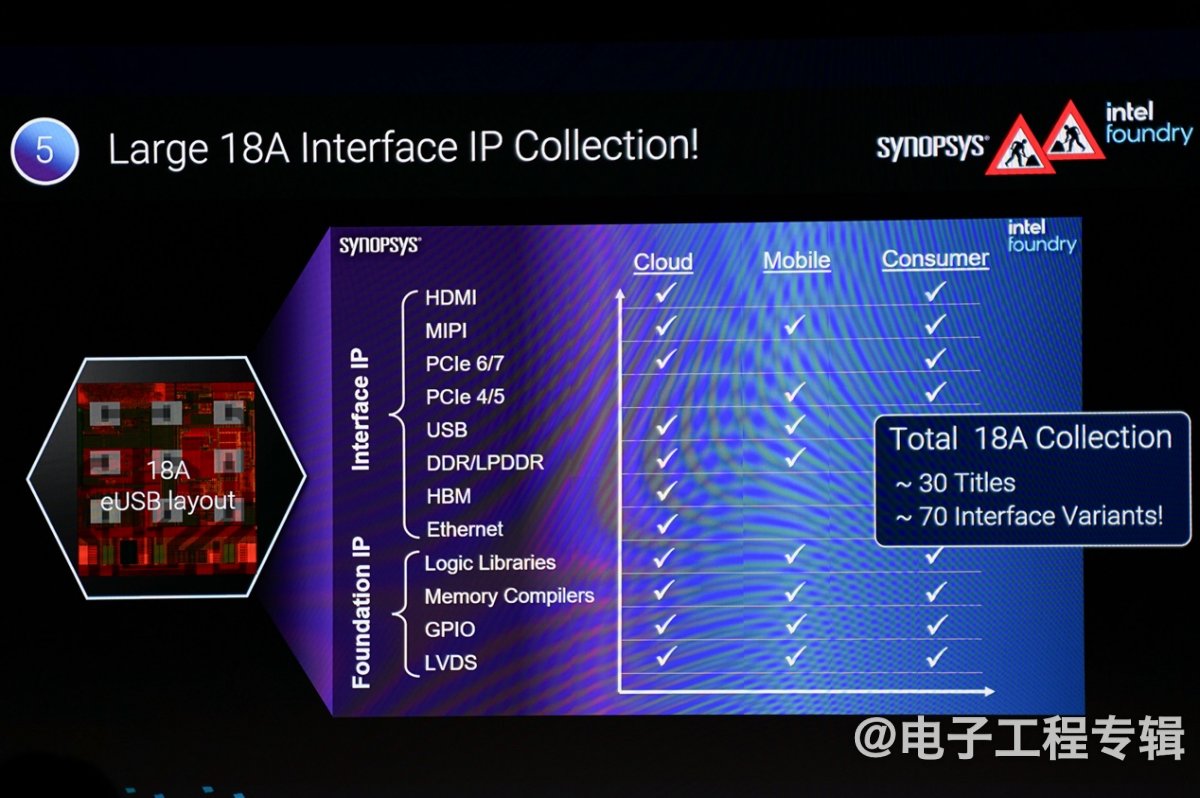

经过寄生参数提取,以及ASO.ai优化,多次迭代以后获得最终结果。虽然Synopsys讲这些大概主要还是为了宣传自家EDA工具,但显然另一方面也是在表达面向18A的这类工具已然准备就绪...另外Synopsys也展示了18A的接口IP集合,如下图——这些当前已经在准备过程中。

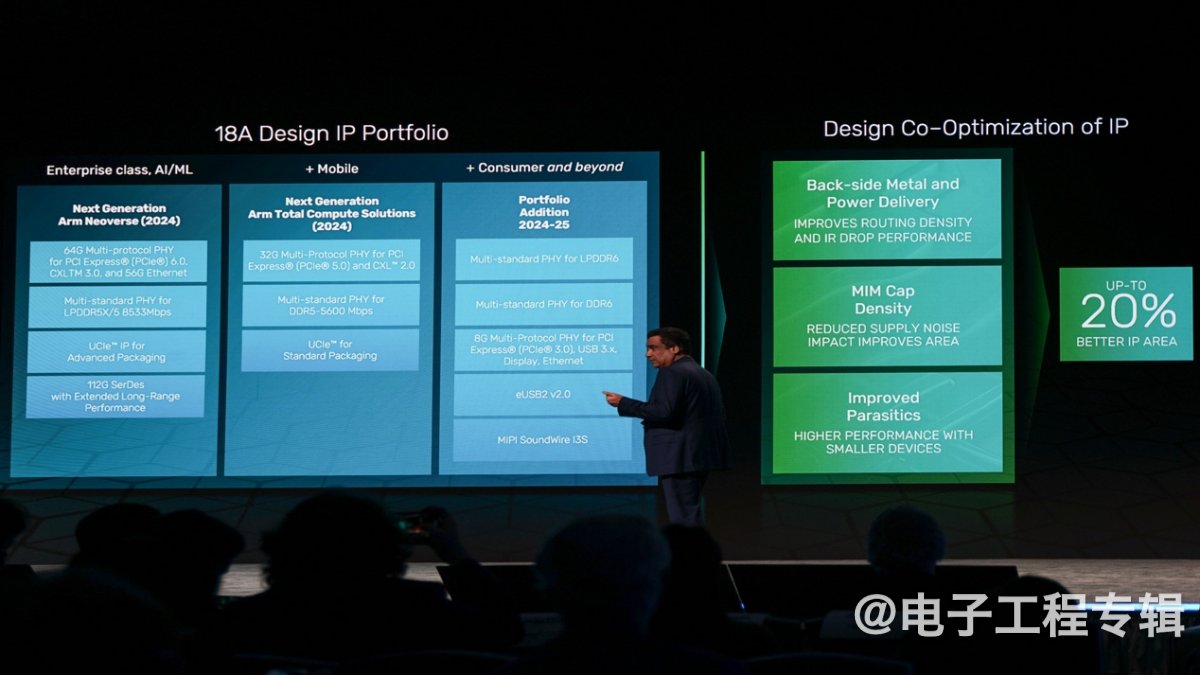

Cadence方面也给出了18A设计接口IP组合,跨不同的应用:包括AI/ML相关的企业级产品Arm Neoverse部分,移动平台Arm TCS,以及更多消费类应用所需。具体如下图。Anirudh特别提到了PowerVia技术,说这项技术有效降低了寄生效应,带来面积红利,也提升了供电质量。

据说在IP设计协同优化后,IR压降实现了最小化,供电电压表现提升5-6%。另外还有此前我们在探讨Intel工艺时就提过的MIM(metal-insulator-metal)电容密度提升,降低供电噪声;外加工艺微缩的整体寄生效应改善,获得最高20%的IP面积红利。

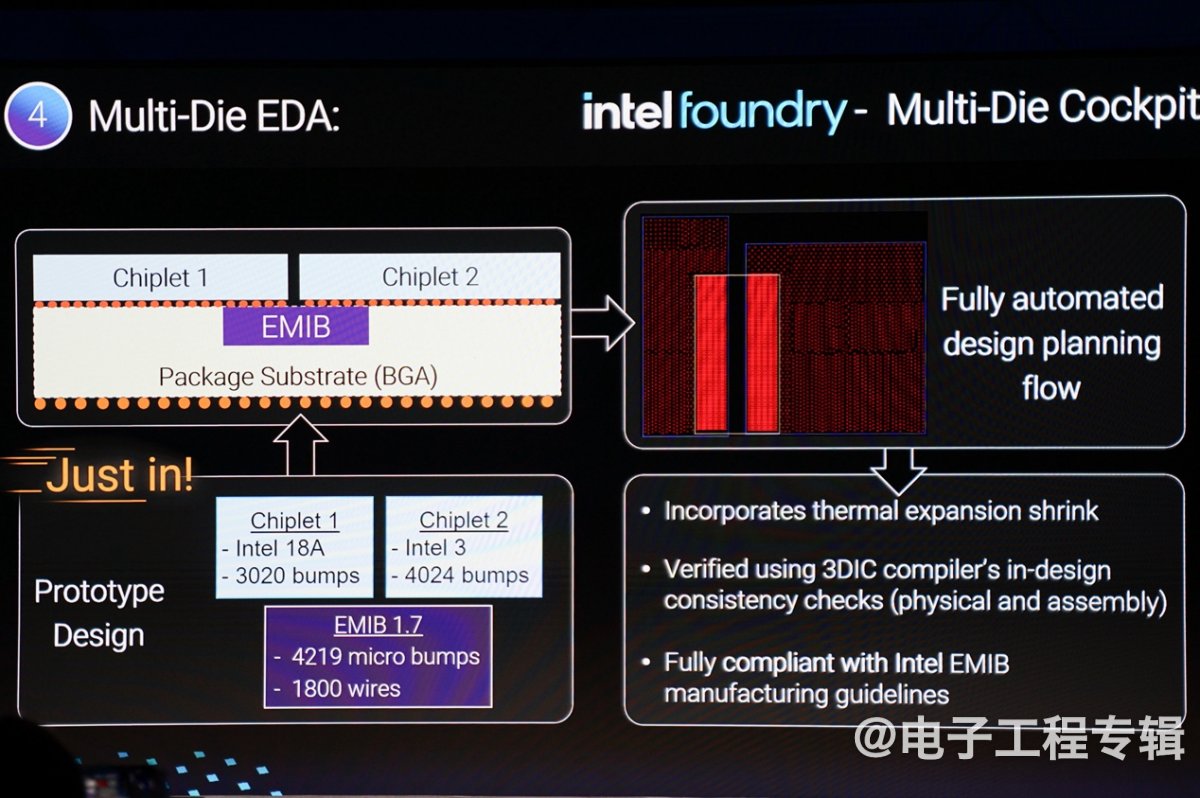

除了这些以外,开始更偏“系统”的设计工具所需就是多die,及涉及到先进封装了。Synopsys展示了基于EMIB硅桥方案,把一片Intel 18A工艺和一片Intel 3工艺的die,基于EMIB连接到一起的原型设计;以及在3D堆叠的方案上,借助背面金属布线(backside metal routing)达成IR电压降与布线资源(routing resource)的权衡优化。

Chiplet、异构集成在Intel Foundry自我定义的概念里,应该是其未来发展的核心之一。

有关3D-IC的几个挑战

显然先进封装方面的合作,是所有发言的EDA企业强调的重点。去年电子工程专辑的封面故事曾经探讨过chiplet与先进封装,导致流程整体“左移”,及芯片设计难度增加的事实。John Lee(Ansys电子、半导体与光学业务副总裁兼总经理)总结3D-IC设计的3大挑战:multi-physics(多物理场)、multi-scale(多尺度)、multi-organizational nature(多团队)。

3月28-29日,由Aspencore举办的国际集成电路展览会暨研讨会(IIC Shanghai)将在上海召开。作为当代芯片设计的重大热点,chiplet与先进封装是摩尔定律持续发展的关键,与IIC 2024同期举办的Chiplet与先进封装技术研讨会上,包括Cadence在内的EDA, IP, 制造与封测厂将齐聚一堂参与chiplet与先进封装技术的探讨,点击这里参考详情并报名参会。

Multi-physics的挑战主要是说,要能够精准模拟多个相互关联的物理现象,比如说功耗、热传导、电路活动等——这些需要作为并行的物理量做仿真。对于3D-IC而言,3D或2.5D堆叠带来的热机械应力(thermo mechanical stress)、翘曲(warpage)等问题都需要考虑,还有interposer(中介)之上,电磁耦合影响数字信号。

这些问题在以前的单die时代是不存在的。比如“对于IC设计者而言,热机械应力可能并不熟悉,但机械设计领域对此应该还是很熟悉的。”

而multi-scale是指不同模块、IP的设计尺度是不同的,比如芯片设计在nm级,interposer和封装设计是毫米级,系统设计是厘米级。需要引入不同的技术方法来处理不同量级的数据;而且需要考虑不同量级的组成部分物理方面的挑战,如热传导在芯片和interposer上的表现就不一样。

最后一个因素主要是跟不同团队合作或者设计流程有关的,以前切分成芯片、封装和系统不同设计团队,对于应对前面提到的这两个挑战就不再适用了。原本明确的分工,在3D-IC时代的界限也变得模糊,或者说几方必须要协作,且原本处于流程后端的人员必须更早甚至全流程参与设计。

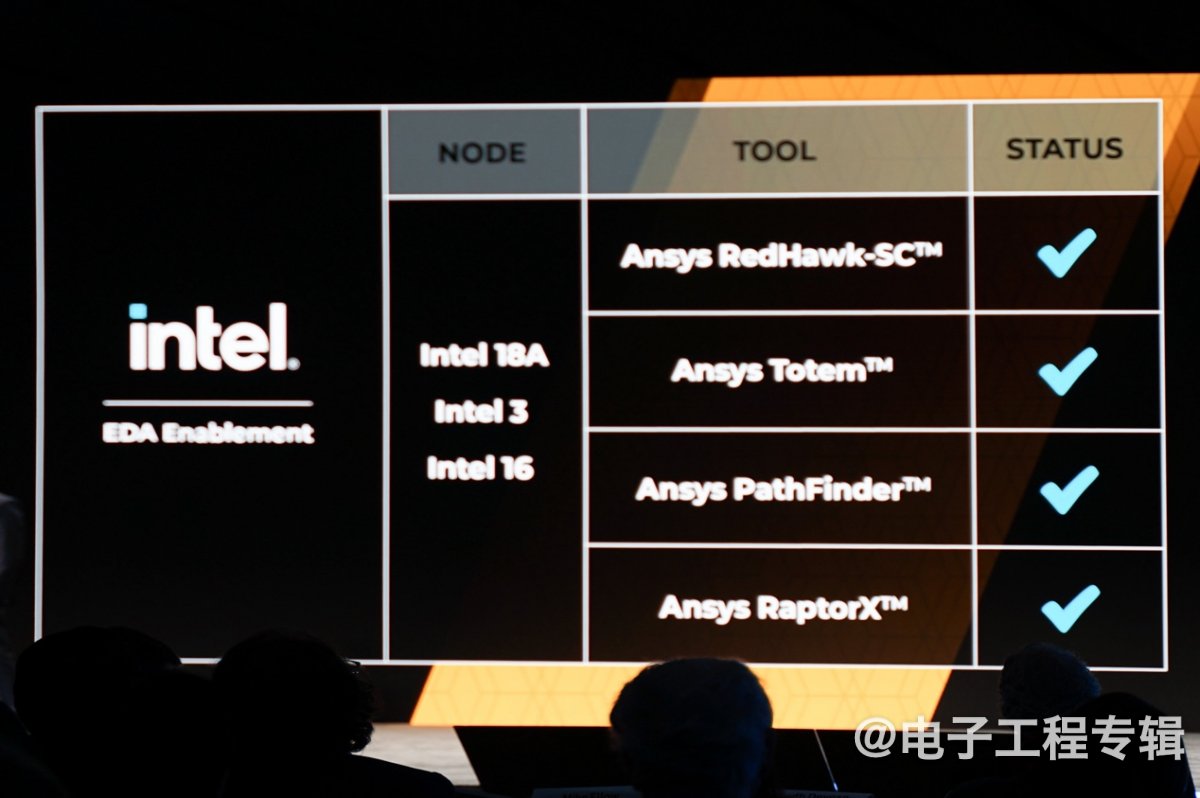

Ansys针对这三大挑战提出的解决方案也是三点:physics(物理), platform(平台)与partnership(合作)。有关“物理”,解决方案显然很大程度来自于EDA/IP这类工具提供者。比如Ansys有针对Intel不同工艺的物理仿真工具,涵盖Intel 18A工艺,并考虑上RibbonFET和背后供电;包括各种模拟仿真,解决信号干扰、完整性等问题。

“平台”与“合作”应当就不需要再多作解释了,其中也涵盖平台支持云、可扩展(西门子EDA也特别提到了云支持,及开放、多供应商环境的生态系统),以及不仅是不同设计团队,而且包括软件供应商、生态合作伙伴组建的完整生态。

对于“合作”,John举的例子是Intel, Synopsys和Ansys三方合作,“将Ansys的压降分析与Synopsys的时序分析结合,Intel获得了更高精度的结果。”还有诸如Ansys RedHawk-SC与Synopsys 3D-IC compiler协作,能够带来优化的多die系统设计。

当然并不只是Ansys与Synopsys,Mike Ellow(西门子数字化工业软件执行副总裁)说,西门子EDA与Intel在先进封装方面的合作积累超过了13年。“我们相信这样的技术不应该只是给有高预算的大型工程团队使用,而是应当让每个过程是都能接触到。”

Cadence的方案名为Integrity 3D-IC,据说基于Intel 18A工艺,2D到3D方案,Cadence已经和Intel进行了Atom核心方面的合作;目前已经流片超过10例。

AI与多方协作的未来

John说Intel Foundry拥抱合作是其能够在竞争中获得优势的关键。实际上,多方合作不止于Intel, Ansys与Synopsys。Anirudh也提到了Arm, Cadence和Intel Foundry的三方协作。“基于Intel 18A,优化的Cadence工具、流程、方法学,呈现面向HPC的新一代Arm Neoverse解决方案。”虽然其实对Intel Foundry而言,面向客户提供foundry服务,这种合作就必然成为常态。

在“合作”与生态养成的问题上,前篇Intel Foundry业务逻辑解读的文章已经谈到了Intel打造“标准”的野心。几家EDA企业也多少都提到了加入UCIe标准等在内的生态。这也算是“合作”的某种体现。

最后单独谈一谈AI。前文已经多有涉及AI技术,比如DSO.ai, ASO.ai,都是很典型的在EDA流程中应用AI。不过Cadence和西门子EDA都将AI作为单独的部分特别谈了谈。Anirudh定义AI就是“计算软件应用到数据上”。“对我来说,推理就是矩阵乘,训练则是迭代的矩阵求解器(iterative matrix solver)。所以其实很多技术在EDA上已经超过20年了。”

他说,“如果你去看EDA行业过去30-40年的发展,会发现我们是很擅长复杂的仿真和优化工作的。”“跑一次(single run)诸如布局布线,给出一个输入,就要跑上1-2天才有输出。”“进行这类工具的多次迭代一般得花上6-12个月,跑了再改,改了再跑。”“在验证等相关设计的各个组成部分都如此。”Anirudh说,“所以我觉得EDA行业一直都没有做好的,就是工作流的自动化。”

“这项工作很难。而现在基于强化学习的进步,最终令其(工作流自动化)成为可能。现在可以做到的就不单是针对单次运行的优化了,而是针对多次运行(multi-run),全工作流的优化。”

“比如说数字设计,做设计的时候肯定不会都只跑一次。有两个大方向的变量,设计变量、工艺选择——包括选何种金属堆栈,架构。这是个非线性的优化空间,人类做得还不错,但人类并不能算是特别擅长这样的工作。可以应用数学方法或者AI来解决问题,那么结果会得到极大程度的改善。”

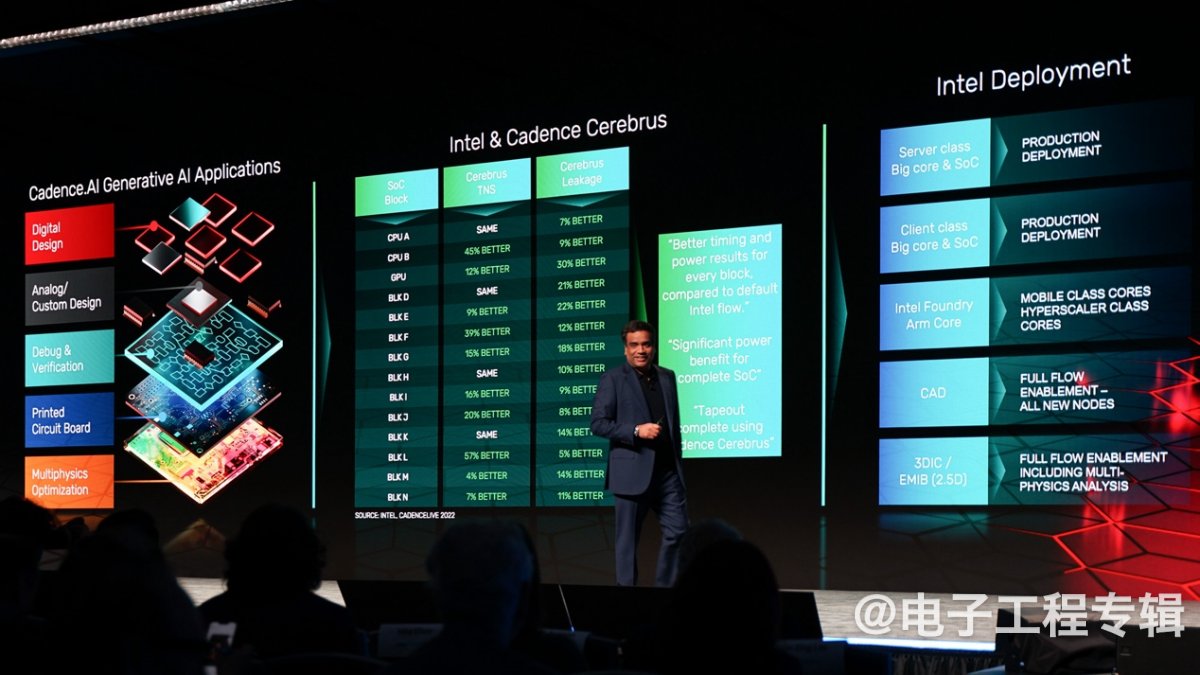

Cadence列举AI工具Cerebrus为不同block带来的优化增益(TNS为Total Negative Slack, Leakage是功耗泄露)

有关AI的“另一个问题是资源和工作”,“芯片上面现在有1000亿晶体管,10年后可能变成1万亿。考虑chiplet、软件,复杂度至少要发生30-50倍提升。”Anirudh谈到,“我们的客户不可能多雇30-50倍的工程师。”这中间的生产力空缺很大一部分是要靠AI填补的。且除了数字设计之外,“对模拟来说,AI特别适用于验证工作。”

Anirudh认为AI的价值不单在生产力上,而是在“所有其他组成部分“,比以前可能做到的最好的设计还要好。“客户要开设包括3nm, 2nm, 18A等在内的工作流,开设各种不同的设计。没有足够的时间和资源来优化每个block的设计是很正常的。AI就能做这样的事。”

“比如用Cerebrus,与Intel一起来提升PPA,效果非常不错。”据说不光是和Intel Foundry在这方面合作,也与Intel Products产品团队有相关合作。

上述信息整体给出的干货可能并不算多,很大程度上也还是EDA企业对自家技术的宣传,不过多少能够表现EDA企业对于Intel Foundry的态度,以及部分反映生态和工具准备情况。

用Aart的话来做结:“90年代末,就有不少人在预测摩尔定律的消亡。”这个时代是“超越了摩尔定律的,是系统层面的摩尔定律:也就是对于终端市场的理解,对于优化的理解——无论是AI、数据管理,还是存储等等。而所有这一切都需要大量的团队合作。”

Intel Foundry的这场Direct Connect活动整体都在不断重复着“系统”“合作”“优化”“AI”等关键词。系统级foundry时代,这些关键词会驱动半导体行业下一个10年的发展。