RISC-V这两年一直都算是半导体领域内的热门话题。其实首个RISC-V芯片的流片是早在2011年的事情,为什么会在十多年后的现在突然变得如此盛行?

此前我们大致分析过RISC-V这些年大热的原因,包括摩尔定律的停滞、加速计算的崛起、应用导向的芯片设计趋势(以及系统企业更多开始涉足芯片设计)、乃至地缘政治和产业链的区域化、自主化,都让RISC-V的开源、灵活等属性能够得到最大程度的发挥,是x86, Arm这类指令集没有也几乎不可能给到的。

换句话说,时代大潮决定了RISC-V的大火——不仅是嵌入式应用,还越来越往HPC方向走。现在的问题并不在于RISC-V是否会崛起,而在于RISC-V的生态发展得有多快。未来5-6年40%年复合增长率;正渗透到HPC领域;以及英伟达、Intel这些传统大咖入局,都能表现RISC-V处于高速发展期的事实。

可能近期对RISC-V而言,一个大事件在于,去年底IP领域内的一名重要参与者开始提供基于RISC-V的CPU设计IP:即新思科技。新思作为EDA企业,提供协助RISC-V指令集芯片设计的工具并不奇怪,不过作为IP供应商推出基于RISC-V的ARC-V处理器IP,至少可以说是RISC-V发展史中的大事件;当然还包括配套的设计工具,以及像TileLink VIP这样的必要组成部分。

因为这家公司在EDA/IP界的分量,和业内已推出基于RISC-V的CPU IP的其他参与者还真的不大一样。借着这个机会,我们来聊聊新思入局RISC-V的可能性与影响。

有关ARC-V,及新思的RISC-V尝试

ARC在处理器IP行业的名声本身就不小,低功耗、高度可配置性、可扩展性是其得以满足应用需求的特点:ARC此前在IoT、嵌入式应用领域相当知名。最早的ARC处理器基于ARCompact指令集,几年前新思为其注入ARCv3开始达成64位支持。

一般ARC产品作为处理器核心设计,客户获取RTL级别的方案,并将其整合到更大的SoC上。ARC生态也历经了过去20+年的发展。

RISC-V先期发展已经达成颇具规模的嵌入式应用外加其灵活性,都与ARC这一路走来的方向显得非常契合。所以新思去年在硅谷举办的RISC-V北美2023大会上发布了ARC-V——看名字就知道是基于RISC-V指令集的ARC产品线延伸。

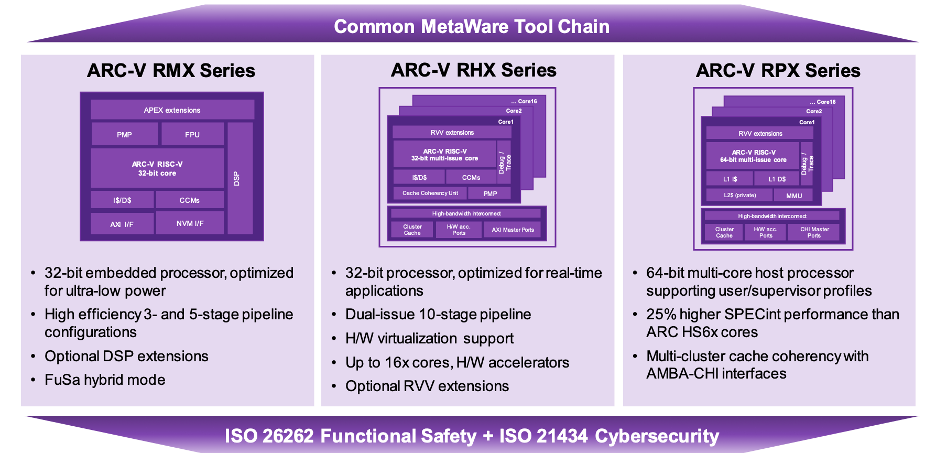

具体到IP产品,现阶段ARC-V涵盖3个家族系列,包括有:32位微控制器平台ARC-V RMX系列、32位支持实时多核的ARC-V RHX、能跑Linux这类操作系统的64位平台ARC-V RPX。前者上市时间预计为今年Q2,后两者则在下半年。

其中ARC-V RMX,3或5级流水线,主要面向低功耗的IoT应用;也有内置的DSP可选,用以支持人脸识别、手势识别之类的特性。值得一提的是RMX设计支持ASIL B和ASIL D安全等级,能够加速ISO 26262和ISO 21434汽车网络安全认证。也就是说RMX是FuSa功能安全支持的。

另外APEX(ARC Processor Extension)为RISC-V设计做出了额外的扩展指令支持——新思也提供定制化的编译器支持。RMX的目标应用典型如电机控制、BLE控制、SD卡等。

实时性能更高的ARC-V RHX,10级双发射流水线,最多支持16个核心。其重要特性包括支持硬件虚拟化、caching和RVV——也就是RISC-V的矢量扩展。更高性能需求的实时应用仍是其应用方向,如汽车、机器人、医疗设备与计算存储的安全管理。

64位多核心支持的ARC-V RPX系列,则基于虚拟化能跑Linux的常见分发版本;基于AMBA-CHI接口能够支持多核心cluster的缓存一致性。这就是个主处理器级别的产品了,面向航空电子、医疗成像、汽车域控制器、存储局域网等应用。

不过从此前新思发布ARC-V时给出的信息来看,无论是上述哪一个,ARC-V面向的就是嵌入式应用,暂时不会与HPC领域内的RISC-V处理器竞争,比如数据中心和手机SoC。

为什么说ARC-V对RISC-V而言,分量不轻

去年新思宣布ARC-V产品时,媒体普遍报道说新思此次是正式进军了RISC-V。实际上新思作为EDA供应商,对RISC-V的支持也应该算得上是由来已久。

尤其考虑到ISA规格定义上,RISC-V对开发者来说有各种选择,而且还可以做ISA扩展、增加定制的指令。灵活性本身就对验证解决方案提出了更高的要求。与此同时,文首提到“应用导向”又是这个时代伴随RISC-V芯片设计的一大特性,则适配不同应用达成对应的PPA平衡,都是EDA工具与方法学需要解决的问题。这对新思而言显然都是主场。

前两年我们就看到了SiFive和新思合作加速SiFive RISC-V处理器SoC的设计和验证工作,还有和Imperas合作解决验证需求问题(更不用说后续新思就收购了Imperas)等等。

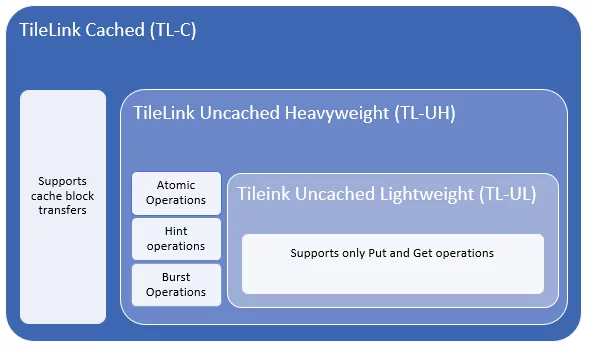

而且对于核心IP的支持也不限于核心自身,还在于核心周围的很多东西,从cache设计到NoC fabric等。比如在ARC-V之外,即便抛开现有ARC家族产品,也有个值得一提的Verification IP for TileLink(TileLink VIP)。TileLink本身是个开放标准的芯片级互联,主要用于RISC-V(也支持其他ISA)。

在诸如SoC这类系统之上,连接加速器、通用多处理器、协处理器、DMA等设计时,实时缓存一致性总线协议就可以选择TileLink。规格介绍中提到TileLink作为一种互联标准,本身有低延迟、高吞吐的特点。其关键特性包括缓存一致性(cache coherent)共享存储,针对SoC提供无死锁(deadlock-freedom)特性(支持DAG,以避免连接拓扑结构中的回路),请求的乱序执行,状态无关(stateless)总线的带宽适应等...

RISC-V SoC就可以用TileLink协议来实施到内存的一致性存储映射访问,算是比较典型的master-slave主从点到点协议。新思的TileLink VIP作为一整套协议、方法、验证相关的方案,主要是加速开发者的验证收敛;支持涵盖TileLink新版本的主要特性,比如TL-UL, TL-UH, TL-C一致性级别、乱序响应等。实现典型如多级缓存+内存的方案,都应当算是现代CPU设计的标配了。

实际作为RISC-V芯片设计EDA工具的组成部分之一,TileLink VIP也只是新思方案中的一个例子。像ARC-V处在ARC产品线之下,本身就表明了对于以往IP技术及其生态的借鉴,毕竟ARC作为既有产品就已经相当成功——再将其与RISC-V本身高速成长的生态接合,这个逻辑就显得相当合情合理。

基于RISC架构核心在硬件指令解码器、流水线执行、大型寄存器堆和load-store等结构方面的相似性,直接用ARC处理器现有的一些机制就能开发ARC-V核心。ARC处理器的现有用户针对新的ARC-V只需要简单重新编译代码。借助共享的Metaware工具链,扩展出对于ARC-V核心的支持,提供编译器、debugger、ISA模拟器开发工具等本身就是一种自有技术与资源的利用。

其他工具方面,前文还提到包括APEX指令集扩展,就有定制化编译器支持;还有ARC-V的处理器IP借助于Synopsys.ai的协助优化;那么对于ARC-V提供一系列工具与技术来加速SoC的设计与验证,涵盖Synopsys.ai, Fusion QuickStart Implementation Kits(QIK), 验证解决方案, 云SaaS平台等也就不意外了。

总结新思提供的RISC-V相关解决方案大方向,除了前述ARC-V处理器IP、TileLink VIP之外;还包括RISC-V设计与实施、RISC-V验证、ASIP Designer支持的定制设计、RTL Architect预测PPA预测RTL变化带来的拥塞影响、各种接口IP、Virtual Prototype、安全解决方案等……这些是ARC生态积累,以及ARC-V IP之外,新思提供RISC-V IP可能对RISC-V世界、对芯片行业产生影响不同于常规参与者的部分。

基于新思整个硅生命周期开发工具的诸多积累,从原型产品到具体实施、验证和流片,乃至到系统、软件开发工具,新思因此与foundry厂及诸多标准组织都有紧密的联系。这对RISC-V IP生态的长期构建都有着相当大的优势。

RISC-V合作与竞争间的差异化

此前新思就表达过,一直在观察RISC-V的发展,在看到客户需求和RISC-V生态强势增长的情况下,就发现是时候进入这一战局了。所以不出意外的新思成为了RISC-V International的Premiere会员。RISC-V International的扩大,吸纳更多的成员和参与者是RISC-V生态得以持续开拓与发展的基础。

但另一方面,更多企业参与生态构建,就商业层面也会事实上形成竞争关系。实际上现在的RISC-V处理器核心IP方面已经有Andes晶心科技, Codasip, Imagination, SiFive, Tenstorrent, Ventana等不同应用方向的参与者。

不过新思去年在发布ARC-V处理器时就提过差异化竞争的问题,即新思在IP领域已经有几十年的经验,IP占到“新思的25%”。

单就IP供应商的身份,新思本身是产品最全的IP供应商,还是顶级接口IP供应商,提供的IP产品包括逻辑库、嵌入式存储、模拟IP、各种有线无线接口IP、安全IP、嵌入式处理器及子系统等等。这对ARC-V这一IP产品的推广也都是优势资源。

所以福布斯去年撰文提及以新思在IP领域的地位,进驻RISC-V称得上是标志性事件。前文有提及新思在SoC及系统设计方面的优势资源让新思在RISC-V IP领域迅速占据一席之地几乎是板上钉钉的。

而且像ARC-V系列产品中还有机会加入不同场景定位的IP,辅以包含TileLink VIP及EDA工具在内的周边加强,新思构建起RISC-V生态的强势在整个行业里可能都会显得格外与众不同。