当前,在3纳米芯片工艺不断导入量产之后,2纳米芯片正成为各大巨头新的角逐高地。

近日,作为移动消费电子领域“最激进”创新应用巨头,苹果被爆料正在设计使用台积电下一代2nm N2工艺的芯片。一张自韩国泄露的有关苹果公司的文件显示以下字样:“TS5nm、TS3nm,正在研究TS2nm”。

实际上,除了台积电之外,三星、英特尔等芯片代工巨头均获得了2纳米芯片订单。整体来看,相对于3纳米芯片工艺,2纳米不仅涌入更多的芯片代工厂商,更多产业链上下游巨头也在加快2纳米芯片技术的布局。

从这一系列有关2纳米芯片工艺的最新动态可以看出,在AI技术不断演进与发展的推动下,2纳米先进芯片工艺的竞争正愈演愈烈。未来,随着良品率、成本以及确保生产的可持续性等问题不断得到解决,2纳米芯片的时代正在加速到来。

巨头纷纷布局2纳米芯片

在过去数十年里,半导体行业“大浪淘沙”,最后成就了台积电、三星这两大先进芯片工艺的主力推动者。

其中,台积电更是先进芯片工艺的引领者。最近几年,台积电更是把大部分资金用于2纳米、3纳米以及更先进工艺技术的研发。

在2纳米芯片产能布局上,目前台积电正在建设两座2nm芯片工厂,位于新竹科学园区的宝山P1晶圆厂将最先量产2nm,最早将于2024年4月开始安装设备;高雄工厂将紧随其后,预估2025年开始生产。此外,台积电第三座2nm厂宝山P2工厂规划,预计将在今年确定。

三星则是第一家开始大规模生产3nm或SF3芯片的企业,也是第一家转向称为Gate-All-Around(GAA)的新型晶体管架构的芯片巨头。尽管三星3纳米良率不尽人意,但其也是2纳米芯片的积极推动者。据悉,三星正在打造一项尖端的SF2 GAAFET工艺,并有意超越其最大的竞争对手——台积电。

而英特尔也在最近的Direct Connect活动上公布了“4年5个工艺节点推进计划”,其中就包括2纳米芯片的发展节点,更是强调了在2030年之前成为全球第2的foundry厂的发展目标。

目前,英特尔已经披露了其在2024年量产20A“2纳米”芯片的计划。这款芯片将采用全新的RibbonFET晶体管,以取代现有的FinFET架构,并带来新的互连创新,如PowerVia技术。从推进时间表来看,英特尔似乎是最先实现2纳米芯片工艺的企业,但其计划也面临着诸多现实挑战。

此外,日本Rapidus公司也计划在2027年开始生产2纳米芯片,加入与台积电、三星电子等芯片代工大厂竞争中。尽管这家企业缺乏台积电、三星那样深厚的先进芯片生产的造诣,但在日本政府的推动下,已经从应用工艺研究到先进芯片制造各个环节,引入了越来越多的“支援者”,比如IBM、比利时研究机构IMEC等。

2纳米芯片技术储备不断完善

目前,整个产业链的技术储备也正在不断完善,从设备制造商、材料供应商到芯片设计公司,整个半导体行业都在积极应对这一技术变革,以确保在2纳米芯片时代能够保持竞争力。

其中,光刻机是重要的一环。2023年12月,全球最大的光刻机厂商ASML透露,已开始向美国英特尔公司,交付最新一代“0.55数值孔径”EUV光刻工具,将用于2nm制程工艺芯片生产。

据悉,ASML计划将在2024年生产10台2nm EUV光刻机,其中6台已被英特尔预定。尽管英特尔在先进芯片工艺上要“略输”台积电、三星,但其获得最多2nm EUV光刻机,也为未来先进芯片工艺竞争带来更多的不确定性。

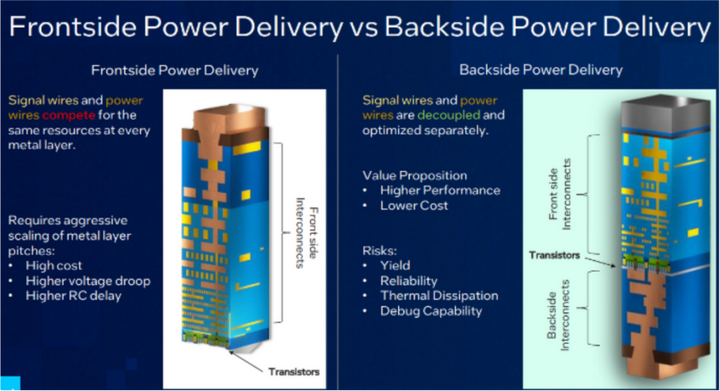

图 1:背面供电减少了电压下降和 RC 延迟,但需要更长时间处理。来源:英特尔

同时,被指为实现2纳米芯片工艺的关键技术——“背面供电(BSPDN)”技术最近也取得了进展。近日,有韩国媒体报道,已确认三星电子正在开发的背面供电(BSPDN)技术已经获得新突破,且将提前应用于2025年2nm芯片工艺中。

英特尔也在积极研发背面供电技术,以恢复其在制程技术领域的领导地位。据悉,该公司计划将PowerVia与20A节点(2纳米)的RibbonFET(全方位栅极)晶体管结合使用。通过采用BPD,设备实现了6%的性能提升(Fmax)、90%的单元利用率以及30%以上的降低电压降。

台积电在此前法说会上也透露,在N2研发出背面配电线路(backside power rail)解决方案,此设计最适于高性能计算(HPC)相关应用。在基线技术之上,背面线路将使速度提升10%至12%,逻辑密度提升10%至15%。

另外,在晶体管架构上,最近有供应链消息称,台积电将如期采用GAA(全栅极环绕)技术来生产2nm制程节点,位于新竹科学园区的宝山P1晶圆厂,最早将于4月份开始安装设备,P2工厂和高雄工厂将于2025年开始生产采用GAA技术的2nm制程芯片。

2nm芯片订单抢夺战正式开启

随着半导体技术的不断进步,芯片工艺制程即将进入一个新的里程碑——2纳米。相比于之前的制程,2纳米芯片可以提供更高的性能和更低的功耗,为未来的电子设备带来更加出色的性能和能效。然而,2纳米芯片成本非常高。

此前,International Business Strategies分析师发布报告,称制造商过渡到2nm工艺后,相比3nm工艺其成本增加50%,导致每片2nm晶圆的成本为3万美元。晶圆厂增加的成本,主要原因是EUV光刻工具数量的增加,大幅提高了每片晶圆和每块芯片的成本,而这些成本自然地会转嫁给消费者。

不过,相对3纳米芯片量产时缺乏订单的窘况,2纳米芯片下游应用需求似乎要明朗很多。据悉,台积电已经向苹果和英伟达等大客户展示了N2原型的制程工艺测试结果。而三星也不甘示弱,通过推出2nm原型以及开出折扣价,以吸引英伟达等客户。高通已计划下一代高端手机芯片采用三星SF2(2nm)制程生产。

毫无疑问,苹果是2纳米芯片工艺绝对的“拥趸“。业界甚至预计,苹果公司将独占台积电2nm产能,有望于2025年下半年投产。与3nm工艺相比,2nm预计可实现相同功耗下,性能10%~15%的提升,或者相同运算速度下,减少25%~30%的功耗。

最近,三星2纳米芯片也迎来了好消息,赢得了日本AI巨头Preferred Networks Inc.(PFN)的首个2nm工艺AI加速器芯片生产订单。该订单还包括配套的HBM内存和高级封装服务。

而作为矢志进入芯片代工领域的英特尔近日也公布了4年5个工艺节点推进计划,不仅有Arm为其先进芯片工艺站台,更有微软送上Intel 18A工艺订单。

值得一提的是,即使日本Rapidus公司也获得了2纳米芯片订单。日本政府支持的半导体研究小组将与美国初创公司Tenstorrent Inc.合作,在半导体行业传奇人物、“晶片大神”Jim Keller的帮助下设计其首款先进的人工智能芯片。而这些AI芯片将由日本Rapidus公司生产。