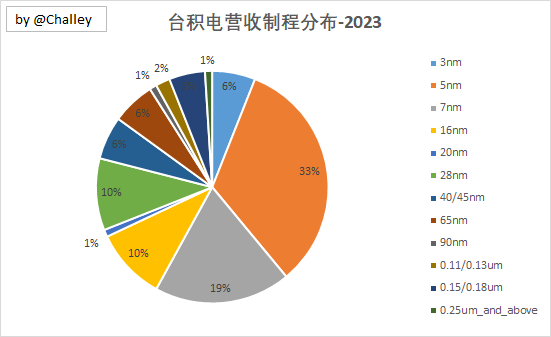

台积电最近公布了2023年12月和Q4的业绩,2023全年业绩也就清晰了(详情请看:《台积电五年业绩分析:台积电法说会,半导体晴雨表》)。根据台积电的报告,其3nm晶圆在第三季度和第四季度的营收总和已经占到了全年营收的6%。

而据最新报道,三星的第二代3nm还在试运行,或许还要六个月才能实现正常良率(60%)的量产。因此,三星的3nm可能比台积电要晚整整一年。

有内部消息指出,三星的第二代 3 nm工艺原型正在试运行。三星和台积电正在争夺即将量产的第二代 3nm GAA(Gate-All-Around)工艺的主导权,三星将以此争取潜在客户。

"目前正在测试芯片的性能和可靠性,三星的目标是在未来 6 个月内实现 3 nm第二代工艺 60% 以上的良品率,这也是公司内部设定的目标"。报道提到,要吸引英伟达(NVIDIA)、高通(Qualcomm)和 AMD 等知名客户离开台积电,三星还需要付出很大的努力。

三星正在确保内部使用的首批产品第二代 3 纳米工艺与即将推出的应用处理器(AP)有关,这个面向可穿戴设备的单元预计将用在第七代 Galaxy 手表上。

根据第二代 SF3 在 Galaxy Watch 7 型号中的表现,该生产节点可能会获得公司 LSI 部门的认可,作为其 Exynos 2500 移动 SoC 的技术基础。这款即将推出的基于 ARM 的处理器将在 2025 年的 Galaxy S25 智能手机系列中首次亮相。

据称,高通公司(Qualcomm)是该公司的主要目标客户,但要想从台积电的主导地位中夺回这家无晶圆厂制造商的份额并不容易。三星的 Galaxy S24系列也将采用台积电 N4P 4 纳米工艺制造的骁龙 8 Gen 3 芯片。

三星第一代3nm

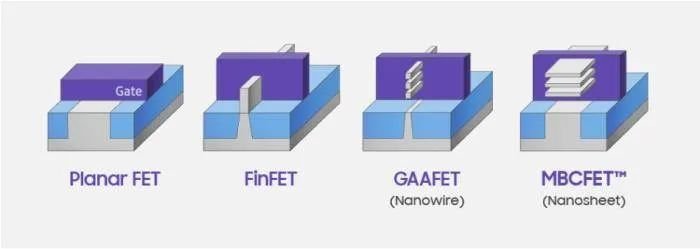

2022年6月底,三星发布了第一代3nm工艺,采用了当时最先进的GAA晶体管技术,算是实现了自己2022年上半年量产的承诺。

三星宣布开始量产的3nm采用全环绕栅极(Gate-All-Around,简称GAA,而台积电当时使用的是4纳米工艺(鳍式场效应管,FinFET),第一代3nm(N3)预计在2022年下半年量产,三星似乎在3nm工艺节点上超过台积电。因此三星算是提前台积电半年量产,实现了领先。

三星表示与5纳米工艺(三星5nm)相比,第一代3nm芯片可以降低45%功耗、性能提升23%、芯片面积减少16%。同时由于采用了GAA晶体管技术,所以栅极电压降低了,漏电流减少了,功耗低了。然而,业界没有看到任何一颗量产的3nm芯片推出。或许第一代3nm由于良率问题,又或是由于工业技术的争议问题,最终没有正视量产。

三星第二代3nm

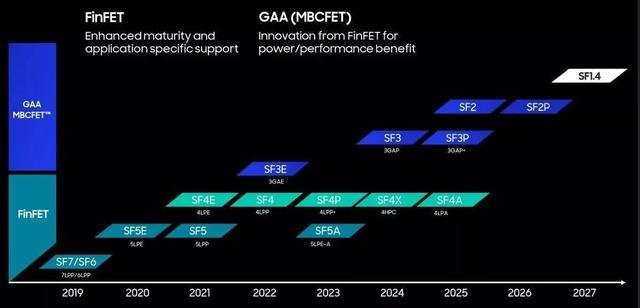

2023年11月,三星电子向投资者透露,将过渡和推进光刻技术,计划 2024 年下半年向市场推出采用第二代 3nm 工艺技术(SF3)以及量产版 4nm 工艺(SF4X)的产品。声明写道:“我们计划今年下半年启动第二代 3nm 工艺、以及用于 HPC 的第 4 代 4nm 工艺的量产,进一步增强我们的技术竞争力。”

三星公布的第二代3纳米工艺,芯片功耗降低50%、性能提升30%、芯片面积减少35%。其第一代3nm工艺(3GAE)晶体管密度大约为150.6MTr/mm2,第二代3nm工艺(3GAP)晶体管密度大约为194.6MTr/mm2。

不过,台积电官方介绍:相较于N5制程技术,N3制程技术的逻辑密度将增加约70%,在相同功耗下频率提升10-15%、或者相同频率下功耗降低25-30%。台积电3nm工艺(N3)晶体管密度大约为294.3MTr/mm2。

因此,台积电3nm工艺的晶体管密度还是要大于三星第二代3nm工艺。

不过,三星声称,SF3 将提供更大的设计多功能性,可以在相同的单元类型中,为不同的全栅极 (GAA) 晶体管提供不同的纳米片通道宽度。

尽管三星没有直接比较 SF3 和 SF3E,但三星表示 SF3 比 SF4(4LPP、4nm 级、低功耗)有重大改进:包括在相同功率和复杂性下性能提高 22%,或者在相同频率和晶体管数量下功耗降低 34%,以及逻辑面积减少 21%。

同时,三星还计划于 2025-2026 年开始推出其 2 nm制程工艺。

小结

而今,三星3nm即将在2024年实现量产,尽管晶体管密度要小于台积电,但三星的良率如果能提高,其性价比也将提升,同时,三星自己可以消化一部分,其综合成本相对于台积电来说要更低,对于非高端制程来说,三星是芯片厂商的另一个选择。

三星与台积电的制程之争将再次激烈展开,三星要想胜出,或许在下一个战场节点:2nm甚至更低才有可能。