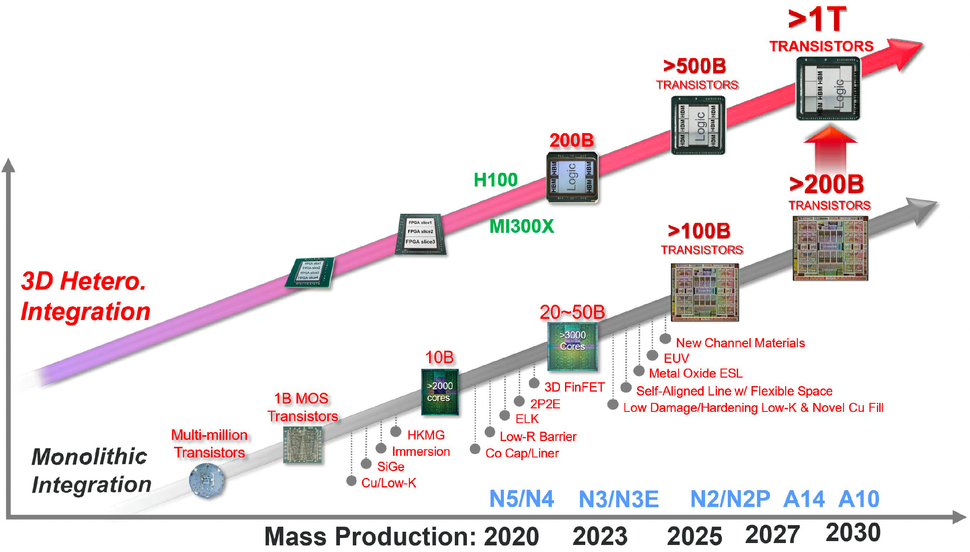

尽管摩尔定律已经放缓,但业界对先进芯片工艺追求永不停歇,即使在1nm这一极限工艺级别上。近日,台积电在2023年IEEE国际电子元件会议(IEDM)上,发布了进军至1nm制程的产品规划蓝图。据外媒Tomshardware报道,台积电计划在2023年推出1nm级的A10制程,实现单个芯片上集成200亿个晶体管,并依托于先进封装技术,实现单个封装上集成1万亿个晶体管的目标。

根据台积电的计划,首先会在2025年量产2nm级的N2制程,2026年左右量产N2P制程,届时将会采用新的通道材料、EUV、金属氧化物ESL、自对齐线w / Flexible Space、低损伤/硬化Low-K & 新型铜填充等技术,将实现单颗芯片集成超过1000亿个晶体管,同时借助先进的3D封装技术,实现单个封装集成超过5000个晶体管。

在2027年之后,台积电还将量产1.4nm级的A14制程,2030年将量产1nm级的A10制程,实现单芯片集成超过2000亿个晶体管,借助3D封装技术,实现单个封装内集成超过1万亿个晶体管。

毫无疑问,实现1nm芯片并不容易。虽然产业界以及各大科研机构均在1nm芯片工艺上作了诸多技术研究,但从技术的角度来看,制造1nm芯片仍将面临非常大的技术门槛。其中,量子隧穿现象是其中之一,因为当尺寸缩小到1纳米时,电子会发生量子隧穿现象,这会导致晶体管的性能受到限制。同时,这一工艺级别芯片的制造过程还会面临更多的工艺控制和材料选择挑战。此外,还需投入大量的研发资源和资金来支持这一芯片工艺的研发。

不过,台积电一直在积极推进1nm制程工艺,而且已在谋划1nm制程工艺工厂的建设事宜,以便按计划量产。今年6月,在公布其与美国麻省理工学院(MIT)和国立台湾大学(NTU)合作的结果后,台积电据传正计划在桃园打造1nm晶圆厂。此前EDN美国版报道称,新的1nm芯片生产设施将落脚桃园龙潭科学园区,而台积电至今已在该科学园区经营两座半导体封测厂。

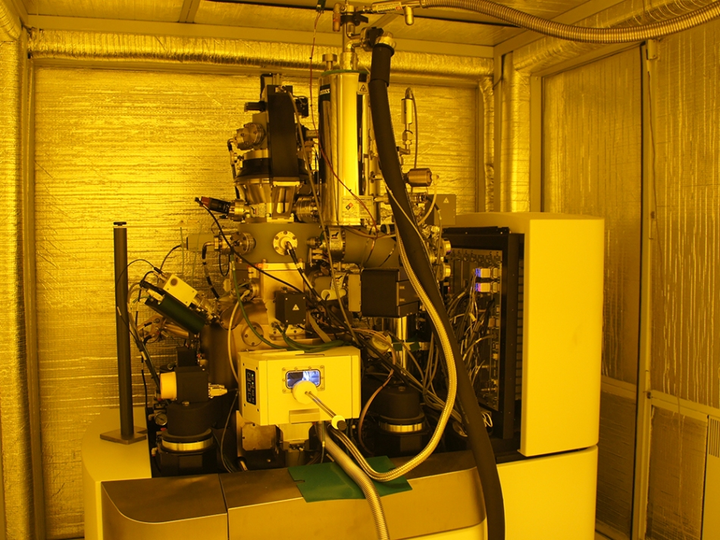

MIT、台湾大学和台积电的研究人员发现,2D材料与半金属铋(Bi)相结合可达到极低的电阻,克服实现1nm芯片的挑战。(图源:NTU)

据悉,在MIT、台湾大学和台积电共同发表的研究论文中描述了由金属诱导导电间隙而引发的制造挑战,以及单层技术如何受到这些金属诱导间隙的影响。此外,文中并建议采用后过渡金属铋和半导体单层过渡金属二硫属化物以缩减间隙的尺寸,从而生产出比以往更小尺寸的2D晶体管。

这项突破涉及一系列新材料,使其可在芯片中创建单层或2D晶体管,从而透过与层数匹配的因子来微缩整体密度。台积电和MIT的团队已经采用包括二硫化钼(MoS2)、二硫化钨(WS2)和二硒化钨(WSe2)等各种现有半导体材料,展现其所实现的低触点电阻。

总之,使用非晶硅材料有助于实现非常小的晶体管——小至1nm。然而,正如台积电研究人员坦言,在未来几年内还不太可能导入使用于1nm制程节点。然而,为了实现1nm制程几何结构寻找合适晶体管结构与材料的任务本身已是一项令人振奋的进展。

当然,“觊觎”1nm芯片的也不仅台积电,一些芯片企业和科研机构也在积极布局。比如,在2022年末的IEDM会议上,IBM就展示了其为通向1nm及以上准备的技术:互连3.0和VTFET。

今年5月,Imec公布了1nm以下晶体管的路线图,在其路线图中1nm等于10埃。随后,Imec更是表示其与ASML签署了一项重要协议,与ASML共同合作开发1nm以下芯片。ASML将提供最新型号 0.55 NA EUV、2nm 和 1nm 工艺开发关键的 TWINSCAN EXE:5200,以及最新型号 0.33 NA EUV TWINSCAN NXE:3800。

今年11月,日本芯片制造商Rapidus、东京大学也宣布与法国半导体研究机构Leti合作,共同开发电路线宽为1nm级的新一代半导体设计的基础技术。