现在还在从事尖端与先进制造工艺的半导体fab和foundry厂,总是喜欢对外宣传摩尔定律还在推进——毕竟时代大潮唱衰摩尔定律的声音越来越多。其中一种宣传摩尔定律运转良好的方式,是前瞻性或未来向技术成果展示——以此表明半导体技术的未来仍旧一片光明。比如Intel每年在IEDM(IEEE International Electron Devices Meeting)顶会上的技术研究成果公布,去年我们就报道过。

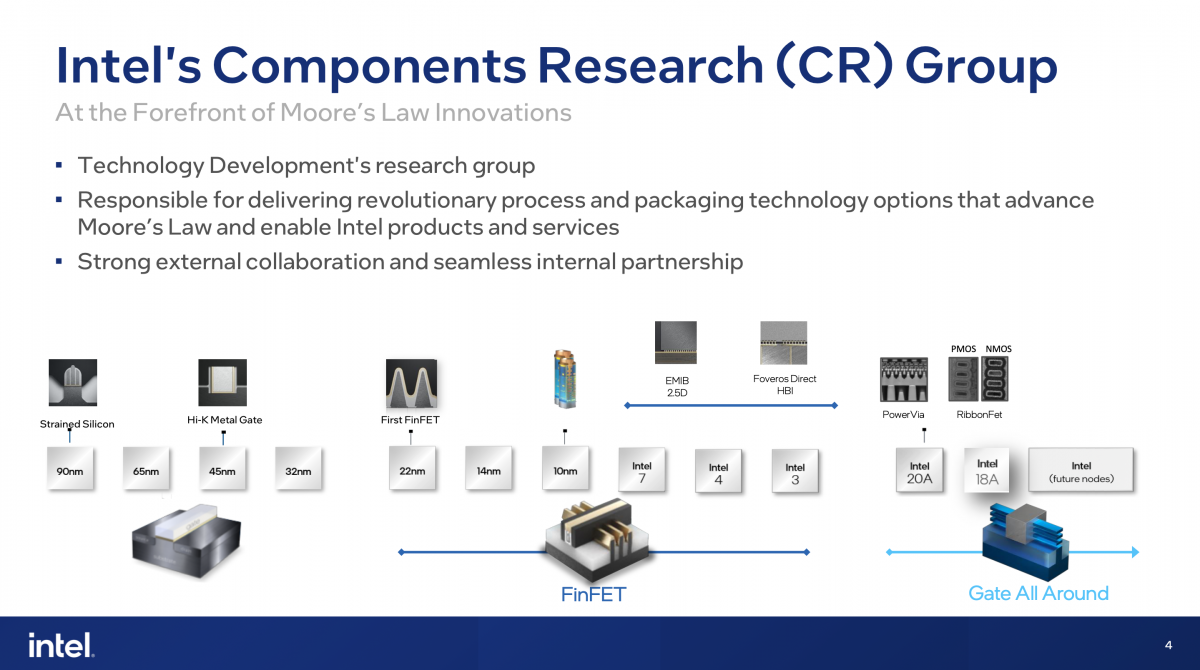

Intel技术开发部门里面有个Components Research团队——Intel方面的说法是,他们为技术研发团队提供“选项菜单(full menu of options)”,以定义未来的fab制造工艺、封装潜在技术。换句话说Components Research探索那些可能有潜在价值的技术,然后通过多方合作(包括材料装备与解决方案供应商、技术联盟、政府与研究机构等),去研究和发现达成这些技术的路径,甚至做出原型prototype。

其中的很多技术也未必会走向最终的产品化。不过在我们的理解里,Components Research的研究成果也并不完全是实验室性质或停留在科研阶段,而是更大程度具备了产品化可能性、偏近未来的技术。如果你关注半导体制造技术,那么一定听过好些走出了Components Research、实现了产品化的技术,比如说应变硅、high-k金属栅(metal gate)、FinFET,这些都是半导体制造历史上的关键技术;

还有像是比较近代的EMIB、Foveros Direct封装,以及近两年讨论度很高、很快要在Intel 20A工艺走向产品化的PowerVia芯片背面供电技术,和RibbonFET晶体管结构——也就是Intel版本的GAAFET。后面这几项我们过去都有详细撰文谈到过。

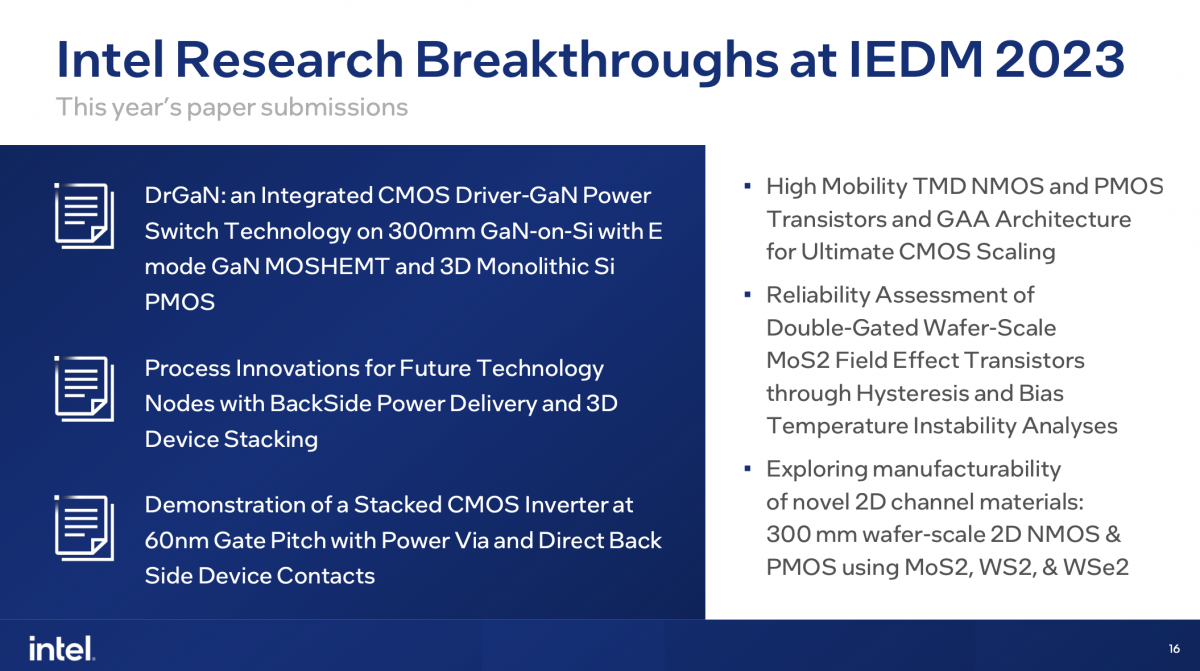

今年的IEDM上,Intel公布来自Components Research的几个在制造和封装领域可能有机会产品化的技术成果,宣传时的主题仍然是“Intel研究实现摩尔定律的创新”,表明推进摩尔定律的器件缩放、单位面积器件数量增长还在持续,同时有器件结构、应用材料和先进封装方面的进步。

今年公布成果的亮点有几个,其一是3D堆叠CMOS晶体管——也就是过去我们常说的CFET,并且以3D堆叠晶体管为基础,去做backside power delivery network背面供电网络(以下简称BSPDN);其二是BSPDN不光可以用PowerVia做垂直互联,现在还出现了一种名为Back-side Contacts(Intel似乎将其译作了背面触点)的技术;还有一项突破是在一片300mm晶圆上,实现硅晶体管与GaN(氮化镓)晶体管的融合,所以叫GaN-on-Silicon wafer,今年展示了把Si CMOS驱动和GaN功率晶体管放到一起的DrGaN。

我们来逐个看一看,虽然Intel方面一直强调并不对这些技术未来的商用做任何评论;但说不定几年以后就会在实际的芯片产品上看得到。

芯片背面供电有新方案

Intel在某些宣传资料中把backside power delivery直接翻译成芯片背面供电。感觉这个翻译非常直白和清晰,业界还有诸如晶背供电、背晶供电之类的翻译,看起来多少就有那么点令人费解了。

BSPDN的概念最早应该是2019年由Imec引入的,这两年的很多重要会议上,Intel也很热衷于去谈自家在BSPDN技术上的研究——这项技术自然也是另外两家foundry厂争夺技术高地的热点。

在Intel的计划里,离现在已经不怎么遥远的Intel 20A工艺就要用上芯片背面供电技术——Intel称其为PowerVia,会比台积电和三星更早,像台积电计划中的初代N2工艺还不会用上BSPDN。

一般的芯片制造流程,是先搞定最底下的晶体管和器件,然后开始往上“垒”——晶体管是需要金属线做互联和供电才能工作的。现在的高性能处理器,在晶体管往上,一般都会有十几层金属层。在靠上的层级,供电的电源布线也是其中的组成部分。这就是常规的正面供电方案:供电与信号互联线路都在同一侧。

金属层很多的时候,互联和供电可能都需要走很远才能到达晶体管,IR压降也是个问题,而且信号和供电这两者间可能还会产生干扰;当然更重要的是,如果设计非常复杂,设计和工艺技术要考虑的工程问题会更多,也就影响到了芯片面积的有效利用。

所谓的backside power delivery是把供电轨从原本wafer/die的正面,移到背面去,实现供电和IO信号互联较大程度的分离。供电和信号互联可以分别优化,而且各自都有了更大的空间,也能降低工艺的复杂度和成本......有关这种技术具体的好处,此前我们也特别撰文聊过,这里就不再赘述了。

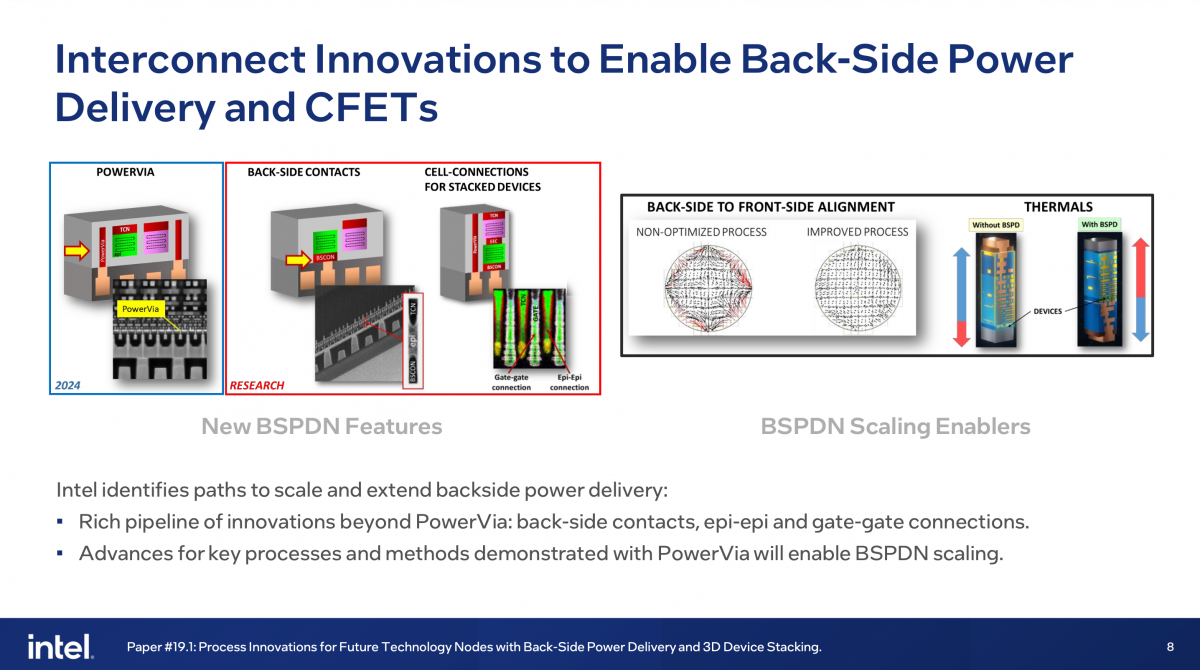

一般我们说Intel家的BSPDN技术名为PowerVia。不过这里可能需要考虑两层含义,第一是如果“PowerVia”作为BSPDN技术的品牌名,则其表征的是整体技术称谓;但从今年IEDM的技术介绍来看,PowerVia有时可能并不是指整体的背面供电技术,而是特指一种TSV(硅过孔,through-silicon via)。这就要看将来Intel市场部如何定义这个问题了。

Via通常意义上是指某种能够让电信号贯穿半导体器件不同层之间的垂直通道,这应该也是初期PowerVia的核心技术点。之前我们就在文章里提过PowerVia技术所用的nano TSV,相比于一般的BSPDN电源轨还是有所不同的,供电更直接。

IEDM 2023上,Intel引入了一种名为Back-side Contacts的方案,具体如上图所示——它和PowerVia不一样。这张图最左边展示了即将要在明年量产的PowerVia——从TEM图中是可以看到器件层两侧的互联,中间有个垂直连接的部分令两侧实现互联——这个部分就是很具体的PowerVia了。

而Back-side Contacts或者说背面触点,是BSPDN技术的进一步延伸和改良。上图红框展示了这项技术,Intel说有需要的话,这种技术支持从上面、下面,或者从上下两侧同时连接到晶体管。Intel表示Back-side Contacts可以和PowerVia一起用,也可以单独用——后文谈3D晶体管的部分就会看到两者同时上场。

Intel形容Back-side Contacts技术展示的TEM图看起来很“对称”——上面和下面的Back-side Contact差不多,而且“不只是几何上的对称,电特性(electrical behavior)也是相称的”。

“这么做有不少好处。现在我们可以从背面,直接为器件供电,从大型线路(large wires,应该是指线宽较宽的金属层)直接到器件,而不需要先绕过器件(go around the devices)。”这里所说的“绕过器件”是PowerVia方案决定的供电线路结构,上面这张PPT的3D结构图中已经展示了PowerVia贯穿到晶体管上方,至TCN(top side trench contact)触点的位置;而Back-side Contact背面触点显然就直接连接了器件。所以相比于PowerVia,新成果Back-side Contact可以获得更好的性能红利。

而且因为Back-side Contact本身不再使用PowerVia,“意味着每个cell单元更少的金属、更少的电容、更快的开关速度和更低的功耗”;“因为不再需要为PowerVia保留位置,其他组成部分可以靠得更近,也就节约了面积,单位面积内可以塞进更多的器件。”所以Intel总结说,Back-side Contacts不仅保留了PowerVia此前带来的所有益处,而且相比于PowerVia,在PPA三方面都有优势。答记者问环节,Intel发言人似乎大略提到了,Back-side Contact对于性能的提升在4.5-8.5%左右,而且有面积方面的更多红利。

不过在媒体会上,Intel并未详述所谓的Back-side Contact具体是如何实施的,技术难点在哪儿。对这部分感兴趣的读者可以去看一看本次Intel就这一议题发布的paper(#19.1, 题为"Process Innovations for Future Technology Nodes with Back-Side Power Delivery and 3D Device Stacking")。

有关背面触点技术,其着眼未来的根本,恐怕还在于,它能够为CFET服务,也就是3D堆叠的晶体管结构——有关CFET,下文将会做进一步的阐述。简单来说,CFET是把pMOS和nMOS在垂直方向上叠起来,这也是过去这些年尖端制造工艺研究的热点技术。

从直觉来看,如果晶体管叠起来,对互联拓普而言自然也就造成了更大的麻烦:因为对于上层器件和下层器件,都必须提供供电和信号连接。Intel认为,PowerVia和Back-side Contacts在此可以发挥很大的作用,实现高效的器件堆叠。另外就3D堆叠晶体管的问题,互联相关的问题还涉及到栅极、源极等组成部分,也需要新的垂直互联——位于单元内部(gate-gate connection, epi-epi connection),Intel表示也已经实现了这部分连接方案。

而高效的互联才是更进一步确保CFET带来面积利用率提升的基础。前面提到的包括PowerVia, Backside Contacts, epi-epi连接与gate-gate连接,可能都会成为未来3D堆叠晶体管最终落地的组成部分。

这部分最后值得一提的是,这张PPT还有一部分内容下标“BSPDN scaling enabler”,也是Components Research在研究的部分。就是为了配合器件微缩和结构改良,所做的配套跟进。比如说在芯片背面供电实现上,要在前面和背面的对齐问题上做工艺的精进,实现正反两侧特性的重合;此外还有散热方面的,Intel表示在相同功率密度的情况下,自家的BSPDN技术表现出的热行为与响应,和没有采用BSPDN技术的方案基本一致,也就是说Back-side Contact不会影响到热行为。

3D堆叠的晶体管,也用背面供电

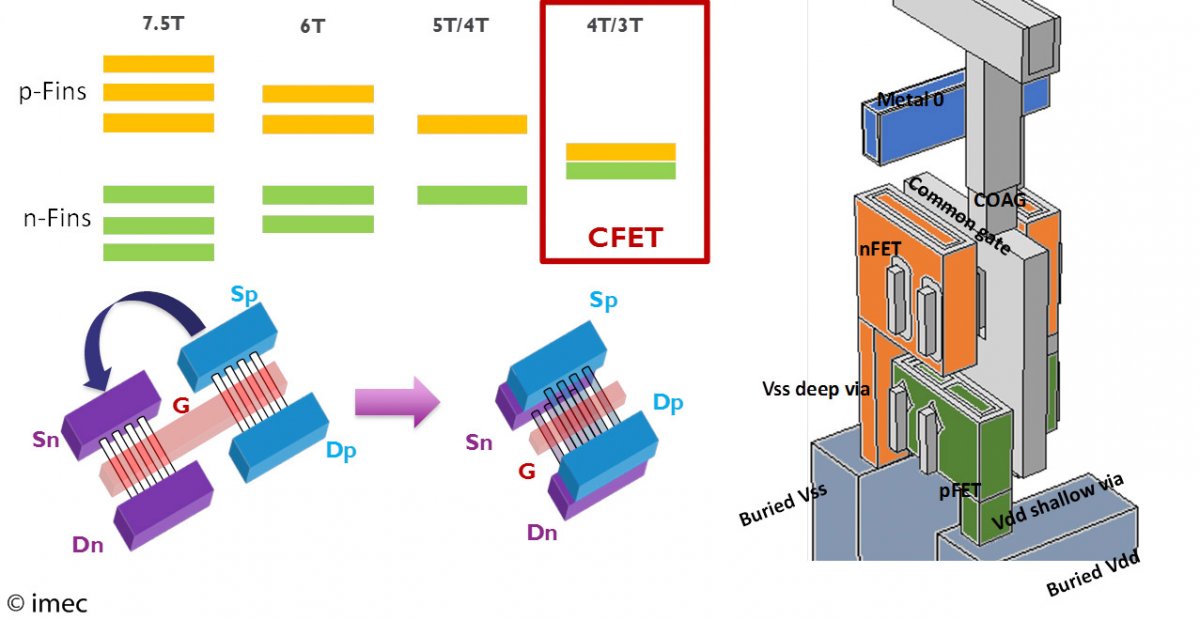

对尖端制造工艺未来走向有关注的读者普遍都知道,FinFET之后的器件结构走向是GAAFET,而在此之后的走向可能包括了基于GAA的Forksheet FET,以及更加未来向的CFET(complementary-FET)——前文也已经提到了。

我们在去年的文章里解释过,CFET是一种cell单元或block层面的结构变化,将nFET堆叠到pFET上面——形成了所谓晶体管的3D结构,之前Imec称其为sheet-on-sheet。从下面的结构示意图很容易理解,这个过程就像是把原先水平方向放置的nMOS折叠到了pMOS上。

这是行业对于晶体管、单元结构变化的共同预期。因为折叠让cell单元的占die面积缩小了,逻辑单元缩减大概有30-50%;而且单元之间的连接走向也更有弹性。很显然CFET是推进摩尔定律很重要的技术方向,也是不同科研机构、企业研究的方向。在2021年的IEDM上,Intel曾首度展示过这种器件堆叠成果,Intel称其为3D monolithic CFET器件。

当时Intel公布的器件实现成果,是把3个nFET nanoribbon(也就是GAA的nanosheet)叠到3个pFET nanoribbon上面,垂直距离间隔30nm。偏实用性的成果展示,是做了一个gate pitch(栅极间距)60nm的inverter(也就是用于做NOT操作的非门),据说是整个行业内的首次实现。

如前文所述,今年Intel公开有关CFET的成果主要就集中在背面供电的融合上。IEDM上发布的这份paper题为"Demonstration of a Stacked CMOS Inverter at 60nm Gate Pitch with Power Via and Direct Backside Device Contacts". 看这个标题,其实基于堆叠晶体管的、60nm栅极间距的inverter去年就做出来了,这次的关键是用上了PowerVia和Backside Contact。

因为传统基于前面供电(Front-side)方案还是需要同时有单独的、大的触点(contact)来连上面和下面的晶体管——这肯定不是一个优雅的方案。而且媒体会上,Intel也提到说这种前面供电的方案“需要额外的触点,像图中Vcc标注位置的触点,而且还离gate栅极比较远”。“原本CFET是为了获得空间上的红利,现在则会被这样的问题给对冲掉。”也就浪费了CFET器件结构革新的良苦用心。

右边的结构图展示的就是3D堆叠器件,pMOS在下,nMOS在上。有关如何沉积源极、漏极触点之类的问题,都是需要在制造的时候解决的,“pEPI(pMOS上的epi)在下面,材料用的是锗化硅;nEPI在上面,用的是硅。还需要对gate栅极做相同的操作,以垂直的方式单独做沉积,p-WFP和n-WFP(work-function metal)按需达到阈值电压。”

听Intel发言人的讲解,应该是Back-side Contact和位于底部的器件直接连接,而PowerVia给叠在上面的器件供电,图上也是这么标注的。此外,这张图还标了一个WAC(wrap around contact),据说是某些时候需要用到的contact,inverter内部的节点连接。“我们将nEPI与pEPI放到同一个track上,而不需要再用别的一些方案来连接。”

Intel说,上面所说的这些构成多少也可以从左边倒置的TEM图里看出来,BSCON(Back-side Contact)在这张图中是在上面的。(虽然我们完全看不出来...)

作为已经造出来60nm CPP间距的inverter(非门电路就包含一个nMOS和1个pMOS),PPT也展示了其电压转换曲线,和FinFET、GAAFET还是很接近的。

把GaN和Si CMOS放一起

到这里可以稍微做个小结了,上述两项研究成果本质上的确都是对摩尔定律延续的努力。CFET本身就是通过器件和单元结构革新来提升单位面积内的器件数量——3D堆叠晶体管也不是封装层面的,实打实的就是摩尔定律进步本身的议题。

而芯片背面供电——这个话题就是基于半导体制造工艺改良,来缩减成本、提高效率、提升性能。今年Intel是提出了一种不同于PowerVia的新方案。与此同时背面供电还能应用到CFET上,用Intel的话来讲,是不能让CFET堆叠晶体管辛辛苦苦得到的面积红利,又浪费在了供电复杂性上,所以需要背面供电加持来提升效率。

思路还是环环相扣的,虽然像Intel在会上呈现的inverter最终产品化其实仍然需要很多工作,但我们倒是感觉上述技术产品化的希望很大。另外从Intel的新闻稿来看,今年IEDM上,Intel还提到了2D材料(TMD,过渡金属硫化物),作为沟道(channel)材料能够进一步缩减gate length;据说是展示了全球首个GAA 2D TMD PMOS晶体管,全球首个300mm晶圆生产的2D晶体管。2D材料也是半导体制造的前沿研究课题;而2D材料研究本身,对于CFET的发展应该也是有帮助的。

本文最后,再谈一个Intel在媒体会上特别提起,但篇幅并不是很多的DrGaN,看GaN就知道是电源领域相关的研究,不过Intel在这部分注意力主要是放在了低压领域(<48V)。

去年IEDM上,Intel曾展示过自家GaN晶体管的功率品质因数FoM达成相比于业界标准GaN(pGaN HEMT)和硅LDMOS大约20倍的领先。当时Intel就展示了300mm GaN-on-Silicon工艺,在具体的规格数据上还挺有看点——当时我们没怎么报道。似乎在器件结构上就栅极沟道区域用了MOS(high-k based oxide),所以Intel说它也可以被称作“MOS-HEMT”。我们没有具体去研究Intel的GaN晶体管结构和材料,但应当与业界主流方案是不大一样的。

值得一提的是Intel展示的3D monolithic integration技术主要基于所谓的“layer transfer”来实现,应该也是一种多层堆叠、键合相关的技术,看“GaN-on-Silicon”这个名字就差不多能猜到。

今年展示的具体是将GaN晶体管和硅CMOS做融合——当然也是在GaN-on-Silicon平台,所以这里的“融合”“集成”程度就比较高了。所谓的DrGaN,这里的Dr是指驱动——驱动与开关在一片die上。Intel方面表示这是业界首个将Si CMOS驱动与GaN功率晶体管做整合的技术。

这张PPT上还展示了此前的一些历史,包括2004年Intel推DrMOS,将硅基CMOS驱动与硅基功率器件做整合,实现了更高的密度、更大程度避免寄生效应——现在DrMOS在PC、数据中心等领域应该算是很常见的了(虽然似乎DrMOS的集成度似乎和DrGaN并不是一个水平)。

DrGaN应该是这一思路的延续,达成GaN功率电子的效率、功率密度等的提升,也算是个未来向的前瞻性技术。答记者问环节,Intel被问及于最终DCDC或者降压变换器之类的应用上,DrGaN能带来多大程度的收益,Intel的回答是这项研究产品化也仍然需要很多后续的工作,不过似乎这项技术“正面临破冰”。有兴趣的读者可以去看一看IEDM上发的paper,paper标题列在最后这一页PPT上——前面提到的几个技术发布重点和2D材料亦有列出:

- 很难的,这都是最前沿的部分了,国内半导体公司没有像intel三星这样有钱和实力玩得起的,另一方面光刻机也是问题,intel已经有highNA EUV了 国内EUV根本买不到

- 可以看一下 IEDM 每年发 paper 的一些清单,国内貌似主要是一些科研院所,比如 2D 材料,国内就有在研究的

- 国内有没有玩这个的,特别是上市公司