继2022年11月发布EnFortius®凝锋®系列第一款低功耗设计验证工具(Low Power Checker, LPC),2023年4月发布第二款数字电路门级功耗静态分析工具(Gate-level Power Analyzer, GPA)之后,11月,英诺达推出了一年内的第三款低功耗工具——RTL级功耗分析工具(RPA),向业界展示了公司持续深耕功耗优化之路的决心和实力。

低功耗设计,下一个IC设计创新的突破点

如何降低功耗目前已经成为半导体产业的热点问题。

从大环境来看,过去的40年里,世界人口总数从40亿增长至75亿。但与此同时,全球用电量的速度却从40年前的6000特瓦时增加到现在的24000特瓦时,这意味着每人所消耗的电量在过去40年中平均增加了两倍,远远高于人口增长速度。毫无疑问,这一趋势跟我们40年内消费习惯、生活习惯的改变有着密不可分的关系,最具代表性的应用新能源汽车的大量涌现,极大带动了二次能源的使用量。

人与人之间交流方式的改变也对此产生了重要的影响。贝尔先生发明电话的时候,使用很少的电量就可以维持长距离通信,但对比之下,现在的移动电话完成同样距离通信所消耗的单位能量发生了显著提升。如果再考虑AI、5G、机器学习、智能驾驶、大数据处理这些新兴技术对电量和能量密度的需求,电气化发展的速度实在是令人感到惊叹。

于是,对芯片设计公司或制造商来说,在保证芯片性能的情况下,尽可能做到低碳、节能和环保,成为了企业发展的必选项。

但一个无法忽视的问题是,当IC设计的规模越来越大,功能和复杂度越来越高时,不断增加的功耗密度,成为了阻碍高性能芯片开发的一道壁垒。AMD CEO Lisa Su在ISSCC 2023上就曾指出,“超级电脑的算力可以每1.2年就翻倍,但是能耗效率的进展却是每2.2 年才能够翻倍”,“现在要让半导体的算力增加的最大瓶颈,其实不是算力本身而是能耗效率”。

为了应对这些挑战,设计工程师们运用了各种先进的低功率设计技巧,业界也推出了IEEE 1801标准(UPF)来描述功耗设计意图,该标准定义了从RTL到GDS全流程的低功耗管理设计意图,帮助功耗的优化以及相关的设计验证与实现。

对中国半导体产业来说,通过先进的制程工艺和EDA工具来提高芯片性能,不断提升能耗效率,肯定是一条康庄大道。但如果因为一些特定的原因使得我们无法再去使用它们来获得高水平设计时,能否通过扎实的技术功底和宽厚的设计经验,找到另外一些有效提升产品竞争力的途径?既是挑战也是机遇。而这其中,低功耗设计工具配合创新的架构和设计方法学,就被业界普遍看好。

早期功耗分析的重要性与挑战

不论是先进工艺IC设计还是成熟节点IC设计,在芯片设计全流程中,持续追踪、获取准确的功耗数据对设计团队是至关重要的,这不仅意味着功耗水平在设计中的各个抽象阶段(RTL级、门级)和层级(SoC级、Block级)是透明、可控的,驱动设计团队做出更好的设计决策。同时,通过对功耗的持续管理和优化,还可以提高设计效率、节省因功耗而产生的迭代成本。

尤其在IC设计阶段的早期(RTL阶段),对功耗进行准确且一致的评估分析,为芯片的设计提出修改建议,功耗设计优化的效果是最好的。因为这个阶段抽象层级高,修改的灵活度也更高。换句话说,越早介入,优化手段越多,收益越大;越早介入,能越早反馈,快速迭代,从而节省时间和成本。反之,越是在后期,优化的空间也就越小,长期以来的实践已经证明,在低抽象级别比在高级抽象级别降低功耗更加困难。因此,在RTL阶段需要重复执行功耗估算,并针对不同的设计架构进行功耗比较,以最终评估并提高设计的能耗效率。

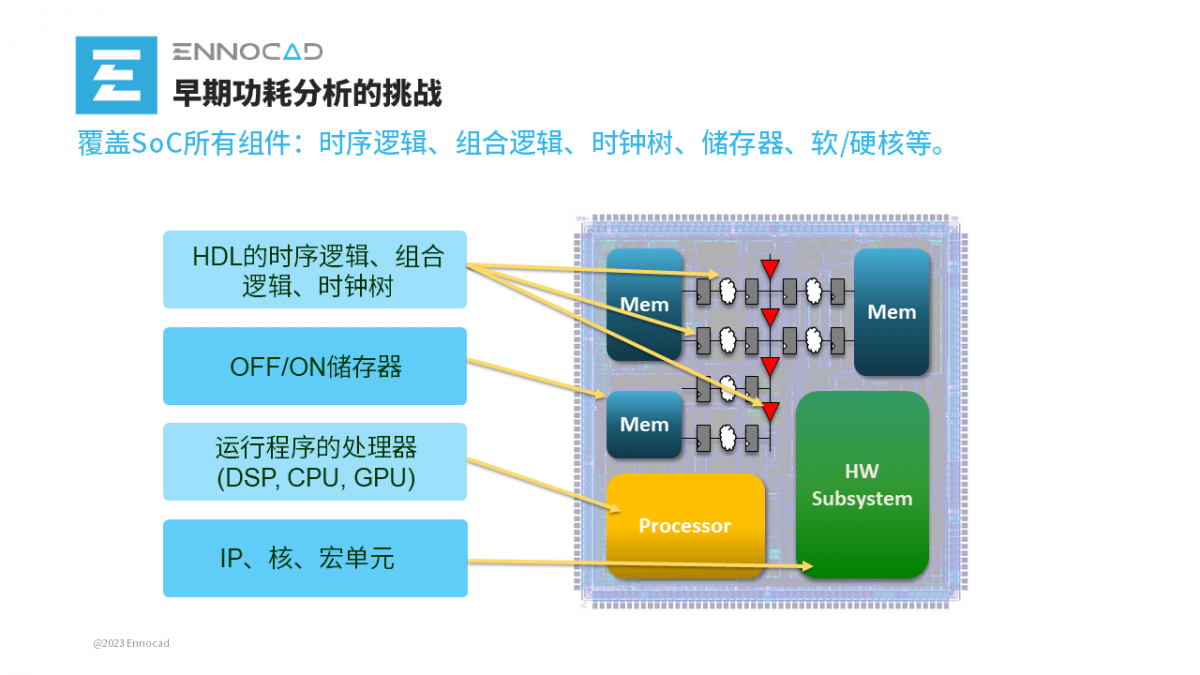

另一方面,要知道大部分SoC设计不是在晶体管级别上进行的,而是在寄存器传输级别(RTL)上进行的,或者是使用通用功能的单元库合成的更高级别的代码。这其中包含许多“低功耗”单元库,设计师可以利用逻辑合成工具快速测试多种单元库的组合,以满足PPA目标。功耗会影响芯片的电源完整性和热特性,因此必须在物理设计阶段就解决这些问题,并在signoff期间进行确认。

但是,在这个过程中,由于没有经过逻辑综合,缺少物理信息等重要的数据,要准确对功耗进行预估是非常困难的。设计团队需要仿真数据,工艺库文件以及其他参考数据才能一步步接近真实的功耗,所以设计团队需要一套先进的工具和设计流程,以在早期获得准确的功耗数据。

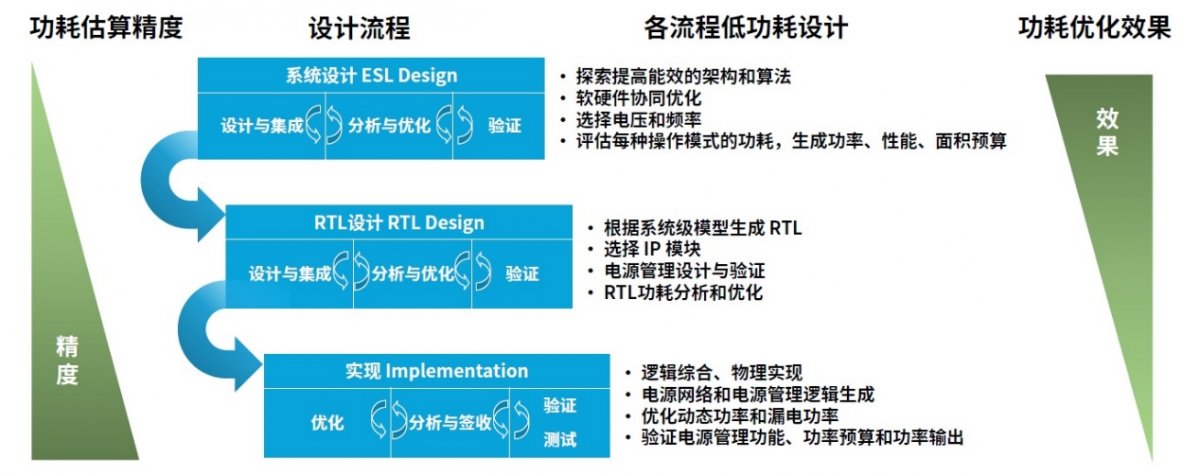

如果从整个流程看,越早考虑功耗收益越大,但是估算精度往往不够精确。到了设计流程后期,特别是物理实现之后,功耗的估算会更精确,但此时可采用的功耗优化方法与优化的程度又都比较有限。

因此,目前在该领域存在“优化效率与估算精度难两全”的困境。对功耗静态分析而言,尽管设计流程早期的功耗估算考虑到了时钟树、关键IP的建模、CPU/GPU/APU的广泛使用、复杂macro IP等因素,但也还要考虑到后端物理实现的影响。这种情况下,芯片工程师需要全面的低功耗设计解决方案,包括兼具速度与精度的功耗分析工具。

英诺达早期功耗分析的EDA解决方案

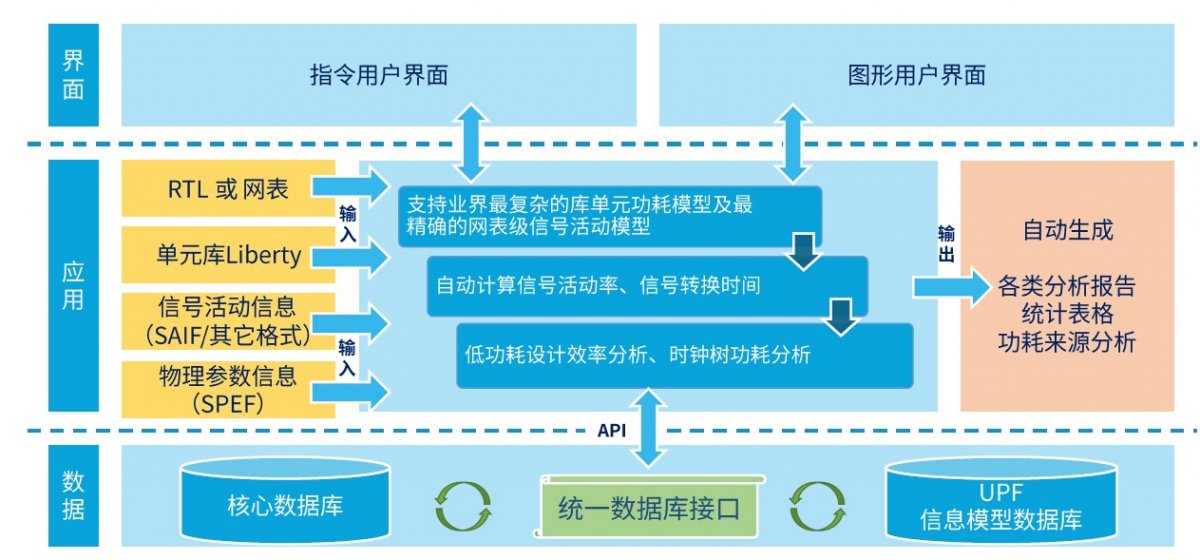

英诺达EnFortius® RPA静态分析工具正是为了解决上述挑战而生的,主要是用于估算RTL阶段IC功耗,可以帮助用户在设计早期获取准确的功耗数据,找到设计中的功耗热点,优化电源管理策略,从而降低电路功耗。该款工具支持行业标准输入文件,包括System Verilog、提供工艺库单元数据的Liberty文件、提供信号活动信息的SAIF/FSDB文件、以及提供寄生参数信息的SPEF文件。

而为了进一步提高功耗估算的准确性,EnFortius® RPA采用了英诺达自主开发的创新高效数据和算法架构;高效逻辑综合、门控综合与时钟树综合引擎与物理线网模型,既能够在面对超大规模设计(等效逻辑门过亿)时快速完成功耗计算,也可以通过参考设计的现有物理数据完成更准确的线网电容估算。

同时,EnFortius® RPA还实现了四个“支持”:

- 支持单元库标准Liberty中各类常用的功耗模型,包括状态相关漏电功耗模型(state-dependent leakage power model)和状态及路径相关内部功耗模型(state dependent-path-dependent internal power model);

- 支持业界标准信号活动文件(SAIF)中各种信号活动率信息,包括状态相关信号活动模型(state-dependent switching activity model);

- 支持具有不同电压的多电压域功耗分析;

- 支持各类指标分析和报告,例如各逻辑层级和逻辑组的动态及静态功耗,时钟门控比(CGR)和时钟门控效率(CGE)等。

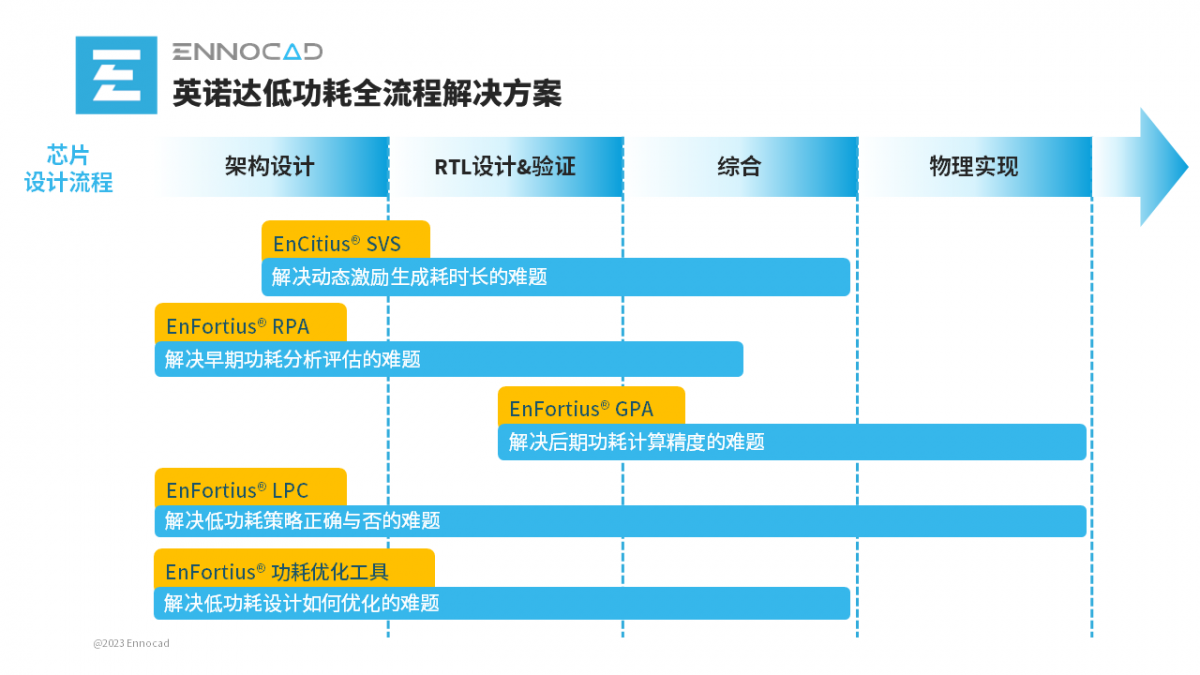

至此,英诺达实现了在设计全流程中低功耗管理、优化的初步方案。也就是说,在低功耗设计策略方面,英诺达的EnFortius® LPC可以在设计的全流程对电源的管理意图的正确性进行检查;而为了解决“优化效率与估算精度难两全”的难题,EnFortius®RPA和门级功耗分析工具(GPA)通过输入设计、信息活动信号和物理参数等文件,既可以实现早期对功耗数据的估算、了解功耗的整体趋势,也可以在设计后期掌握精准的功耗数据。

而这其中,最主要的信号活动文件的来源则由英诺达的EnCitius®曜奇®SVS的硬件仿真加速器来提供,二者相互配合,可以实现对设计的快速迭代。除此之外,英诺达正在开发的功耗优化工具可以通过以上工具的分析评估结果,在早期对功耗进行系统及全面地优化。

结语

从低功耗设计验证工具LPC,到门级功耗静态分析工具GPA,再到RTL级功耗分析工具RPA,英诺达在低功耗设计EDA工具道路上一年内连迈三大步,书写着本土EDA一次又一次的创新突破。展望未来,考虑到PPA的总体目标不能仅仅集中在功耗上,行业更期待英诺达能继续提供端到端的全流程低功耗解决方案来提高能耗效率,帮助用户推出更有竞争力的IC产品。