将开关、电阻器和MOSFET并联连接的目的是分担功率,并创建能够承受更大功率的器件。可以将它们并联连接,以增加输出电流的容量。相对于其他旧款设计,因为并联连接不受热波动性的影响,因而通常显得更简单、更稳定。实际上,碳化硅MOSFET也可以与同类器件并联使用。几个单元之间通过简单并联连接后,在正常条件下工作都不会有问题,但在特殊情况(与温度、电流和工作频率相关)下,器件的工作条件可能会变得极为严苛。因此,必须采取一些预防措施,创建故障预防电路,以便能够充分利用功率器件并联所带来的优势。

需要记住的几件事

在实践中,当功率器件具有相同电气特性以及相同静态和动态行为时,其并联连接是可能的。但现实中,因为各器件之间总是存在一些差异,故要求器件之间完全相同是不切实际的。

在少数应用中,MOSFET才会工作在静态状态下,并充当“慢速”电子开关。而在大多数应用中,涉及的都是高频率连续开关操作。即便是同一型号的多个MOSFET之间的电气特性差异很小(甚至难以察觉),也会引发瞬时电压尖峰以及电流分布的总体失衡。这个问题可能会导致高功耗,引起电路发热严重,最终导致电子元器件损坏。

因此,设计师必须研究电路,以便在所有工作条件下,使传输电流在相同性质的所有功率器件上都是平衡和均匀分布的。在开关切换时,应避免电流集中在某些电子元器件上。事实上,这种非理想并联可能会导致有害的自激振荡以及电子开关操作失衡。

一般来说,非理想并联所产生的问题和原因包括如下:

·设备的参数彼此不一致

·导通电阻(RDS(on))失配

·栅源电压(VGS)失配

·栅极驱动器失配

·电源电路中的失配

导通电阻

RDS(On)是MOSFET的基本参数之一。该参数影响许多工作指标,如元件损耗、最大传输电流、系统效率和传导损耗。当MOSFET关断时,没有电流流动,此时漏-源电压较高。反之,当MOSFET处于激活导通状态时,其漏-源电压会下降到几百毫伏。

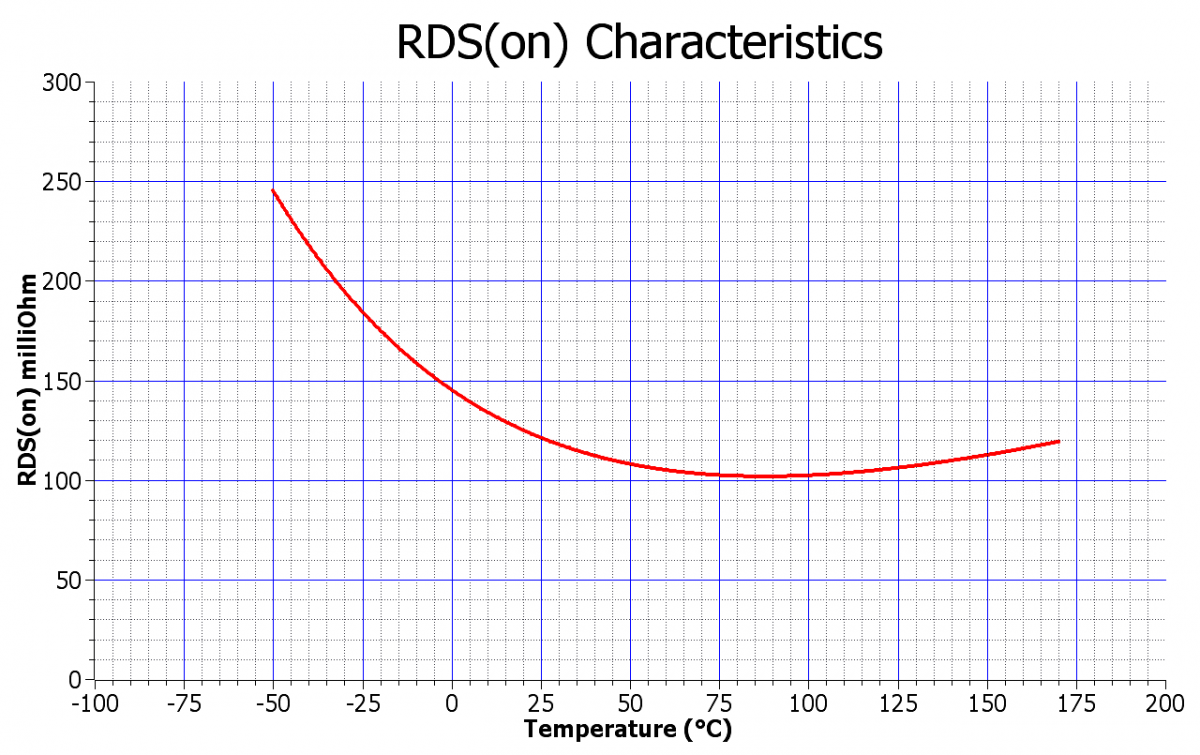

SiC MOSFET的RDS(on)参数对温度非常敏感,因此在设计具有并联器件的电路时,必须非常谨慎(见图1中的图表)。其内部构造决定了负温度系数和正温度系数,因此可能引发电流失衡。图1表明,随着SiC MOSFET的结温不同,沟道的电阻会发生变化。许多示例中的器件简单并联时都会产生问题,因为一个器件可能比另一个器件承受了更大的电流。因此,必需使所有MOSFET的热量耗散均匀。

图1:导通电阻与结温的关系。

各种失衡

当MOSFET开路时,一个小电流并联通过电子开关,电流的大小与开关的开启电阻成反比。显然,电阻最低的器件将传输最大的电流。

幸运的是,SiC MOSFET的特点是正温度补偿,因此电路中会出现自然平衡,从而将元件的热破坏限制在最低限度。

另一方面,MOSFET内部的二极管行为也相反,当传输电流减小时,温度反而升高。电流失衡可能发生在转换期间,特别是在电源接通和断开瞬间。

有害自激振荡

振荡自激是高频信号,将会改变元器件的正常功能。事实上,MOSFET的特殊构造构成了一个谐振电路,包括有电容(C)和电感(L)。显然这两个元件都是寄生元件。如果没有外部栅极电阻,谐振电路将具有非常高的Q因子。

如果发生谐振,在“栅极”和“源极”之间会产生一个颇具影响的振荡信号,从而导致与其一致的寄生振荡和有害自激的产生。过高的振荡电压可能导致MOSFET误开启或误关断。不过一般来说,SiC MOSFET并联连接时的振荡风险并不高,因此,只要采取必要的预防措施,电路就可以毫无问题地正常工作。

解决方案

如今,许多制造商通过将几个MOSFET并联连接来制作SiC功率模块。当然,制造过程中也采取了一些预防措施。有些制造商制作的组件功能非常强大,因为在这种类型的连接中,耗散功率增加了,最重要的是,RDS(on)参数值降低了,这与电阻器并联连接时发生的情况是一样的。

一般来说,SiC MOSFET可以在没有特殊措施的情况下并联连接,因为过热时,内阻会提高,从而使负载分布趋于均匀,尽管各个部件存在固有差异。不过也有一个明显的缺点,就是“栅极”电容容量会增加,这导致SiC MOSFET的导通时间增加。此时,栅极电流将会大幅增加,具体还取决于并联器件的数量。在高频情况下,这一事实可能会变得不可接受。对于老式的功率器件(例如IGBT)来说,虽然设计师必须克服恒有的挑战(包括平衡、大电流驱动器等),才能在功率器件之间实现良好的并联连接。但采用SiC MOSFET时,由于开关频率要高得多,这类的挑战可能会增加。

另外,设计师还需要研究PCB布局。布局结构应该对称,以分散所产生的热量,并大幅减少寄生电感。

上述所有这些都是SiC MOSFET并联连接时的正确解决方案,目的都是增加传输电流和功率电平。

但是,仍需要注意以下几点:

·产生阈值电压的电流可能出现失衡

·由于寄生电感不对称,可能出现电流失衡

·可能出现波动

如今,一些制造商的制造完美度已经达到了相当高度,并制造出了几乎完全相同的SiC MOSFET组件,出现失衡的可能性很小。然而,阈值较低的器件具有较高的瞬态效应,因此开关和导通损耗也较高,最终导致总功耗较高。通常,如果负载电流大于所选用单个器件的标称值,则可以将两个器件安全地并联使用,以将流过每个开关的电流减半。

图2显示了一种解决方案,该解决方案中采用了一个外部栅极电阻器(每个MOSFET采用一个),以减少各种器件之间切换时所产生的变化。不过,采用外部栅极电阻器并非万能,这种失衡可能仍然存在。有时候,在这种并联配置中,由于两个MOSFET之间存在RLC谐振电路,VGS也可能会产生振荡自激。

图2:两个SiC MOSFET并联连接的驱动电路。

(参考原文:power-design-tutorial-more-power-with-sic-mosfets-connected-in-parallel)

本文为《电子工程专辑》2023年11月刊杂志文章,版权所有,禁止转载。点击申请免费杂志订阅